这里主要介绍ITS所产生的LPI中断的虚拟化。首先对ITS寄存器映射作简要介绍。

1 ITS寄存器映射

ITS地址映射包含两个分开的64KB,该地址由ITS_base指定。基地址必须64KB对齐,这两个包含:

- control寄存器,地址位于ITS_base + 0x000000

- 中断转换空间,地址位于ITS_base + 0x010000

- vSGI空间,地址位于ITS_base + 0x020000

下表为GIC寄存器映射。

| 序号 | 类型 | 描述 |

| GITS_CTLR | RW | ITS控制寄存器 |

| GITS_IIDR | RO | ITS ID寄存器 |

| GITS_TYPER | RO | ITS Type寄存器 |

| GITS_MPAMIDR | RO | ITS支持MPAM大小 |

| GITS_PARTIDR | RW | ITS PARTID寄存器 |

| GITS_MPIDR | RO | ITS亲和性 |

| GITS_STATUSR | RW | ITS错误报告状态寄存器 |

| GITS_UMSIR | RO | ITS未映射MSI寄存器 |

| GITS_CBASER | RW | ITS命令队列描述符 |

| GITS_CWRITE | RW | ITS写寄存器 |

| GITS_CREADR | RW | ITS读寄存器 |

| GITS_BASER<n> | RW | ITS转换表描述符 |

| GITS_TRANSLATER | WO | ITS转换寄存器 |

| GITS_SGIR | WO | vSGI寄存器 |

2 ITS设备的模拟概述

ITS设备的模拟包含两个部分,一部分在QEMU中,一部分在内核KVM模块中。QEMU中会模拟ITS设备,让guest中能够识别到ITS设备;另一部分在内核KVM中对于ITS MMIO等模拟。

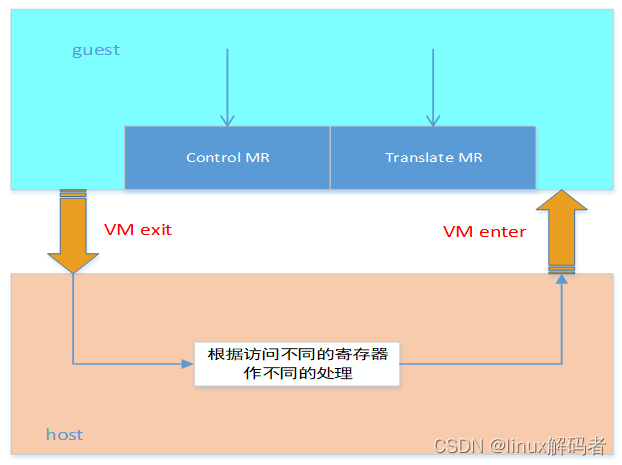

在guest中访问ITS设备寄存器所对应的MR时,会触发VM exit进入到host中,在host KVM中会根据访问不同的寄存器作不同的处理,完成MMIO处理后最终再次VM enter进入guest。

3 GICv3中LPI中断的处理

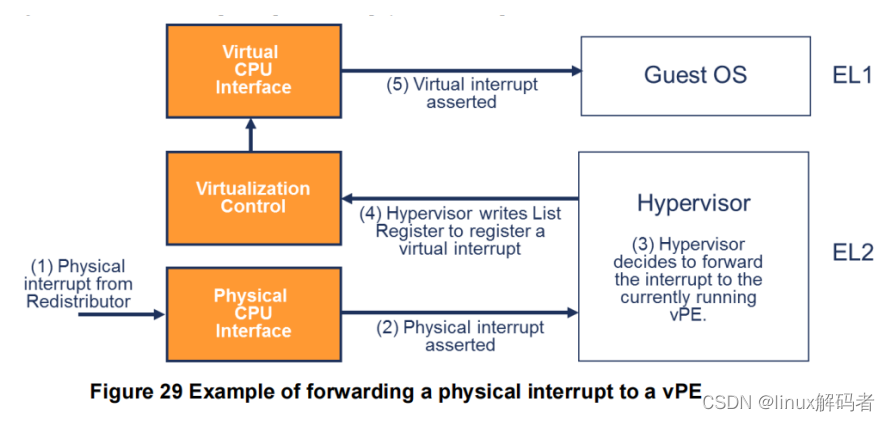

GICv3支持对LPI中断的虚拟化。GICv3增加了GICH和VGICC来支持LPI中断的虚拟化。

- 一个物理非安全Group1中断发送给Redistributor的物理CPU interface;

- 物理CPU interface检查物理中断是否发送给PE。默认情况下该检查通过,发出物理中断;

- 中断被带到EL2。hypervisor读取IAR寄存器,返回物理INTID。因此该物理INTID变成active状态。Hypervisor决定当前中断是否直接发送给当前运行vPE。hypervisor将物理INTID写入到ICC_EOIR1_EL1,在ICC_CTLR_EL1.EOImode=1情况下,该行为仅发出priority drop而不会deactive物理中断;

- Hypervisor写LR寄存器将虚拟中断变成pending状态。LR寄存器指定了vINTID。Hypervisor发出异常到vPE;

- 虚拟CPU interface检查虚拟中断是否发送给vPE。这些检查与物理中断相同,除了使用ICV寄存器。在这种情况下,检查通过并发出虚拟中断;

- 虚拟异常被带到非安全EL1。当软件读IAR时,虚拟INTID返回且虚拟中断变成active状态;

- Guest OS处理中断。当它完成中断处理时,它写EOIR发出priority drop和deactivation。因为LR寄存器记录物理INTID,它将deactivate虚拟INTID和物理INTID。

4 GICv4中LPI中断的处理

GICv4支持对虚拟LPI中断的直接注入,即不需要陷入到EL2,直接由Redistributor产生虚拟中断。

- ITS使用DeviceID从Device Table中获取合适的entry,它用于找到使用的Interrupt Translation table;

- ITS使用EventID从ITT表中选择合适的entry,它要么返回物理INTID和collection ID,要么返回vINTID和vPE ID;

- ITS使用vPE ID选择vPE表中的entry,vPE表返回目标Redistributor和vPE的VPT;

- ITS将vINTID,door-bell中断以及目标Redistributor的VPT地址;

- Redistributor比较ITS的VPT地址和当前GICR_VPENDBASER,若匹配,表示vPE被调度,虚拟INTID被发送给虚拟CPU interface;若不匹配,表明vPE没有被调度,vINTID被设置为pending状态。如果提供door-bell中断,物理INTID被发送给物理CPU interface。

本文详细介绍了GICv3和GICv4中本地中断(LPI)的虚拟化处理。GICv3通过GICH和VGICC支持LPI中断,中断在物理和虚拟层面的传递涉及多个步骤,包括INTID的激活、转换和优先级管理。GICv4进一步优化,支持直接注入虚拟LPI中断,减少了虚拟化过程中的开销。内容涵盖了ITS(中断转换服务)的角色,以及在QEMU和内核KVM中的模拟实现。

本文详细介绍了GICv3和GICv4中本地中断(LPI)的虚拟化处理。GICv3通过GICH和VGICC支持LPI中断,中断在物理和虚拟层面的传递涉及多个步骤,包括INTID的激活、转换和优先级管理。GICv4进一步优化,支持直接注入虚拟LPI中断,减少了虚拟化过程中的开销。内容涵盖了ITS(中断转换服务)的角色,以及在QEMU和内核KVM中的模拟实现。

763

763

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?