VL5 位拆分与运算

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output [4:0]out,

output validout

);

//*************code***********//

reg [15:0] indata;

assign out=(sel==2'b00)?5'b0:(sel==2'b01)?(indata[3:0]+indata[7:4]):(sel==2'b10)?(indata[3:0]+indata[11:8]):(indata[2:0]+indata[15:12]);

assign validout=(sel==2'b00)?1'b0:1'b1;

always@(posedge clk or negedge rst) begin

if(!rst) begin

indata<=15'b0;

end else if(sel==2'b00) begin

indata<=d;

end

end

//*************code***********//

endmoduleVL6 多功能数据处理器

`timescale 1ns/1ns

module data_select(

input clk,

input rst_n,

input signed[7:0]a,

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

c<=9'b0;

end else begin

case(select)

2'b00: c<={a[7],a};

2'b01: c<={b[7],b};

2'b10: c<=a+b;

default:c<=a-b;

endcase

end

end

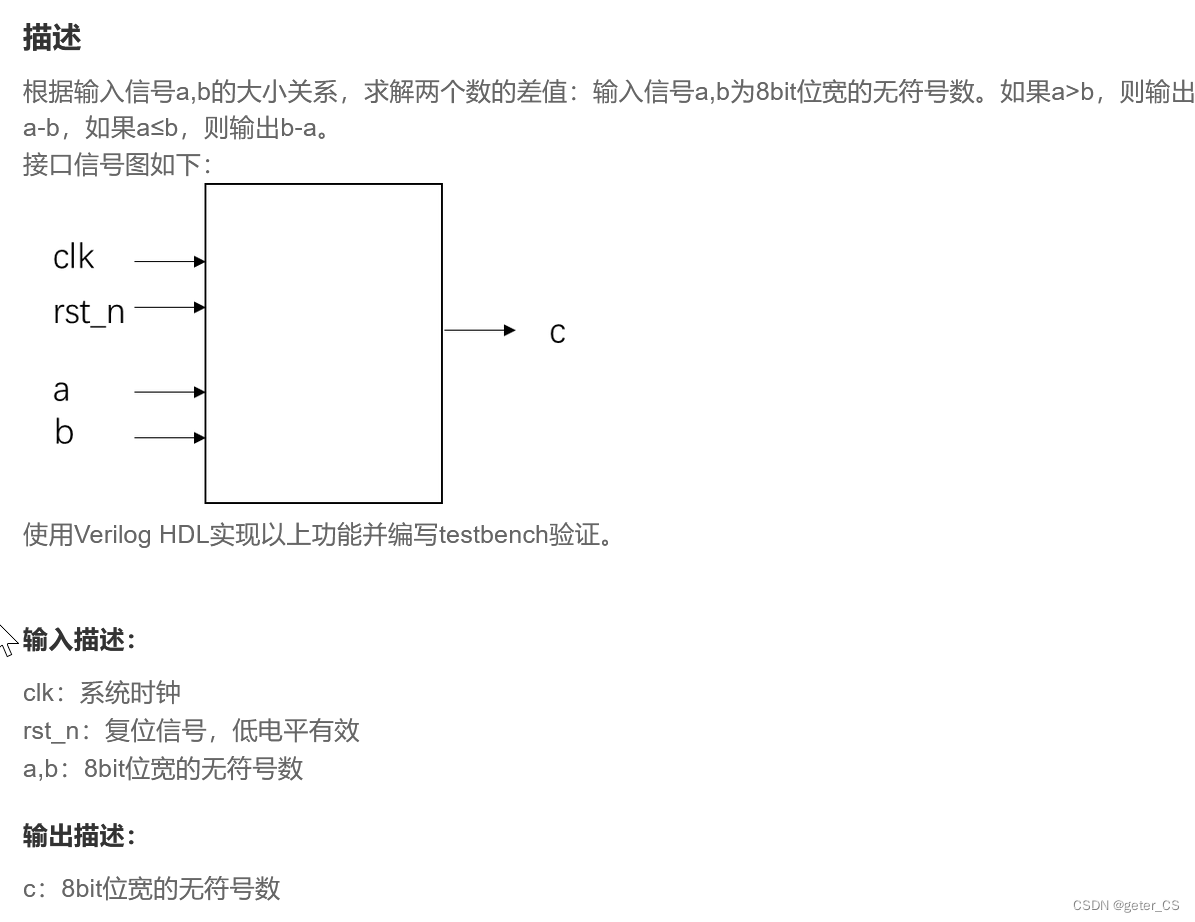

endmoduleVL7 求两个数的差值

`timescale 1ns/1ns

module data_minus(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

output reg [8:0]c

);

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

c<=9'b0;

end else begin

c<=a>b?(a-b):(b-a);

end

end

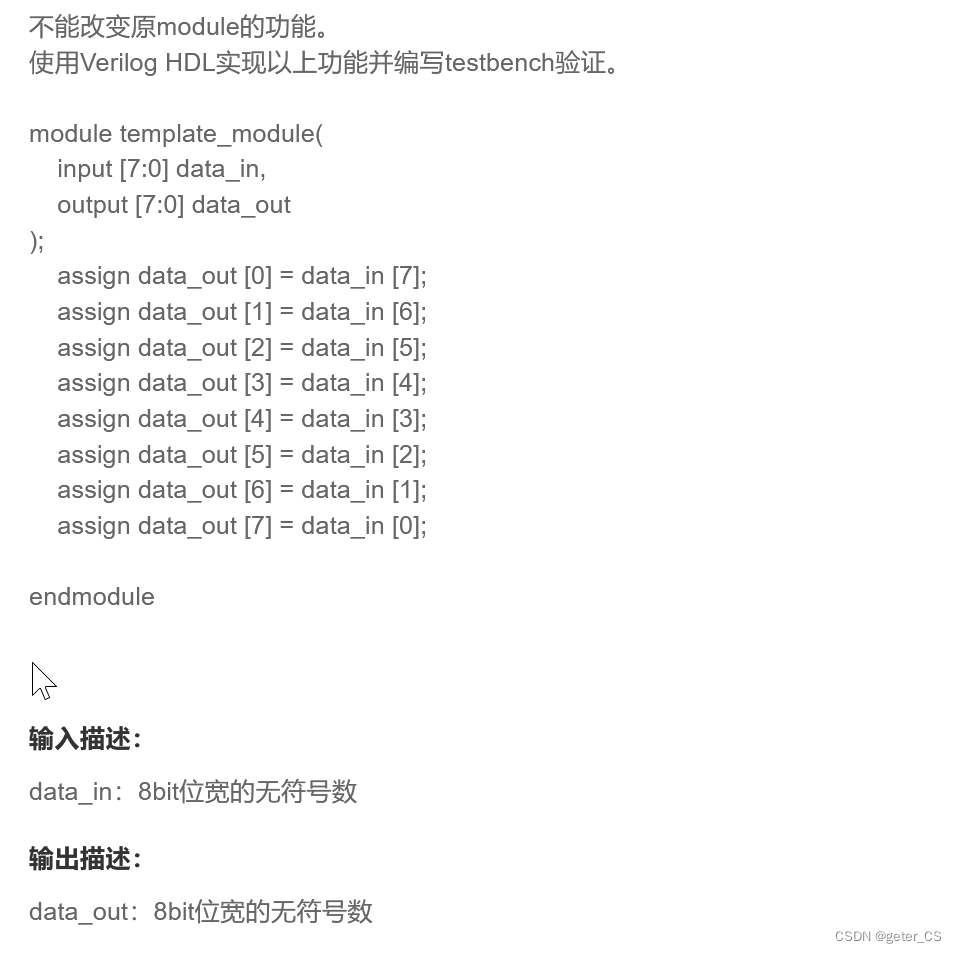

endmoduleVL8 使用generate…for语句简化代码

`timescale 1ns/1ns

module gen_for_module(

input [7:0] data_in,

output [7:0] data_out

);

genvar gen_i;

generate

for(gen_i=0;gen_i<8;gen_i=gen_i+1)

begin:label

assign data_out[gen_i]=data_in[7-gen_i];

end

endgenerate

endmoduleVL9 使用子模块实现三输入数的大小比较

`timescale 1ns/1ns

module min(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output reg [7:0] c

);

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

c<= 8'b0;

end else begin

c<= a<b?a:b;

end

end

endmodule

module main_mod(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

input [7:0]c,

output [7:0]d

);

wire [7:0] e;

wire [7:0] f;

reg [7:0] c_d1;

min min1(.clk(clk),.rst_n(rst_n),.a(a),.b(b),.c(e));

min min2(.clk(clk),.rst_n(rst_n),.a(c_d1),.b(e),.c(f));

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

c_d1<=8'b0;//注意打拍

end else begin

c_d1<=c;

end

end

assign d=f;

VL10 使用函数实现数据大小端转换

`timescale 1ns/1ns

module function_mod(

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);//函数定义在module中。

function [3:0] l2b(

input [3:0] in_

);

integer loop;

for(loop=0;loop<4;loop=loop+1) begin

l2b[loop]=in_[3-loop];

end

endfunction

assign c=l2b(a);

assign d=l2b(b);

endmodule

598

598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?