基于晶体管尺寸调整的FPGA低功耗热感知加法器设计

摘要

在本研究中,我们将寻找在90纳米、65纳米、45纳米、40纳米和38纳米工艺技术的现场可编程门阵列中,最具热效率和节能优势的技术,同时寻找最优的气流和散热器配置。我们还对 273.15K‐343.15K温度范围进行了热分析。当我们将基于65纳米和28纳米工艺技术的现场可编程 门阵列环境温度从343.15开尔文降低到283.15开尔文时,在250LFM条件下漏电功耗分别降低了 31.67%和75.71%;在500LFM条件下漏电功耗分别降低了58.53%和75.71%。同样条件下,结 温在250LFM时分别降低了84.54%和85.65%,在500LFM时分别降低了84.90%和85.65%。本 研究中使用的器件包括:90纳米Spartan‐3E 现场可编程门阵列、65纳米Virtex‐5 现场可编程门 阵列、45纳米Spartan‐6 现场可编程门阵列、40纳米Virtex‐6 现场可编程门阵列以及28纳米 Artix‐7 现场可编程门阵列。实验中采用了两种不同的气流条件:250LFM和500LFM。LFM是 气流单位,表示线性英尺每分钟。加法器是我们的目标设计。

引言

在本文中,我们将研究晶体管尺寸调整对现场可编程门阵列的影响。我们采用基于90纳米、65纳 米、45纳米、40纳米和38纳米工艺技术的现场可编程门阵列。我们的主要目的是开发一种节能 设计的方法论。为此,我们正在寻找最节能的技术、最节能的气流以及最节能的散热器配置。加 法器是超大规模集成电路中最简单且基本的设计。加法器也被用作许多电路的基本构建模块。

适用于加法器的技术必然适用于任何复杂的超大规模集成电路设计。因此,我们将分析限定在加法器上。

在本研究中,我们考虑了如图1所示的基于90纳米技术的Spartan‐3E 现场可编程门阵列、基于65纳米技术 的Virtex‐5 现场可编程门阵列、基于45纳米技术的Spartan‐6 现场可编程门阵列、基于40纳米技术的 Virtex‐6 现场可编程门阵列,以及基于28纳米技术的Artix‐7 现场可编程门阵列。我们采用了如图2所示的 两种不同的气流:250LFM和500LFM。LFM是气流的单位,即线性英尺每分钟。在国际单位制中,LFM相 当于0.01m/s。来自空调、冷却器或风扇的空气流动总会给我们带来舒适的感觉。

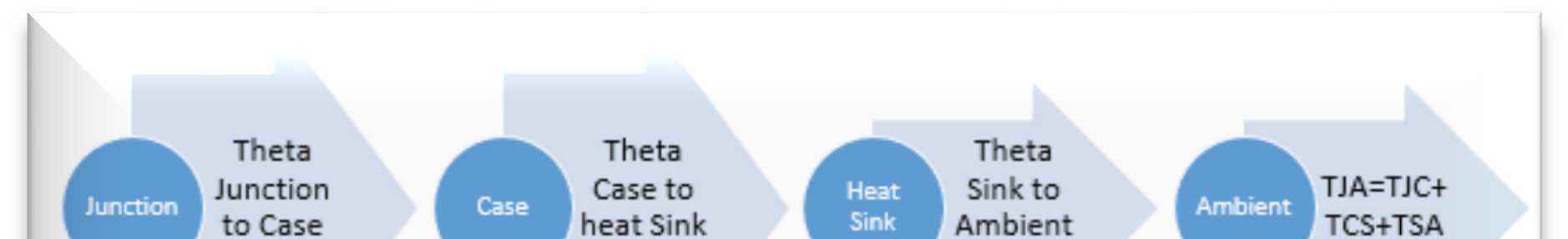

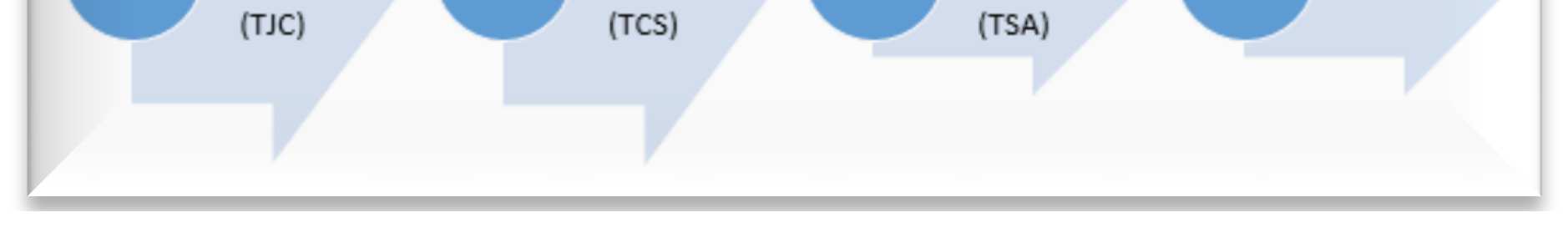

类似地,以热量形式耗散功率的器件,在散热器上安装风扇提供气流时也会有良好的散 热效果。器件的温度称为结温,环境的温度称为环境温度。结温也高于环境温度。用数学术 语表示,结温是环境温度与TJA和TP乘积的总和。这里的环境是一个广义术语,包括外壳、 散热器和房间,如图3所示。上述为热量流动示意图。TP是所考虑设计的总功耗。TJA是结 到环境的热阻。工作中的现场可编程门阵列(FPGA)的结点作为热源,环境作为散热器[1]。

目前在热感知设计方面已有大量研究工作正在进行[1‐9] 。在研究现有的热感知设计方法论 过程中,我们查阅了热感知FIR滤波器设计[2], 、温度感知设计的热建模[3], 、热感知算术 逻辑单元(ALU)[4], 、NoC中的热平衡设计[5], 、热感知 Unicode读取器[6], 、热感知 3D微处理器[7], 、帧缓冲器(Frame Buffer)[8]以及微架构级别的热感知布局规划[9]。

JT通过AT、热功率和TJA来衡量,如图4所示。其中,TJA是结到环境的热阻(℃/W), 热功率是设计的总功耗。TJA热阻是TJC(结到外壳的热阻)、TCS(外壳到散热器的热阻) 和TSA(散热器到环境的热阻)三项热阻的总和,如图1[1]所示。

我们使用了三种不同类型的散热器,如图5所示。分别是低轮廓散热器、中型散热片和高型 散热片。特别地,我们还考虑了不使用任何散热器的情况,并将该情况专门归类为无散热器。我 们的目标设计采用三个输入:输入1、输入2和进位输入,并计算进位输出和和,如图6所示。

250 LFM和500LFM下的功耗

表1 无轮廓散热器和低轮廓散热器的功耗

| 环境温度 | 250 LFM 90纳米 | 250 LFM 65纳米 | 500LFM 90纳米 | 500LFM 65纳米 | 250 LFM 40纳米 | 250 LFM 28纳米 | 500LFM 40纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 0.032 | 0.248 | 0.026 | 0.248 | 1.041 | 0.034 | 1.039 | 0.03 |

| 298.15开尔文 | 0.034 | 0.289 | 0.027 | 0.289 | 1.121 | 0.042 | 1.118 | 0.042 |

| 313.15开尔文 | 0.036 | 0.342 | 0.029 | 0.341 | 1.218 | 0.058 | 1.214 | 0.058 |

| 328.15开尔文 | 0.039 | 0.410 | 0.031 | 0.409 | 1.338 | 0.087 | 1.332 | 0.087 |

| 343.15开尔文 | 0.043 | 0.499 | 0.033 | 0.495 | 1.484 | 0.140 | 1.477 | 0.140 |

在250 LFM条件下,基于90纳米、65纳米工艺技术的现场可编程门阵列漏电功耗分别降低了25.58%、 50.30%,基于40纳米、28纳米工艺技术的现场可编程门阵列漏电功耗分别降低了29.85%、75.71%。

当我们将环境温度从343.15K降低到283.15K时,对于500 LFM,基于90nm、65nm工艺 技术的FPGA漏电功耗分别减少了21.21%、49.89%,基于40nm、28nm工艺技术的 FPGA漏电功耗分别减少了29.65%、75.71%,如表2所示,相应数据如表1所示。

对于基于90纳米和65纳米工艺技术的FPGA,当气流从250LFM增加到500LFM、环境温度为328.15开 尔文和343.15开尔文时,漏电功耗分别降低了20.51%、23.26%和48.80%,如图7所示;对于基于40纳米和 28纳米工艺技术的FPGA,漏电功耗分别降低了20.68%、44.84%和0.00%,如图8所示。

表2:中型散热片的功耗

| 环境温度 | 250LFM 65纳米 | 250LFM 40纳米 | 500LFM 65纳米 | 500LFM 40纳米 | 250LFM 65纳米 | 250LFM 28纳米 | 500LFM 65纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 1.289 | 1.373 | 1.282 | 1.368 | 1.289 | 0.034 | 1.280 | 0.034 |

| 298.15开尔文 | 1.568 | 1.509 | 1.556 | 1.502 | 1.568 | 0.042 | 1.554 | 0.042 |

| 313.15开尔文 | 1.944 | 1.676 | 1.925 | 1.667 | 1.944 | 0.058 | 1.921 | 0.058 |

| 328.15开尔文 | 2.456 | 1.880 | 2.424 | 1.868 | 2.456 | 0.087 | 2.416 | 0.087 |

| 343.15开尔文 | 3.157 | 2.133 | 3.100 | 2.115 | 3.157 | 0.140 | 3.087 | 0.140 |

在250 LFM条件下,当环境温度从343.15开尔文降低到283.15开尔文时,基于65纳米、40纳米工 艺技术的现场可编程门阵列的漏电功耗分别减少了59.17%、35.63%;对于基于65纳米、28纳米工艺 技术的现场可编程门阵列,漏电功耗分别减少了31.67%、75.71%。在500 LFM条件下,当环境温度 从343.15开尔文降低到283.15开尔文时,基于65纳米和40纳米工艺技术的现场可编程门阵列的漏电功 耗分别减少了58.64%、35.31%,而基于65纳米、28纳米工艺技术的现场可编程门阵列的漏电功耗分 别减少了58.53%、75.71%,如表2所示。

250 LFM和500LFM的最高环境温度

表3 无轮廓和低轮廓散热器的最高环境温度

| 环境温度 | 250LFM 90纳米 | 250LFM 65纳米 | 500LFM 90纳米 | 500LFM 65纳米 | 250LFM 40纳米 | 250LFM 28纳米 | 500LFM 40纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 83.7 | 83.4 | 83.8 | 83.4 | 81.9 | 84.9 | 82.5 | 84.9 |

| 298.15开尔文 | 83.6 | 83.4 | 83.8 | 83.4 | 81.9 | 84.9 | 82.5 | 84.9 |

| 313.15开尔文 | 83.5 | 83.1 | 83.7 | 83.1 | 81.7 | 84.9 | 82.3 | 84.9 |

| 328.15开尔文 | 83.4 | 82.8 | 83.6 | 83.0 | 81.4 | 84.8 | 82.0 | 84.8 |

| 343.15开尔文 | 83.2 | 82.3 | 83.5 | 82.6 | 81.1 | 84.7 | 81.7 | 84.7 |

对于250 LFM,当环境温度从283.15开尔文升高到343.15开尔文时,基于90纳米、65纳米工艺技术的 现场可编程门阵列最高环境温度分别降低了59.73%、2.03%,基于40纳米、28纳米工艺技术的现场可 编程门阵列最高环境温度分别降低了59.73%、2.03%。对于500 LFM,如表3所示,当环境温度从 283.15开尔文升高到343.15开尔文时,基于90纳米、65纳米工艺技术的现场可编程门阵列最高环境温 度分别降低了47.73%、1.5%;基于40纳米、28纳米工艺技术的现场可编程门阵列最高环境温度分别 降低了1.3%、35.33%。

表4 中型和高型散热片的最高环境温度

| 环境温度 | 250LFM 65纳米 | 250LFM 40纳米 | 500LFM 65纳米 | 500LFM 40纳米 | 250LFM 65纳米 | 250LFM 28纳米 | 500LFM 65纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 83.5 | 81.6 | 82.2 | 84.0 | 83.7 | 84.9 | 84.1 | 84.9 |

| 298.15开尔文 | 83.2 | 81.6 | 82.2 | 84.0 | 83.7 | 84.9 | 84.1 | 84.9 |

| 313.15开尔文 | 82.8 | 81.2 | 81.9 | 83.8 | 83.5 | 84.9 | 83.9 | 84.9 |

| 328.15开尔文 | 82.2 | 80.8 | 81.6 | 83.5 | 83.1 | 84.8 | 83.6 | 84.8 |

| 343.15开尔文 | 81.4 | 80.3 | 81.2 | 83.1 | 82.6 | 84.7 | 83.3 | 84.8 |

对于250 LFM,当环境温度从283.15开尔文升高到343.15开尔文时,基于65纳米、40 纳米工艺技术的现场可编程门阵列的最大环境温度分别降低了2.51%、2.32%,以及最大环 境温度分别降低了2.15%、35.3%。对于500 LFM,当环境温度从283.15开尔文升高到 343.15开尔文时,如表4所示,基于65纳米、40纳米工艺技术的现场可编程门阵列的最大环 境温度分别降低了1.8%、1.78%,以及最大环境温度分别降低了1.5%、35.3%。

250 LFM和500LFM的结温

表5 无轮廓与低轮廓散热器的结温

| 环境温度 | 250LFM 90纳米 | 250LFM 65纳米 | 500LFM 90纳米 | 500LFM 65纳米 | 250LFM 40纳米 | 250LFM 28纳米 | 500LFM 40纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 11.3 | 11.6 | 11.2 | 11.6 | 13.1 | 10.1 | 12.5 | 10.1 |

| 298.15开尔文 | 26.4 | 26.9 | 26.3 | 26.9 | 28.3 | 25.1 | 27.7 | 25.1 |

| 313.15开尔文 | 41.5 | 42.2 | 41.4 | 42.0 | 43.6 | 40.2 | 43.0 | 40.2 |

| 328.15开尔文 | 55.6 | 57.7 | 56.5 | 57.4 | 58.9 | 55.3 | 58.3 | 55.3 |

| 343.15开尔文 | 71.8 | 71.6 | 72.9 | 74.4 | 70.5 | 73.6 | 70.5 | 73.3 |

在250 LFM条件下,当环境温度从343.15开尔文降至283.15开尔文时,基于90纳米、65纳米工艺技术 的现场可编程门阵列结温分别降低了84.26%、84.17%,基于40纳米、28纳米工艺技术的现场可编程 门阵列结温分别降低了82.39%、85.67%。在500 LFM条件下,当环境温度从343.15开尔文降至 283.15开尔文时,如表5所示,基于90纳米、65纳米工艺技术的现场可编程门阵列结温分别降低了 84.35%、84.08%,基于40纳米、28纳米工艺技术的现场可编程门阵列结温分别降低了83.01%、 85.67%。

当我们将气流从250LFM增加到500LFM,环境温度为328.15开尔文、343.15开尔文时,基于90 纳米和65纳米工艺技术的FPGA结温分别降低了1.5%、27.9%和51.9%、54.5%,如图11所示;而基 于40纳米和28纳米工艺技术的FPGA结温分别降低了1.01%、1.07%,且无明显降低,如图12所示。

表6 中型散热片与高型散热片的结温

| 环境温度 | 250LFM 65纳米 | 250LFM 40纳米 | 500LFM 65纳米 | 500LFM 40纳米 | 250LFM 65纳米 | 250LFM 28纳米 | 500LFM 65纳米 | 500LFM 28纳米 |

|---|---|---|---|---|---|---|---|---|

| 283.15开尔文 | 11.5 | 13.4 | 11.0 | 12.1 | 11.3 | 10.1 | 10.9 | 10.1 |

| 298.15开尔文 | 26.8 | 28.8 | 26.2 | 28.1 | 26.5 | 25.1 | 26.1 | 25.1 |

| 313.15开尔文 | 42.2 | 44.2 | 41.5 | 43.4 | 41.9 | 40.2 | 41.4 | 40.2 |

| 328.15开尔文 | 57.8 | 59.7 | 56.9 | 58.8 | 57.4 | 55.3 | 56.7 | 55.2 |

| 343.15开尔文 | 73.6 | 75.3 | 72.5 | 74.3 | 73.1 | 70.4 | 72.2 | 70.4 |

在250 LFM条件下,当环境温度从343.15K降低到283.15K时,基于65nm、40nm工 艺技术的FPGA结温分别降低了84.37%、82.20%,基于65nm、28nm工艺技术的FPGA结 温分别降低了54%、85.65%。在500 LFM条件下,当环境温度从343.15K降低到283.15K 时,基于65nm、40nm工艺技术的FPGA结温分别降低了84.82%、83.71%,基于65nm、 28nm工艺技术的FPGA结温分别降低了84.90%、85.65%,如表6所示。

当我们将气流从250LFM增加到500LFM时,对于基于65 nm和40nm工艺技术的现场可编程门阵 列,在环境温度为328.15开尔文、343.15开尔文的情况下,结温分别降低了1.55%、1.49%、1.50%、 1.32%(如图13所示);而对于基于65nm和28nm工艺技术的现场可编程门阵列,在环境温度为 328.15开尔文、343.15开尔文的情况下,结温分别降低了1.21%、1.23%,且无降低(如图14所示)。

结论

在5种不同工艺技术中,基于90纳米技术的现场可编程门阵列漏电功耗最小,而基于40纳米技术的现场可编 程门阵列漏电功耗最大。同样,在90纳米、65纳米、45纳米、40纳米和28纳米工艺技术的现场可编程门阵 列中,最高环境温度在28纳米技术中最高,在40纳米技术中最低。根据我们的热分析观察结果,结温在基于 40纳米技术的现场可编程门阵列中最高,在基于28纳米技术的现场可编程门阵列中最低。

未来展望

该设计在90纳米、65纳米、45纳米、40纳米和28纳米的现场可编程门阵列上实现。未来,我们 可以进一步拓展至超大规模现场可编程门阵列、片上系统和三维集成电路。本研究中的目标设计 为加法器。未来,热感知和节能型算术逻辑单元、数学协处理器、处理器以及多核架构的设计具 有广阔的发展空间。本设计在273.15K‐343.15K的控制温度下进行仿真。未来,可以开展适用于 北极、赤道或超出273.15K‐343.15K范围等极端温度环境下的设计。未来展望包括改善功耗,因 为加法器作为电路中广泛存在的核心元件,功耗是主要影响因素。对于未来的现场可编程门阵列 电路而言,优化进位路径以支持基于树的设计,从而优化布局与布线,将是充分且必要的发展方 向。

1470

1470

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?