全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

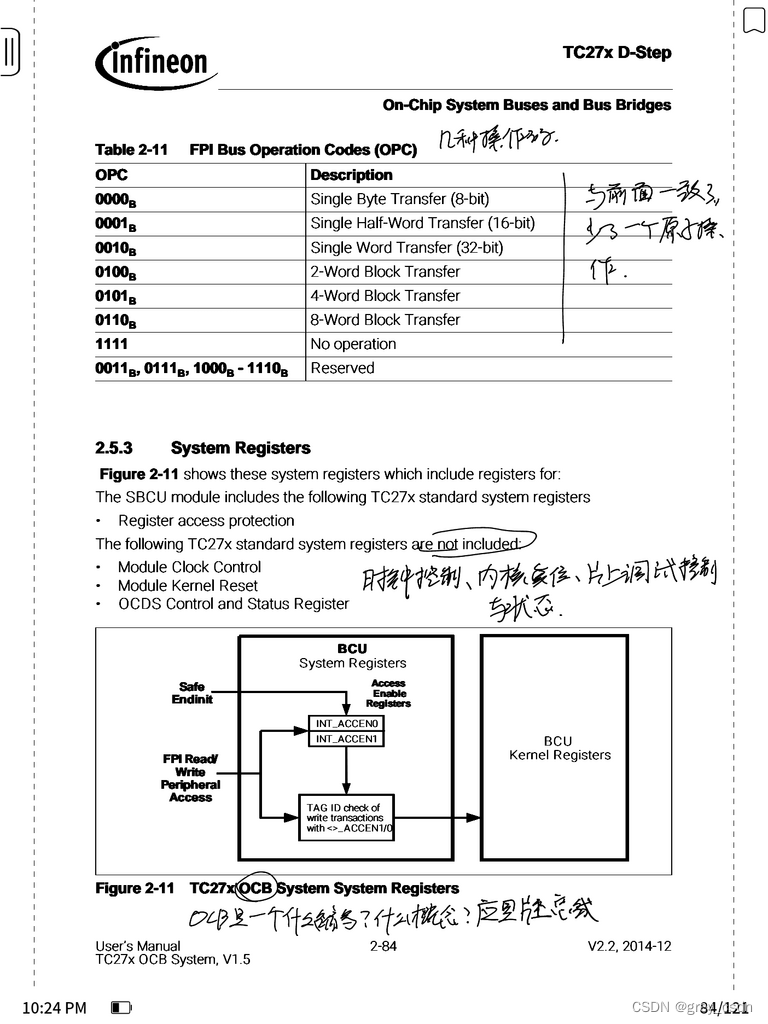

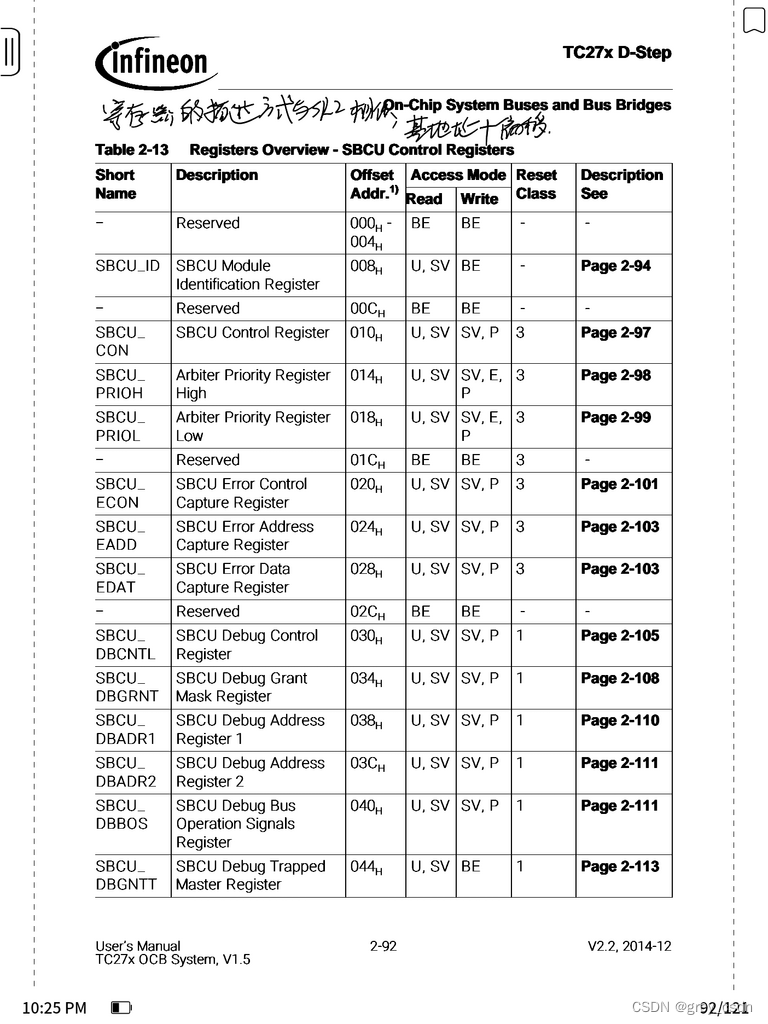

1. SBCU相关的系统寄存器中不包括时钟控制、内核复位、片上调试控制与状态寄存器。

2. 这里出现了一个OCB的缩写,没有一个明确的解释,应该是片上系统总线的缩写。

1. 与SRI相似,FPI也有一个TAG ID进行身份的标识。

2. 这里也有一个ENDINIT的保护,没有说明是来自于什么。有SRI相关的介绍信息,估计这里的实现也是类似的,相关的保护应该是来自于看门狗模块。

3. OCB系统模块不支持OCDS控制以及状态寄存器的相关功能。

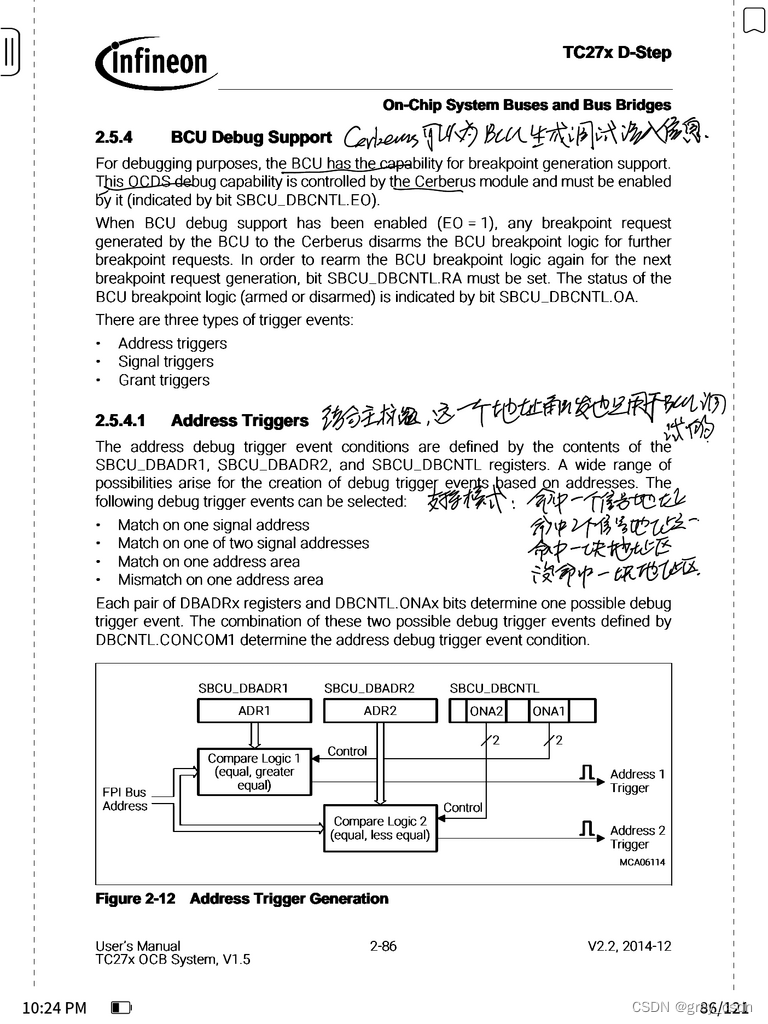

1. 之前看调试系统的时候接触过这个Cerberus,主要是提供调试功能的。从这里看,Cerberus可以为BCU生成调试诸如信息。

2. 寻址触发,结合父级的标题,大概可以看得出来这个寻址触发其实也是用于BCU调试的。支持的模式有:命中一个信号地址、命中2个信号地址、命中一块地址区、没有命中一块地址区。这样的模式有一点有意思,其实我觉得最后两种就可以组合出来四种模式。

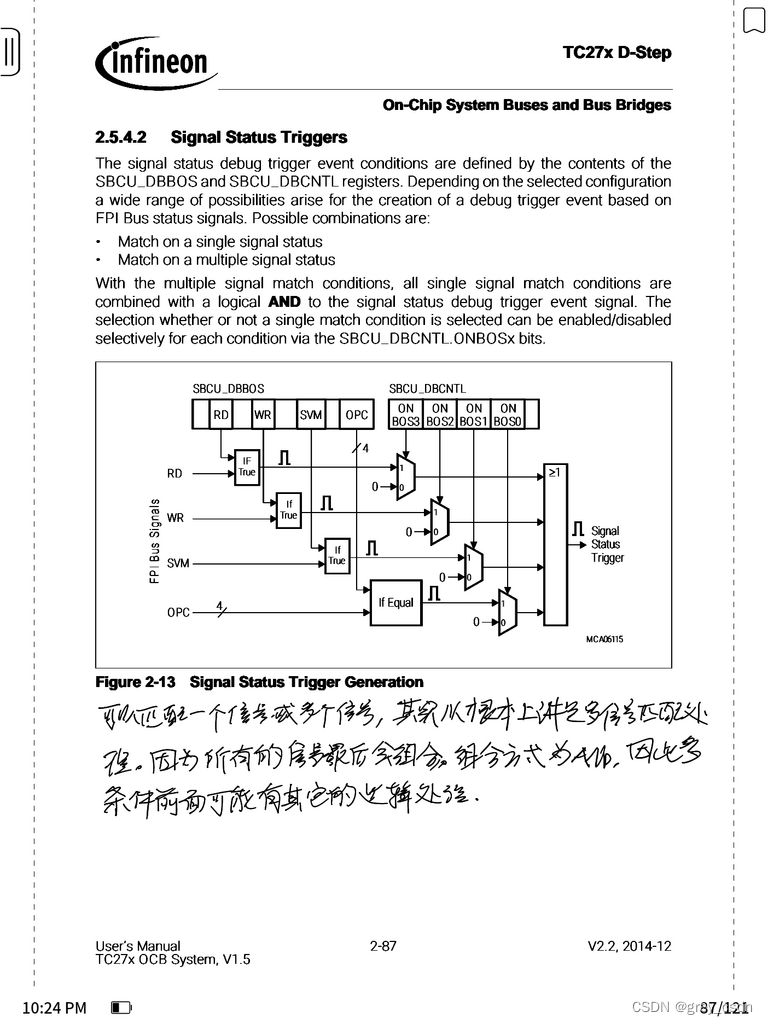

信号状态触发的生成,可以匹配一个信号或者多个信号。其实,从根本上讲是多个信号的匹配处理,因为,所有的信号最后都会进行综合的组合,组合的方式是AND运算。因此,多条件前面可能有其他的逻辑处理。

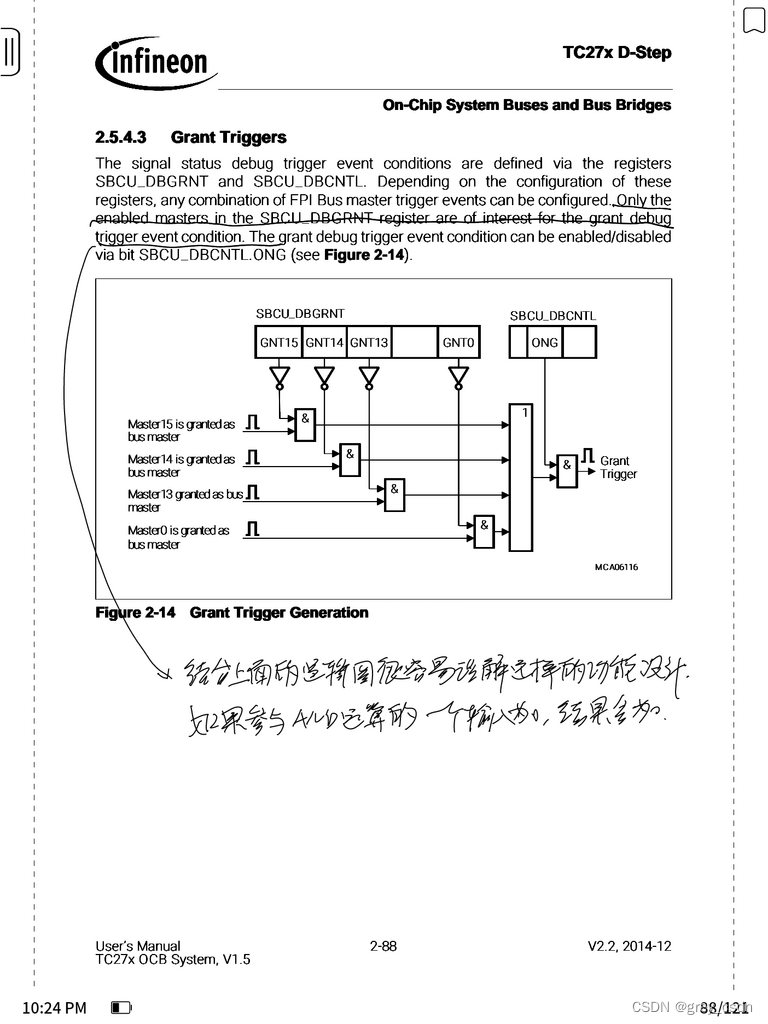

授权的触发。结合上面的逻辑图其实很容易理解这样的功能设计,吐过参与AND运算的一个输入为0,那么结果也就是0,意味着相关的功能禁用。

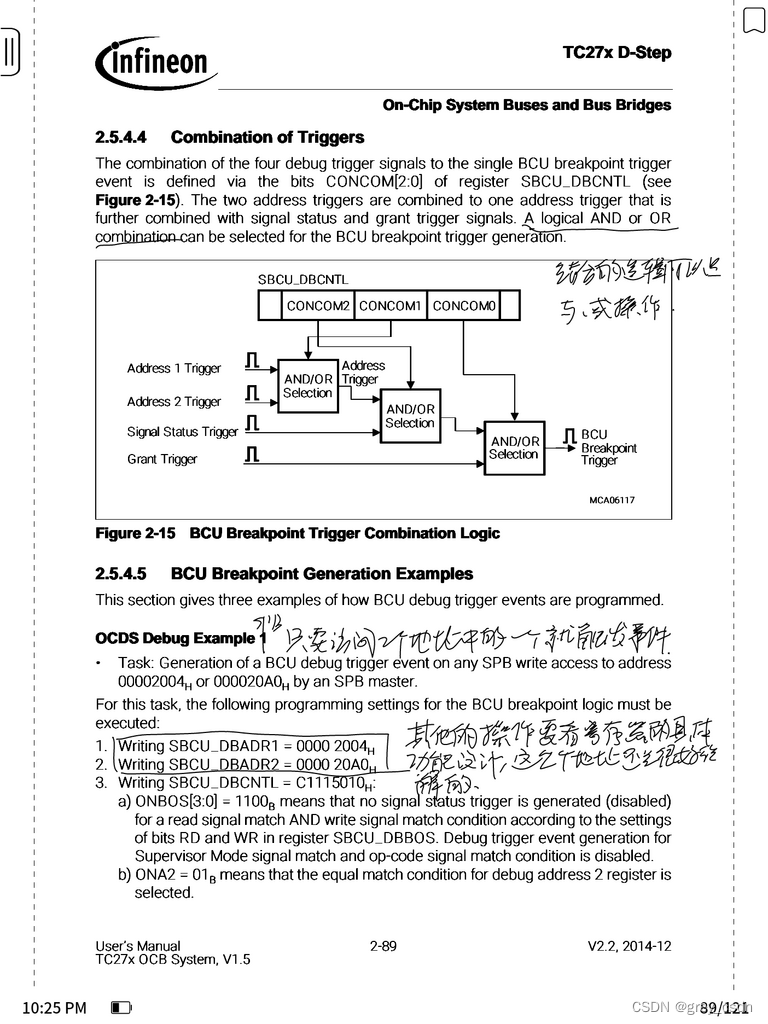

1. 组合触发相对来书在硬件设计上应该是复杂一些,因为实现的不是一个单纯的逻辑操作,而是可以选择与或者或。

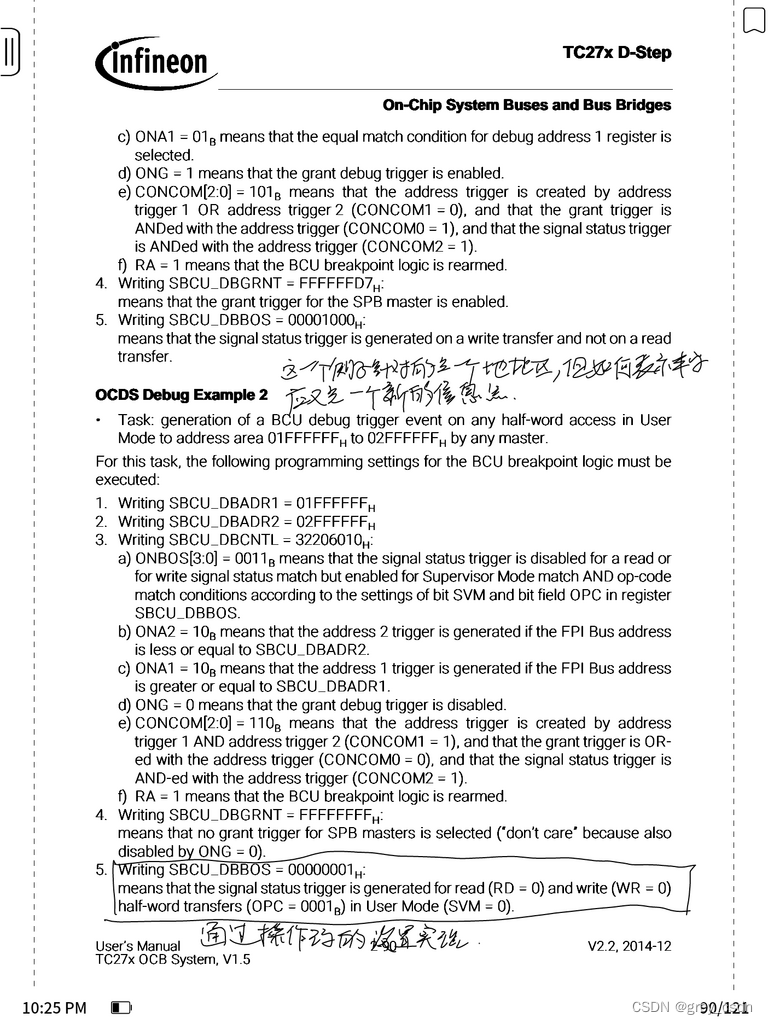

2. 这里给出来的第一个例子中,SPB只要是访问2个地址中的一个就会触发一个事件。其实,从操作流程描述中可以很清楚的看到这两个地址是如何设置的,至于其他的寄存器的配置可能还是得深入理解才行。

1. 这是第二个例子,针对的是一个地址区。但是,如何表示半字的处理又是一个全新的信息点。

2. 结合这里画出来的第5条,其实这个半字的处理是通过OPC,也就是操作码的设置来实现的。

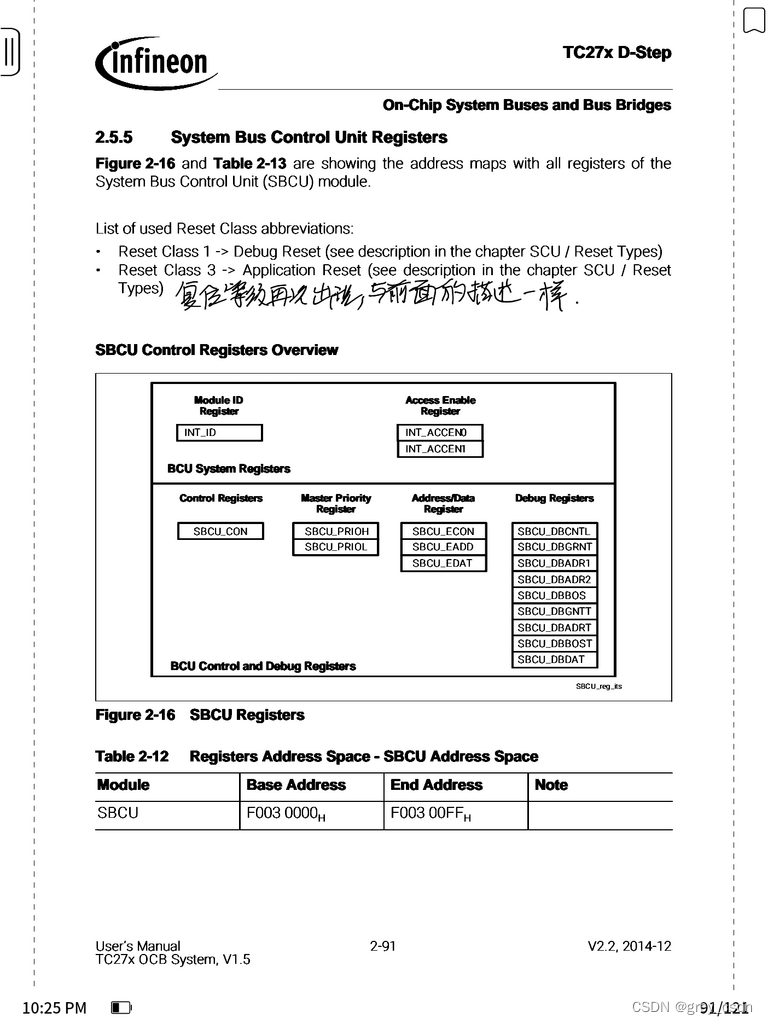

这一页其实没有太多值得去深入分析的内容,但是之前看文档遇到的复位的等级在这里再次出现。暂且也不去仔细区分这之间的差异,相应的学习计划已经加入到了我的计划清单当中。

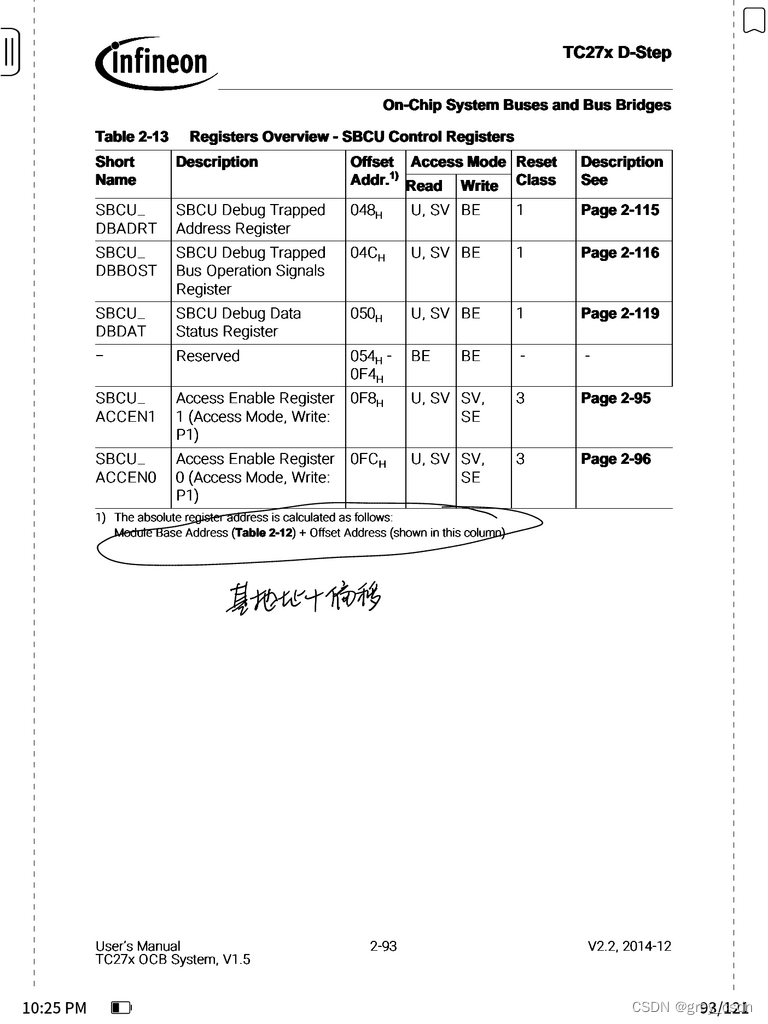

寄存器地址信息的提供跟SRI是很相似的,提供的是一个起始地址加上偏移。这样的形式在软件实现上其实还是很容易来做到的,直接通过位操作比较容易写,不用为了做位的解释实现位域的数据结构。

这一次的内容整理暂且看这么多,剩下的基本上都是寄存器的实际介绍,等下一次再做整理。

7173

7173

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?