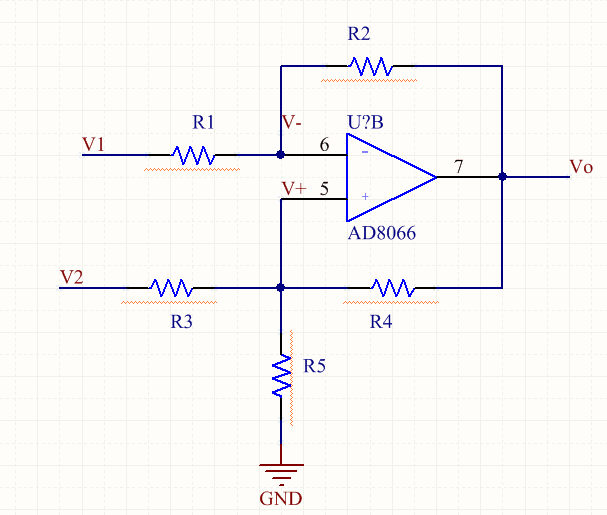

由麻省理工的Brad Howland发明的运放电流源:

运放采用AD8066,供电电压在+-12V到+-15V之间

实际应用时,一定要根据运放的电压范围来选择边路电阻大小,若电阻流过电流的压降大于运放电源范围,则电路无实际意义。

根据运放虚短和虚断的概念,

设: V+ = V- = Vi

可得: (V1-Vi)/R1 = (Vi-Vo)/R2

(V2-Vi)/R3 + (Vo-Vi)/R4 = Vi/R5

联立上面的方程可得到:

I = Vi/R5 = (V2-Vi)/R3 + (V1-Vi)R2/R1/R4

=((V2-Vi)R1R4 - (V1-Vi)/R2R3) / R1R2R3

可看出当 R1R4=R2R3 时,

I = (V2-V1)/ R3

第二类电路:

根据运放虚短和虚断的概念,

设: V+ = V- = Vi

可得: Vi/R1 = (Vo-Vi)/R2

Vi = (1+R2/R1)Vo

又由虚断: (V2-Vi)/R3 = (V2 - Vx)/(R3+R4)

(V2-Vi)/R3 + Vx/R6 =(Vo-Vx)/R5

当满足 R2/R1 = (R4+R5)/R3 时, I = V2 / R5

2208

2208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?