提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

概述

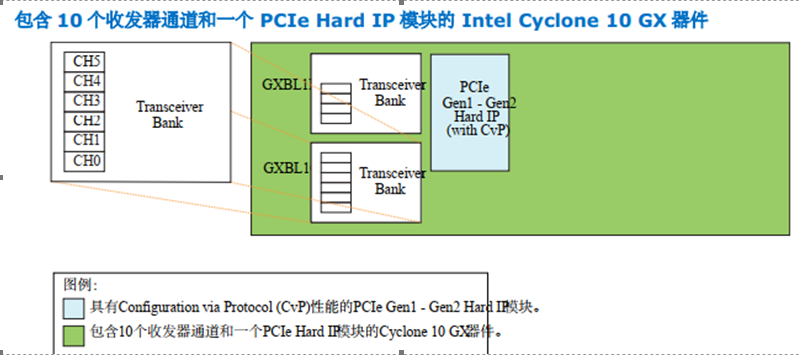

目标芯片: 10CX220YF672I5G

Intel Cyclone 10 GX 器件提供 6, 10 或 12 个收发器通道。每个收发器 bank 有高达六个收发器

通道。

收发器 bank 是一个基础单元,包含与器件的高速串行收发器相关的所有功能模块。每个收发器 bank 均包含四个或六个收发器通道

10CX220YF672I5G这个芯片包含了10个收发器通道,那应该就是如下图所示

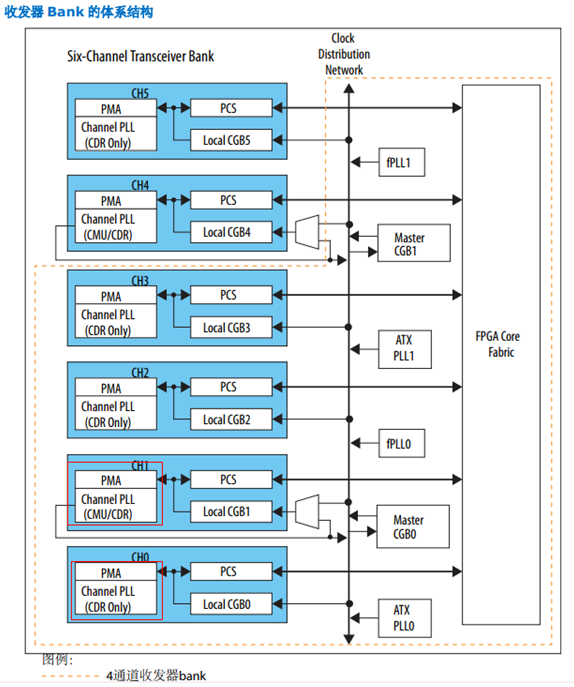

收发器体系结构

PMA、PCS自然不用说,和xilinx类似,也是老熟人了

这里的新概念包括,Channel PLL(CDR Only CMU/CDR)、Local CGB、Master CGB、Fpll、ATX PLL。看来跟之前xilinx Z7系列的QPLL和CPLL还是有不少区别

注意:每个通道的channel PLL有一点区别

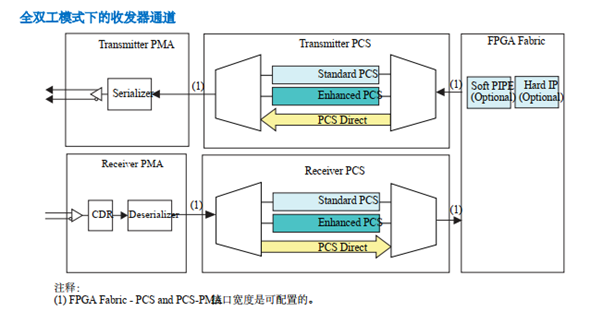

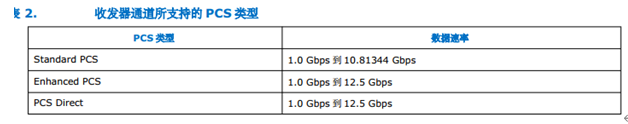

收发器通道

Intel Cyclone 10 GX 收发器通道有三种类型的 PCS 模块,可支持介于 1.0 Gbps 与 10.81344

Gbps 之间的连续数据速率。

收发器锁相环

Intel Cyclone 10 GX 器件内的每个收发器通道都可以直接访问三种类型的高性能 PLL:

Advanced Transmit (ATX) PLL

Fractional PLL (fPLL)

Channel PLL / Clock Multiplier Unit (CMU) PLL

这些收发器 PLL 与 Master 或者 Local Clock Generation Blocks (CGB)共同驱动收发器通道。

小数分频 PLL (Fractional PLL (fPLL))

小数分频 PLL (fPLL)是一种备用发送 PLL,为高达 12.5 Gbps 数据速率的应用生成时钟频率。

fPLL 既支持整数频率综合,也支持精细分辨率小数频率综合。与 ATX PLL 不同的是, fPLL 可用于

综合各种可通过 FPGA 架构时钟网络来驱动内核的频率。

通道 PLL (CMU/CDR PLL)

通道 PLL 位于本地的每个收发器通道中。它的的主要功能是在 PLL 用于时钟和数据恢复(CDR)模式

时对收发器通道内的时钟和数据进行恢复。当通道 1 和通道 4 的通道 PLL 在时钟乘法器单元(CMU)

模式下配置时可用作发送 PLL。通道 0、 2、 3 和 5 的通道 PLL 不能在 CMU 模式下配置,因此不能

用作发送 PLL。

也就是说如果我们只用到channel PLL的话,通道0、 2、 3 和 5只能配置为接收。不过暂时不会考虑只用channel PLL的情况

时钟生成模块(CGB)

在 Intel Cyclone 10 GX 器件中,有两种类型的时钟生成模块(CGB):

Master CGB(主 CGB)

Local CGB(本地 CGB)

包含六个收发器通道的收发器 bank 有两个主 CGB。主 CGB1 位于收发器 bank 的顶端,主 CGB0

位于收发器 bank 的底端。主 CGB 会将 bonded 时钟划分并分配到一个 bonded 通道组中。它还

会将 non-bonded 时钟分配到整个 x6/xN 时钟网络中的 non-bonded 通道中。

785

785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?