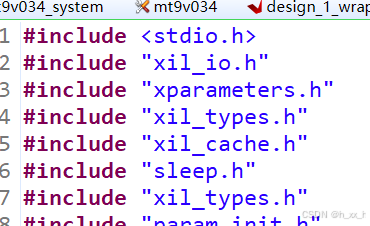

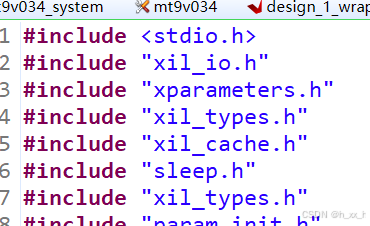

vivado自己创建ip核后,导出的硬件.xsa文件在vitis端无法使用,编译出现makefile等报错,一般会导致c语言的一些头文件显示找不到

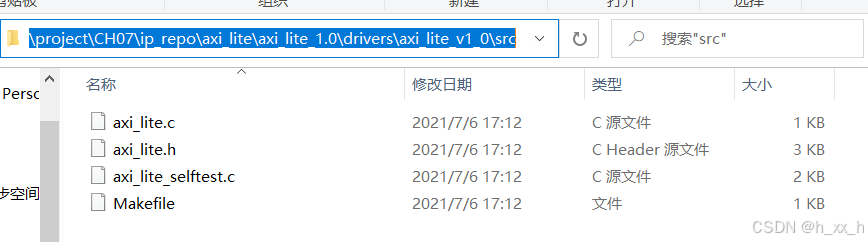

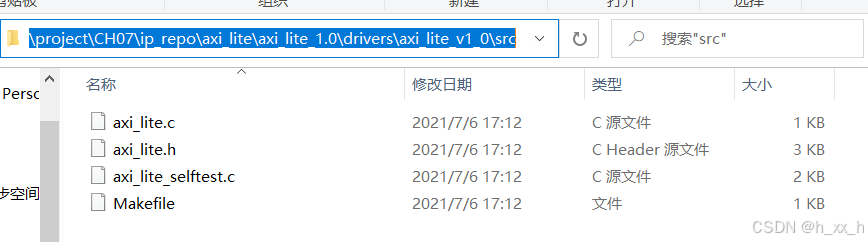

这种情况只需要更改ip核文件下的makefile文件(以axi_lite的ip核为例) 用notepad等软件打开makefile文件,加入以下内容

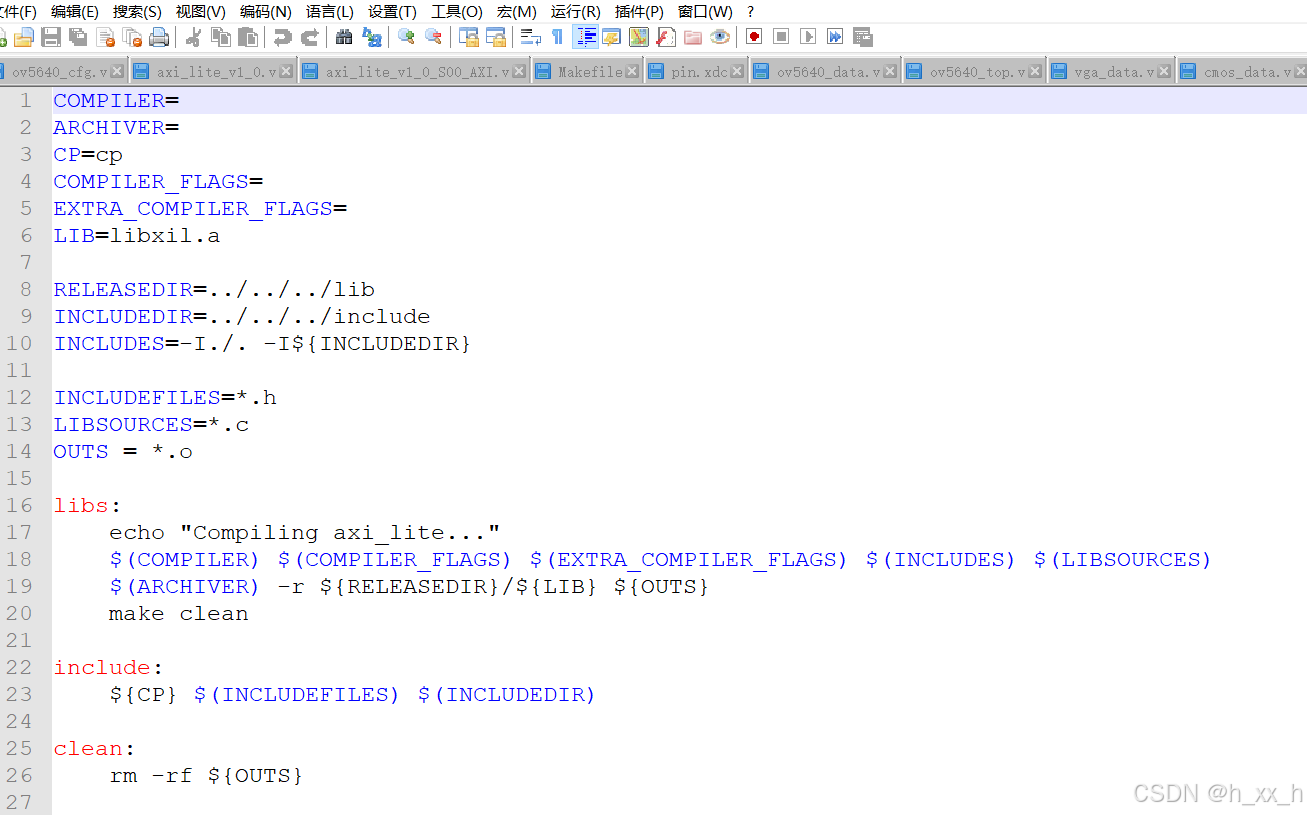

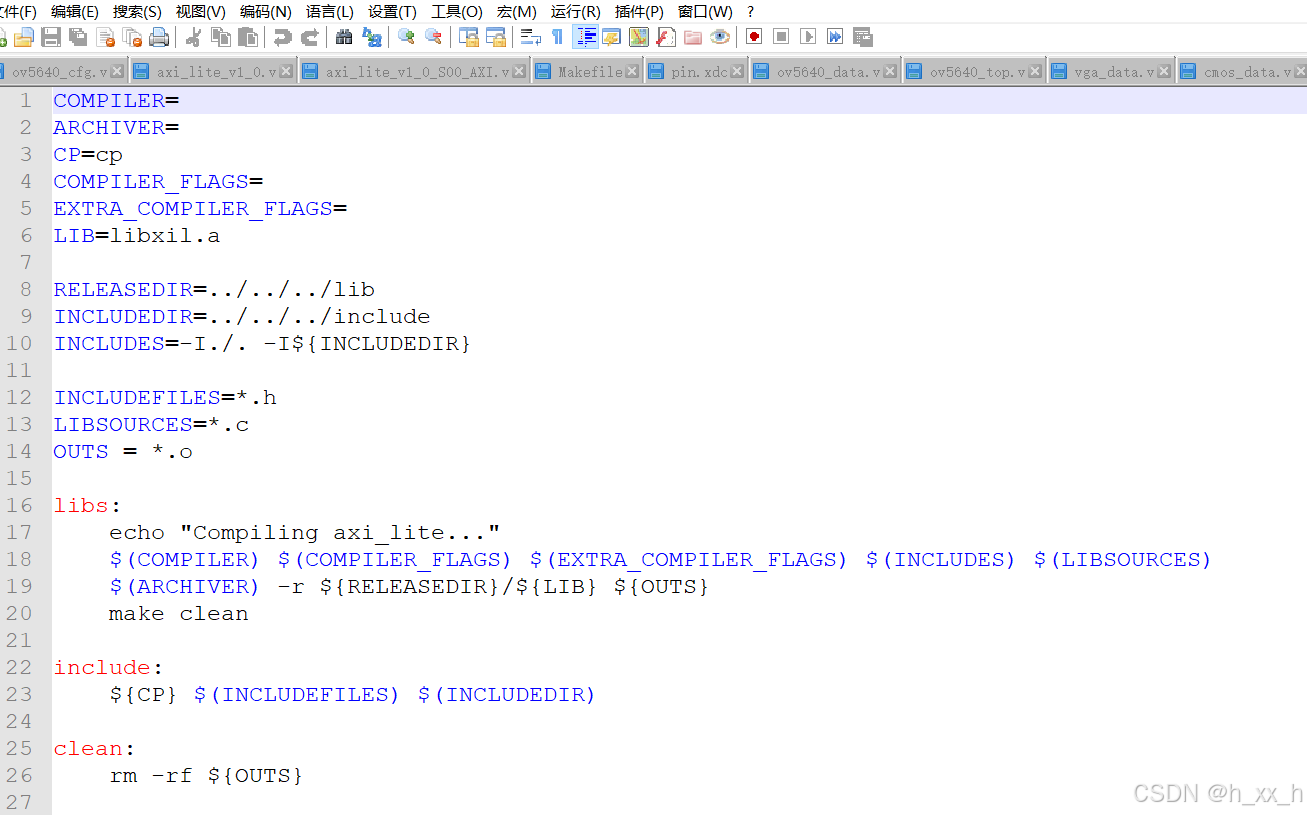

用notepad等软件打开makefile文件,加入以下内容

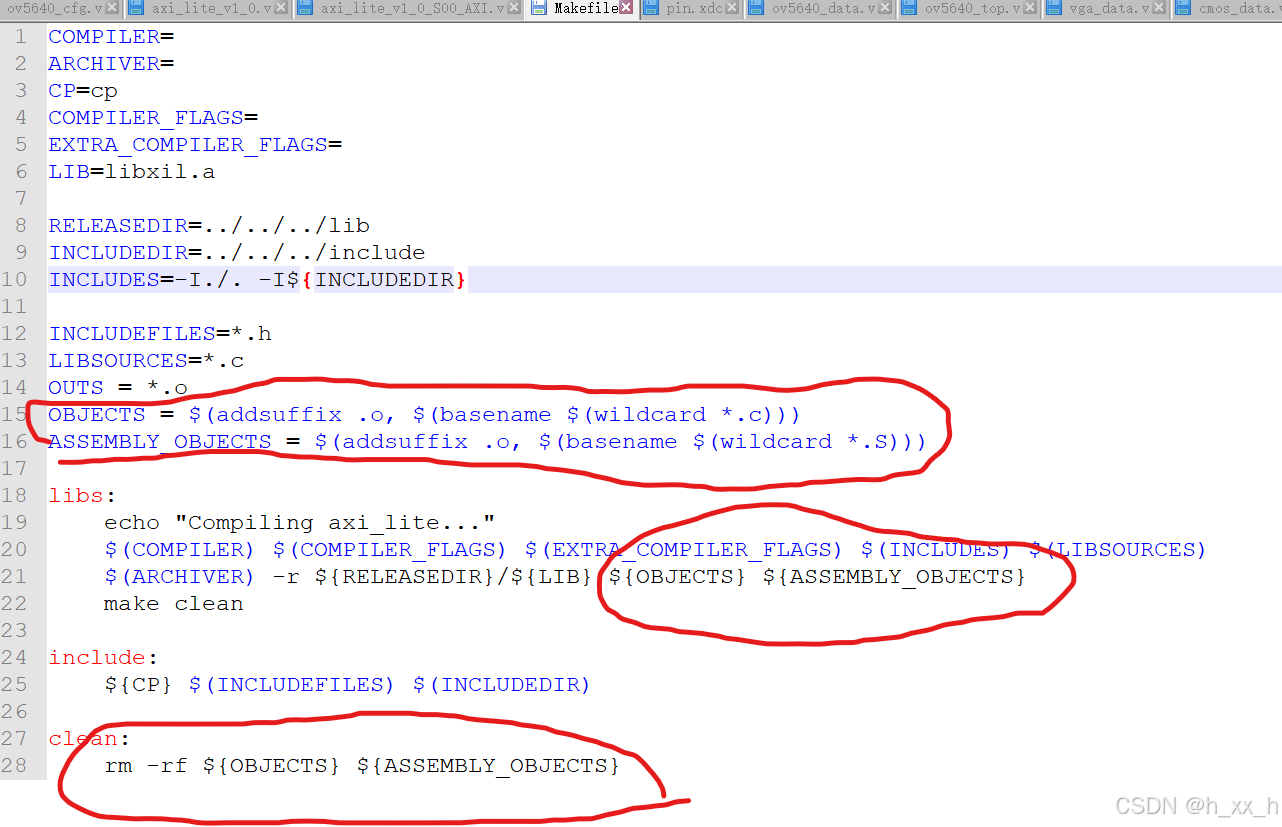

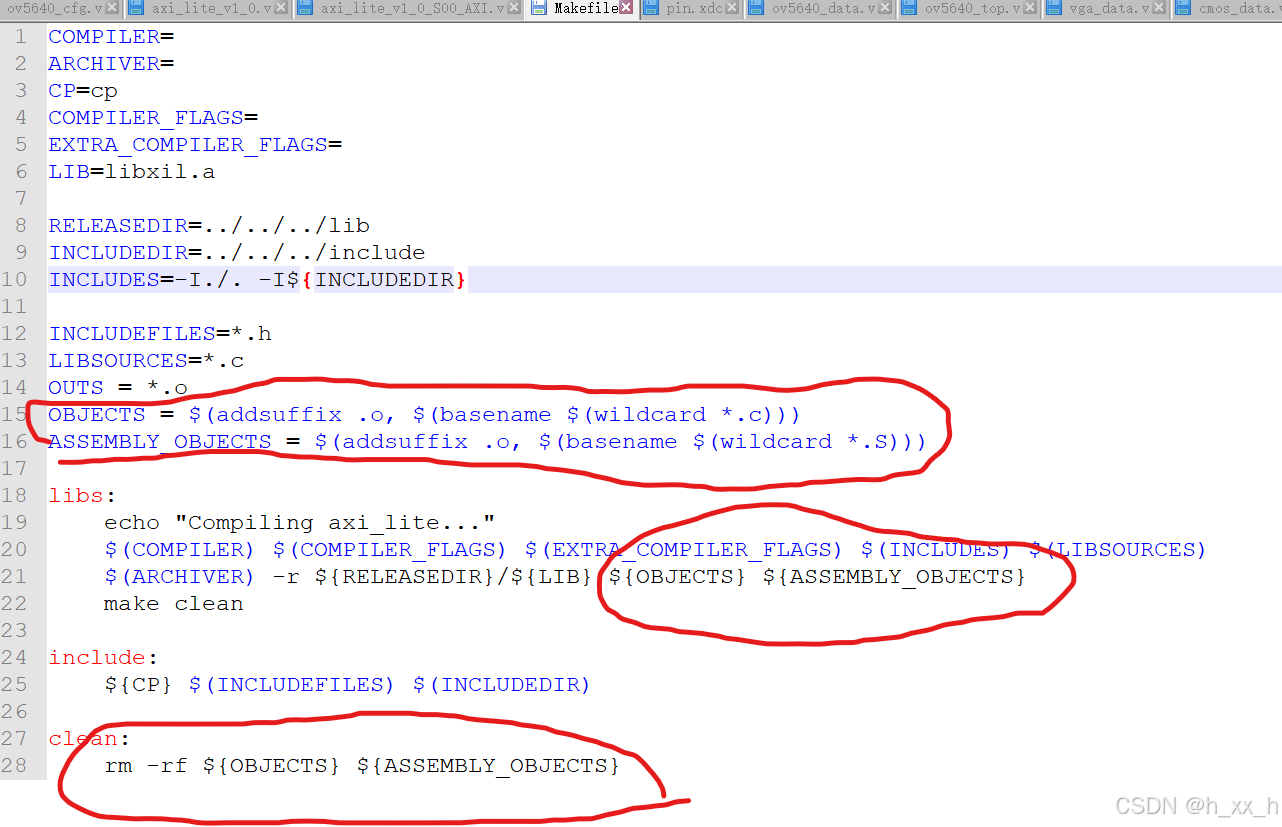

将图二圈出的代码加入到图一中,ip核即可正常使用,导出的硬件xsa文件即可正常使用了,vitis也会成功编译

vivado自己创建ip核后,导出的硬件.xsa文件在vitis端无法使用,编译出现makefile等报错,一般会导致c语言的一些头文件显示找不到

这种情况只需要更改ip核文件下的makefile文件(以axi_lite的ip核为例) 用notepad等软件打开makefile文件,加入以下内容

用notepad等软件打开makefile文件,加入以下内容

将图二圈出的代码加入到图一中,ip核即可正常使用,导出的硬件xsa文件即可正常使用了,vitis也会成功编译

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?