.xsa文件的生成

Vivado工程建立

1 建立Vivado工程,添加相应的IP核,并对IP核进行配置

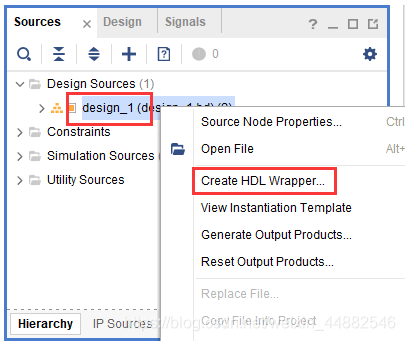

2 选择 Block 设计,右键“Create HDL Wrapper…” ,创建一个 Verilog 或 VHDL 文件,为 block design 生成 HDL 顶层文件。

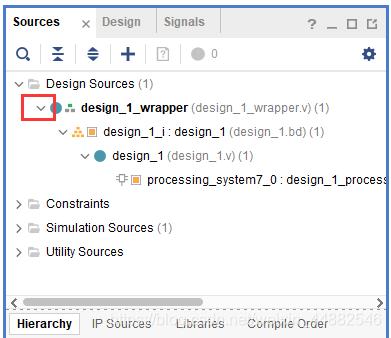

3 展开设计可以看到 PS 被当成一个普通 IP 来使用。

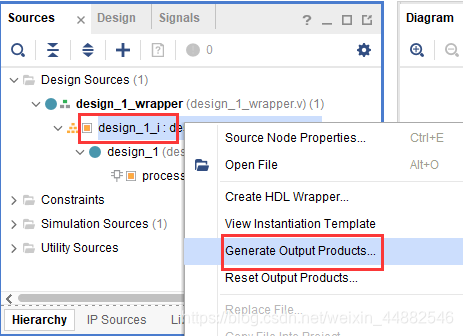

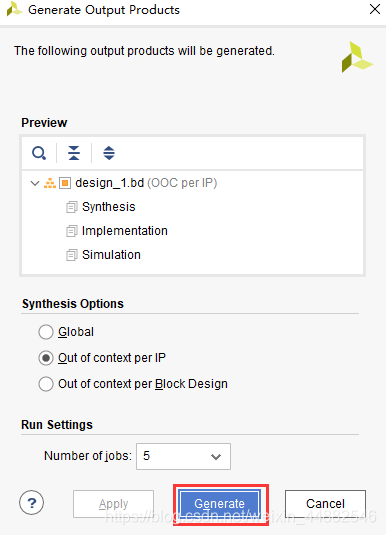

4 选择 block 设计,右键“Generate Output Products”,此步骤会生成 block 的输出文件,包括 IP,例化模板, RTL 源文件, XDC 约束,第三方综合源文件等等。供后续操作使用。

5 点击“Generate”

6 其实并不是说 PS 端的引脚不需要绑定,而是在 IP 生成的输出文件里已经包含了 PS 端引脚分配的 XDC 文件,在 IP Sources, Block Designs–>design_1–>Synthesis 中,可以看到处理器的 XDC 文件,绑定了 PS 端的 IO,因此不需要再新建 XDC 绑定这些引脚。但需要XDC文件约束PL管脚

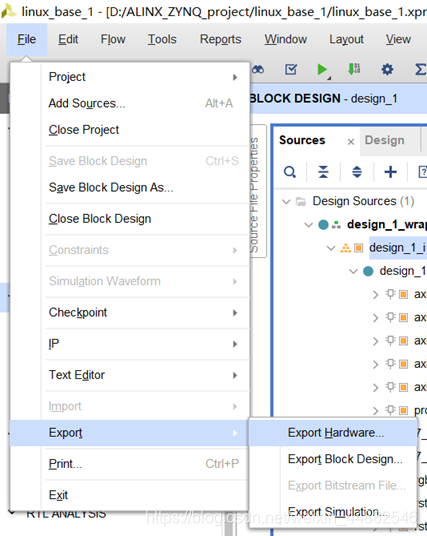

7 在菜单栏“File -> Export -> Export Hardware…”导出硬件信息,这里就包含了 PS 端、PL端的配置信息。

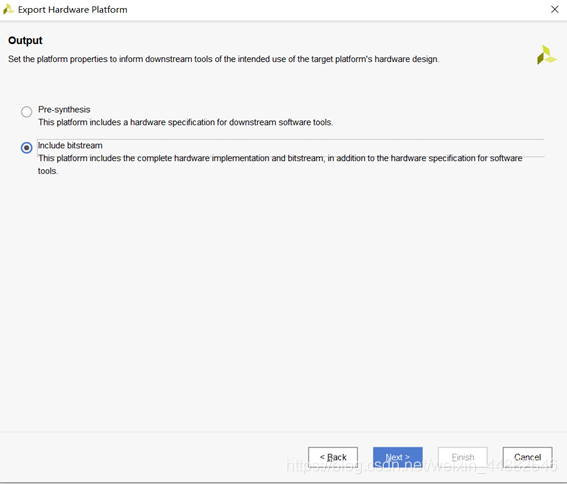

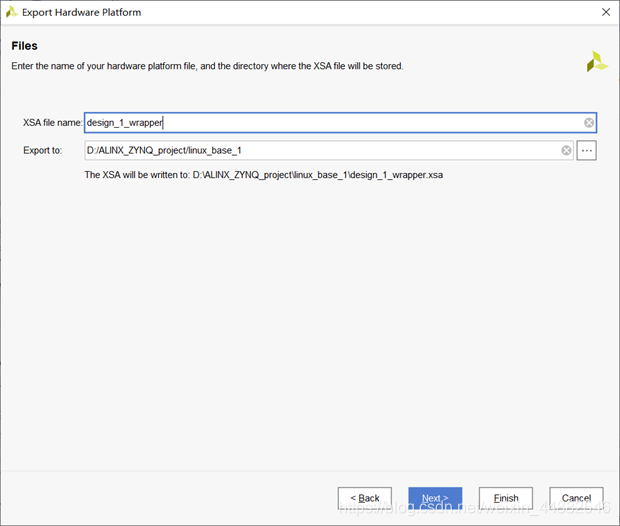

8 在弹出的对话框中点击“OK”,根据工程是否有 PL 参与,选择是否使能“Include bitstream”,导出路径可以自由选择, 这个文件夹可以根据自己的需要在合适的位置新建,不一定要放在vivado工程下面。

此时在保存路径文件夹下可以看到 xsa 文件,这个文件就包含了 Vivado 硬件设计的信息,供软件开发人员使用。

3512

3512

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?