最近有很多网友咨询FPGA DDR4为什么速率总是上不去的问题,发现他们的设计确实很随意,都没有遵守一些手册的基本要求,所以今天和大家一起重新读一读DDR4 design guide,看看哪些要求是一定不能忽略的。

首次设计一款新的芯片或者内存方案时,可能会无从下手。对于内存设计,官方指导首推JEDEC规范,每一代内存推出时,在JEDEC官网均能找到对应的规范文档、各种内存形式的说明文档如DDR4-JESD79、DDR4 SDRAM UDIMM Design Specification以及内存条DEMO等。如果上述资源无法获得,可以查看对应芯片的设计手册,如CPU、FPGA芯片或者DDR颗粒的硬件设计手册、PCB design、datasheet等。

笔者谨以此文抛砖引玉,以Xilinx FPGA为例,对芯片内存部分设计要求进行解析,以指导内存设计。

Xilinx UG583:《UltraScale Architecture PCB Design》这份文档详细介绍了UltraScale平台PCB设计要求,包括电源、各类总线。此文档已分享至网盘,文末有下载链接。

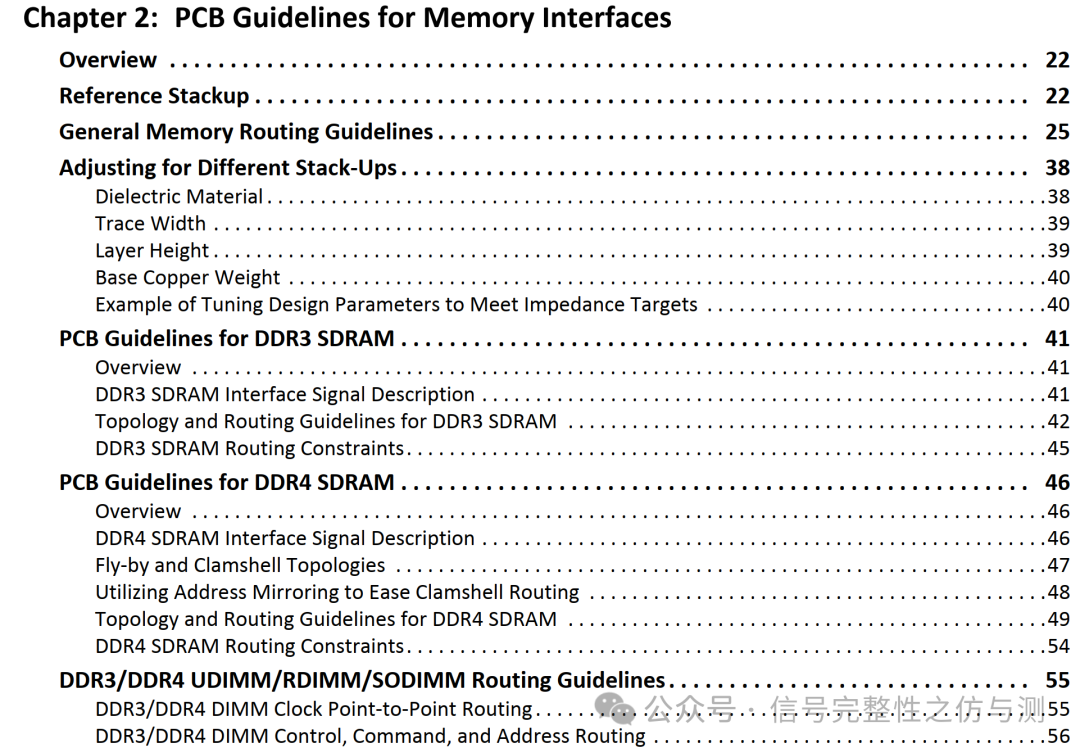

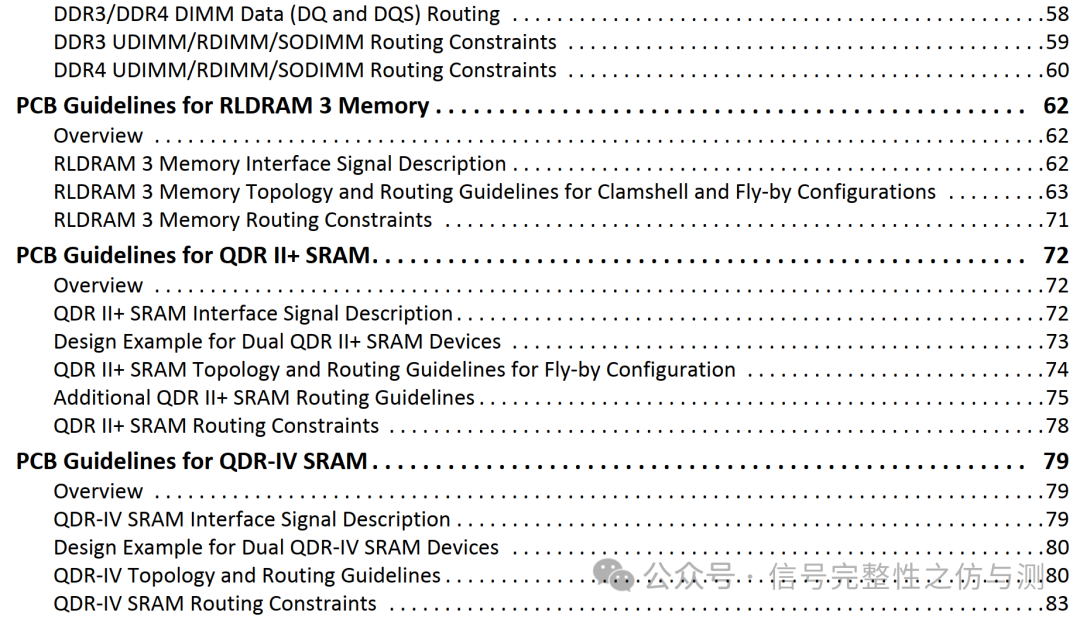

其中第二章为内存相关的内容:

此章节介绍了DDR3/DDR4/RLDRAM3/QDRII+/QDR-IV等多种类型的内存设计。本文以目前最常用的DDR4为例展开。

01 叠层

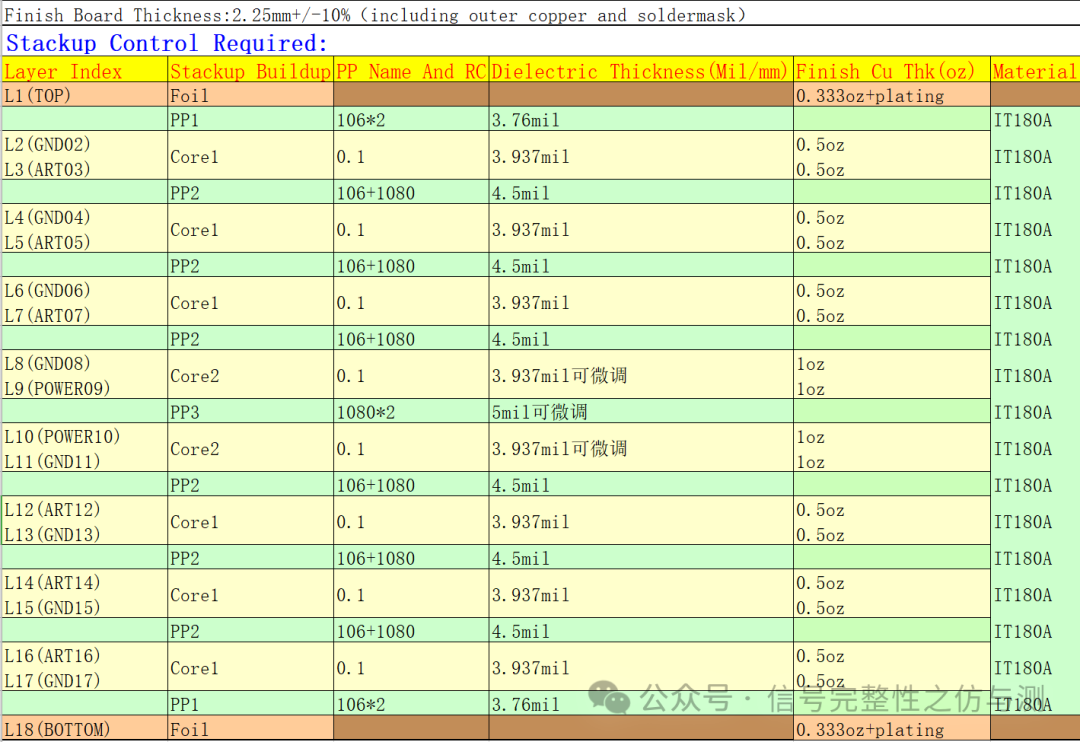

对于有叠层设计经验的工程师而言,根据板厚、层数、板材等要求就可以设计出合适的叠层,如下图这种:

如果不了解如何设计,可以

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

537

537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?