DRAM内存介绍

内存作为计算机系统的关键组件,在诸多领域发挥着不可或缺的作用。从日常使用的电子设备,到推动科技创新的高性能计算场景,内存都在背后提供着关键支持。其主要的应用场景介绍如下:

- 消费电子领域: DDRx/LPDDRx

- 智能手机

:运行各类应用程序(APP)时,内存用于存储 APP 运行过程中的数据、用户操作指令以及系统运行所需的各种临时文件。

- 平板电脑

:同样用于支撑系统和应用程序的运行。在进行多任务处理,如同时打开文档编辑软件、视频播放软件和网页浏览器时,内存会存储各个任务的相关数据,保证不同任务之间能快速切换和协同工作,提升用户的使用体验。

- 个人电脑:

:无论是日常办公使用的办公软件,如 Word、Excel 等,还是进行图形设计、视频剪辑等专业工作的软件,亦或是运行各类游戏,内存都承担着数据存储和交换的重任。

- 智能手机

- 数据中心与云计算领域:DDRx

- 数据中心

:作为海量数据的存储和处理中心,内存用于快速存储和读取大量的数据。在搜索引擎的数据中心,内存会缓存频繁访问的网页数据、索引信息等,加快搜索结果的返回速度。

- 云计算服务

:为众多用户提供虚拟化的计算资源,内存是实现多用户同时在线使用云计算服务的关键。云服务器中的内存为每个用户的虚拟环境分配一定的空间,用于运行用户的应用程序和存储相关数据,使用户能像使用本地计算机一样在云端进行工作和娱乐 。

- 数据中心

- 人工智能与机器学习领域:DDRx/LPDDRx/HBMx

- 训练模型

:在训练深度学习模型,如神经网络时,需要处理海量的训练数据。内存用于存储训练数据、模型参数以及训练过程中的中间计算结果。

- 推理应用

:当模型训练完成后进行推理应用时,内存同样发挥着重要作用。如智能语音助手在识别用户语音指令并进行语义理解时,内存会存储模型的相关数据和识别过程中的临时结果,快速给出相应的回答 。

- 训练模型

- 汽车电子领域:LPDDRx/GDDRx

- 自动驾驶系统

:内存用于存储地图数据、传感器采集的实时数据(如摄像头图像、雷达测距数据等)以及自动驾驶算法运行过程中的中间结果。这些数据的快速存储和读取对于自动驾驶系统做出准确的决策至关重要,如判断车辆行驶路径、避让障碍物等 。

- 车载娱乐系统:LPDDRX/GDDRX

:支持导航、多媒体播放等功能。导航地图数据会存储在内存中,方便快速定位和路径规划;多媒体播放时,音频、视频数据也临时存于内存,保证播放的流畅性。

- 自动驾驶系统

内存应用如此广泛,做好内存的硬件设以及SIPI仿真对电子系统至关重要,接下来的几期我们将介绍内存的一些基础知识以及SIPI关注点。

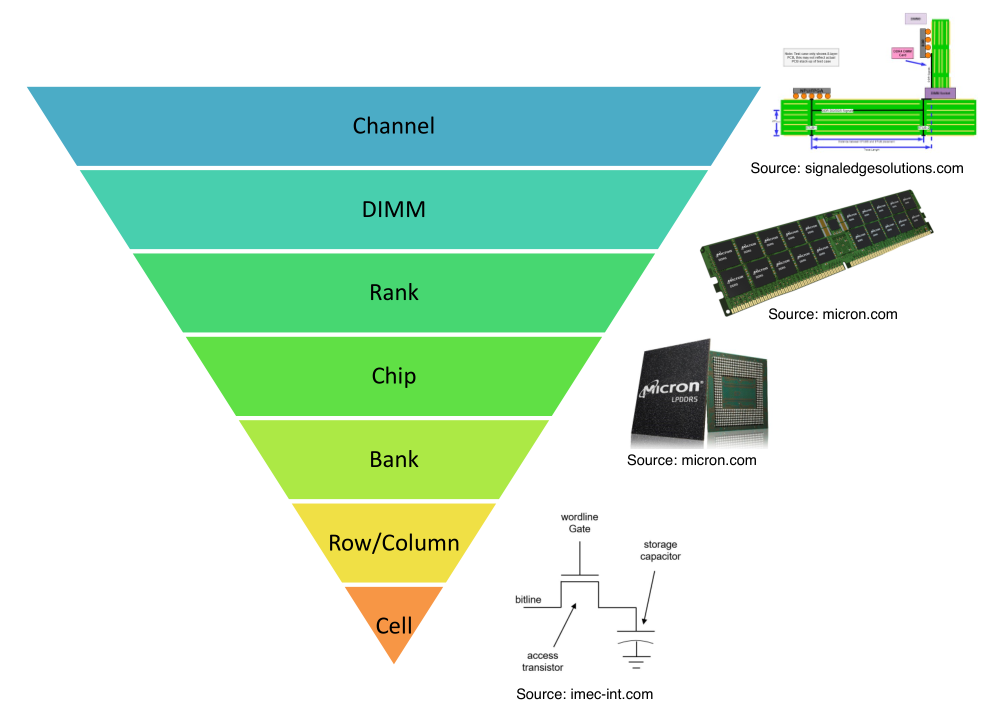

DRAM 内存架构

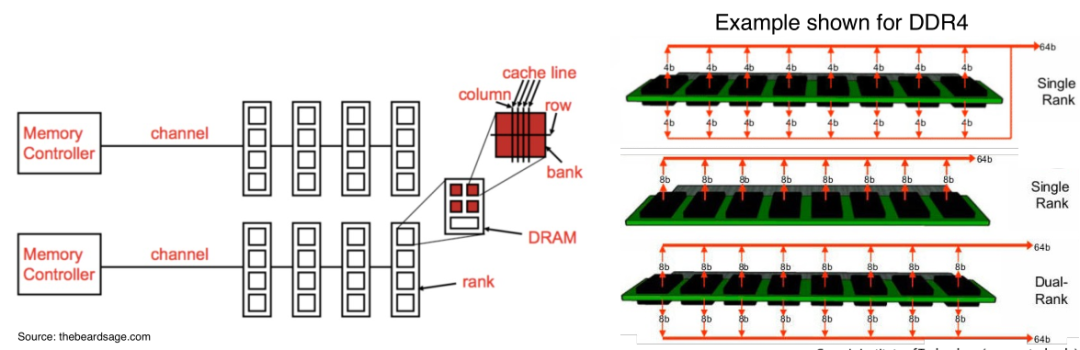

LPDDRx、DDRx、GDDRx和HBMx都使用基于DRAM的技术。下图所示为DRAM的架构解析。

内存的结构从基础的存储单元(cell)到通道(channel),是一个逐步组合和扩展的层级架构,每个层级都有其特定功能,共同保障内存的数据存储和传输。

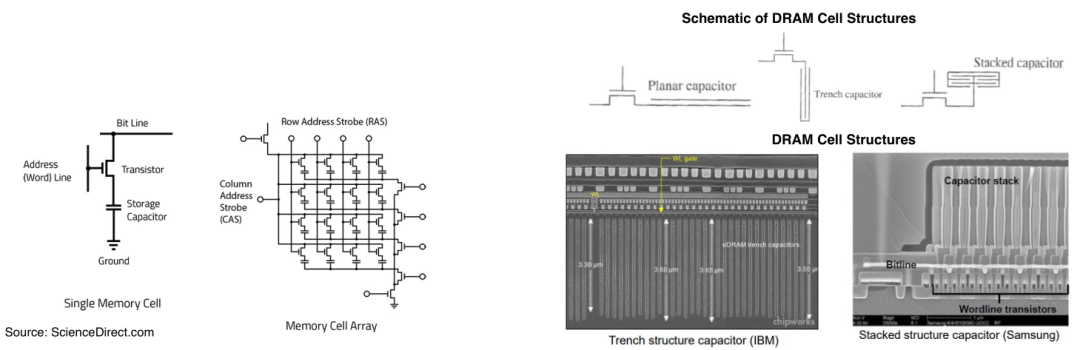

- Cell(存储单元)

:是内存的最基本存储单元,由电容器和晶体管组成。工作原理是利用电容器存储电荷来表示数据,电荷的存在与否分别对应逻辑 “1” 和 “0” 。但由于电容器存在漏电现象,DRAM 需要定期刷新以保持数据。其结构有平面、沟槽和堆叠式电容器等类型,不同结构在性能、集成度上各有优劣,比如堆叠式电容器能提高存储密度。

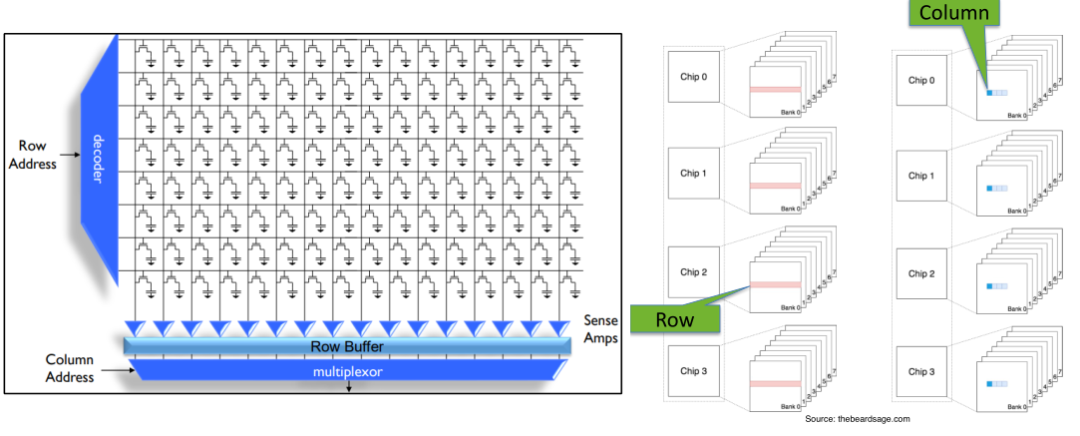

- Row/Column(行 / 列)

:多个存储单元按行和列的形式排列组成存储阵列。行是一组能被同时激活的存储单元,当接收到行激活命令,一行的存储单元会并行工作。列是可独立进行读写操作的最小单元,通过列地址选通(CAS)信号来选择特定列进行数据传输。在进行内存读写时,先通过行地址选通(RAS)信号选中某一行,再用 CAS 信号选择列,从而定位到具体存储单元进行数据操作 。

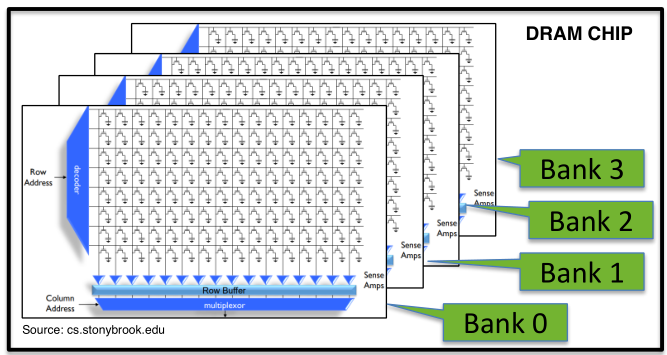

- Bank

:是 DRAM 芯片内独立的存储阵列分区,由多个行和列组成。一般的 DRAM 芯片包含 4、8、16 个甚至更多bank,随着内存密度提升,bank数量会增加,像 DDR5 x4/x8 设备中,16Gb 内存就有 32 个bank。bank可独立进行读写操作,能并行处理不同的内存请求,提升内存整体性能,比如在多任务处理时,不同任务的数据可分别在不同bank中读写 。

- Chip(芯片)

:由多个存储体、行 / 列译码器、数据缓冲器等组成。多个存储体协同工作,通过行 / 列译码器选择具体的行和列,数据缓冲器负责数据的暂存和传输。不同类型的内存芯片在容量、速度等性能指标上有差异,如 GDDR6 芯片更注重高带宽,适用于图形处理,而 LPDDR 系列芯片侧重低功耗,用于移动设备 。

- Rank

:是内存模块中一组协同工作的 DRAM 芯片集合,同一 Rank 内的芯片共享地址和命令总线,但各自提供不同的数据位。以 DDR4 为例,常见的单 Rank 包含 8 个或 9 个 DRAM 芯片(9 个芯片时含 1 个用于 ECC 校验,64 bits of data + 8 bits ECC),这些芯片同时被控制,通过芯片选择(CS_n)信号来确定对哪个 Rank 进行操作 。

下图右图为三个64bit位宽的内存条:(上)用x4的DDR颗粒,正反对贴的16个颗粒组成64bit的单rank内存接口;(中)使用x8的DDR颗粒,8个颗粒组成64bit的单rank内存接口;(下)16个x8的DDR颗粒组成双rank内存接口,需要通过CS_n片选对相应rank进行操作。

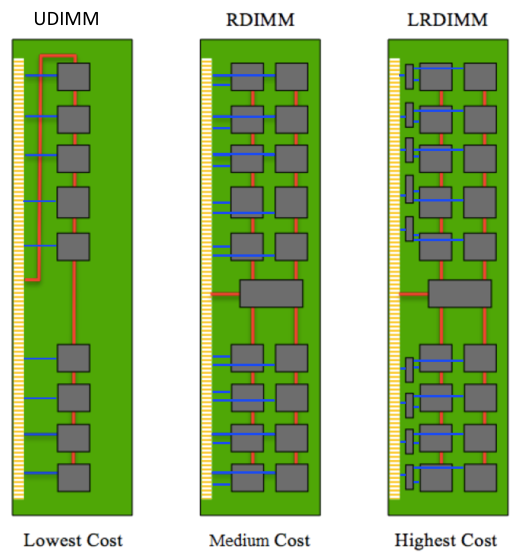

- DIMM(双列直插式内存模块)

:将多个 Rank 的芯片集成在一块印刷电路板上形成 DIMM(也就是我们通常所说的内存条)。常见的有 UDIMM(无缓冲双列直插式内存模块)、RDIMM(寄存器缓冲双列直插式内存模块)和 LRDIMM(负载降低缓冲数据双列直插式内存模块) 。不同类型的 DIMM 在功能和适用场景上有区别,UDIMM 成本低但负载能力有限;RDIMM 和 LRDIMM 适用于高容量、高数据速率系统,能降低信号干扰,但会增加系统成本、延迟和功耗。

DDR3 和 DDR4 支持三种主要 DIMM 类型:

o 无缓冲 DIMM (UDIMM):CK、C/A信号负载数量多,SI设计难度大。

o RDIMM:用于 CK、ADDR、CMD、CTRL 网络带寄存器缓冲,有效降低负载数量,降低SI设计难度。

o LRDIMM:除了 CK、ADDR、CMD、CTRL 网络,DQ网络也带有减载缓冲,降低多rank内存条中DQ信号SI设计难度。

具有更大内存容量和更高数据速率的系统需要RDIMMs或LRDIMMs来克服额外的通道负载并保持1N的时序。

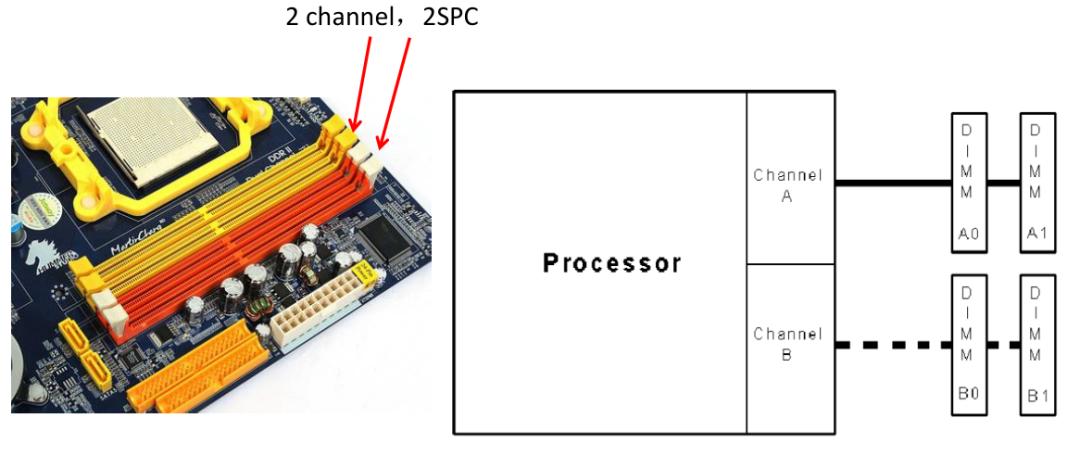

- Channel

:是内存控制器与 DIMM 之间的数据传输通路。一个内存控制器可连接多个通道,如常见的双通道、四通道技术。每个通道可独立传输数据,增加通道数量能提升内存带宽,提高数据传输效率 。在多通道系统中,内存控制器会根据负载情况合理分配数据到不同通道,实现并行传输,提升系统整体性能 。

807

807

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?