上篇文章有说过,通常情况下,我们认为UDIMM(无缓冲双列直插式内存模块)、SODIMM(小型双列直插式内存模块)以及RDIMM(寄存式双列直插式内存模块)的内存设计相对较为直观,因此在这一层面上的设计难度相对较低。主板端的走线设计只需遵循一些通用的电气和布线规则,便能够较好地支持这些内存模块的工作。但对于一些新的设计者而言,不能充分地考虑SI的影响,对于高速信号回流/反射等影响因素没有认知,就会犯一些低级错误。

以下这个case涉及到DDR4 UDIMM 内存条降速问题,我们可以从一个一眼就能看出问题的case中来定量的看一下犯这些低级错误影响和代价是什么。

01 问题描述

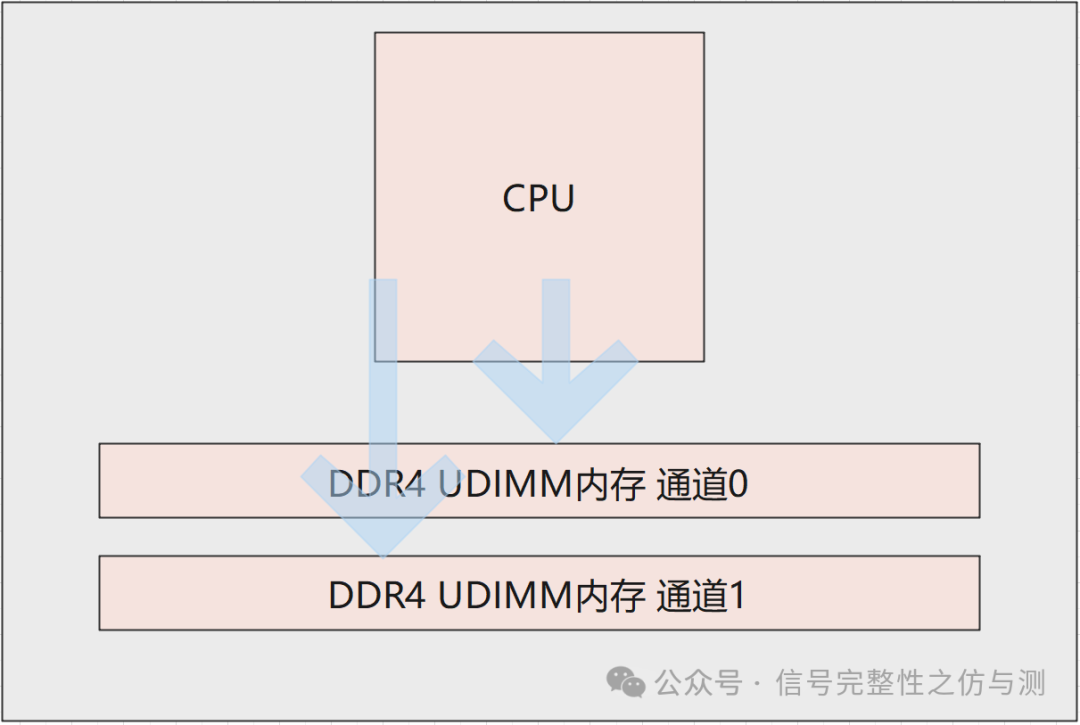

某UDIMM主板,使用两条DDR4内存条。内存速率只能到2666,在3200速率下会卡系统,十次开机,大概两次可以正常进入系统。

信号拓扑如下图所示:

02 问题分析

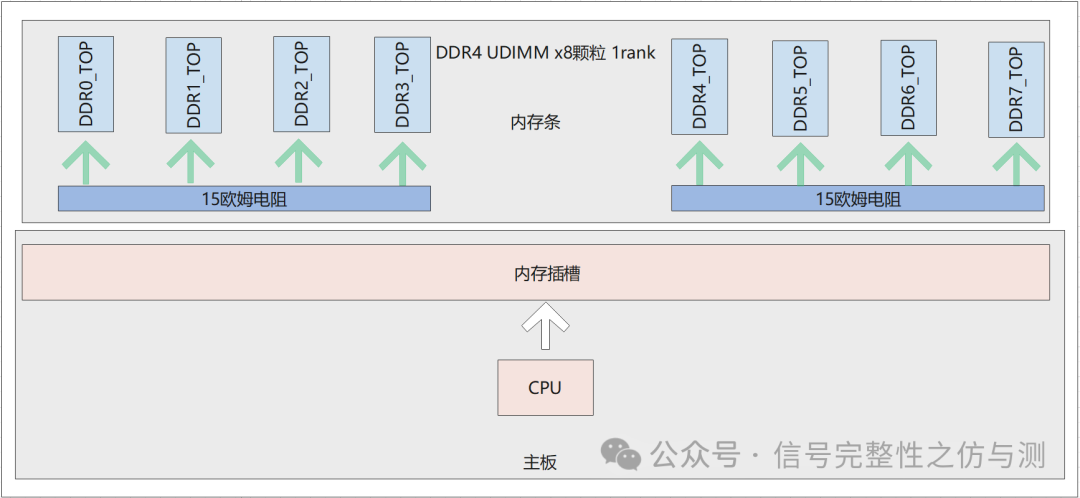

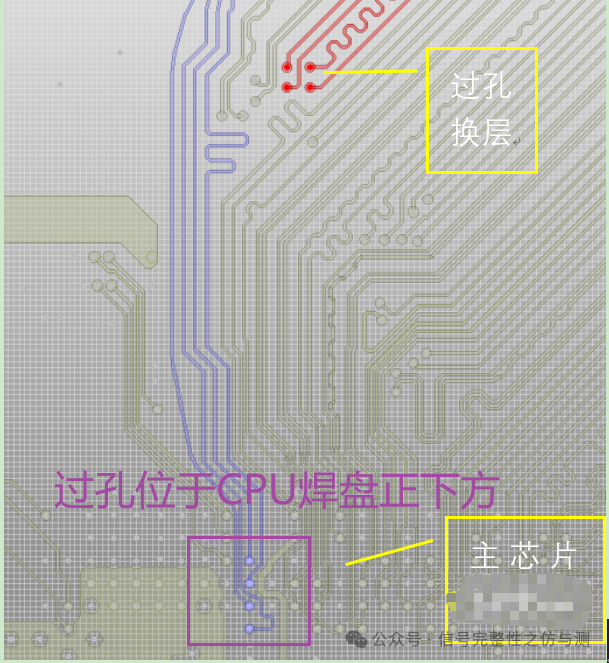

查看主板内存部分走线,发现如下一组Byte信号(DQ0-DQ7),一部分信号从芯片焊盘处直接打孔到内层走线,一部分信号从表层走出一段走线后再通过过孔换到内层走线。下图DQ-0/1/4/5紫色信号,从芯片焊盘处直接打孔;DQ-2/3/6/7红色信号,从表层走出一段走线后再通过过孔换到内层。问题很可能就出现在这里,至于有多大影响,则需要通过仿真去量化。

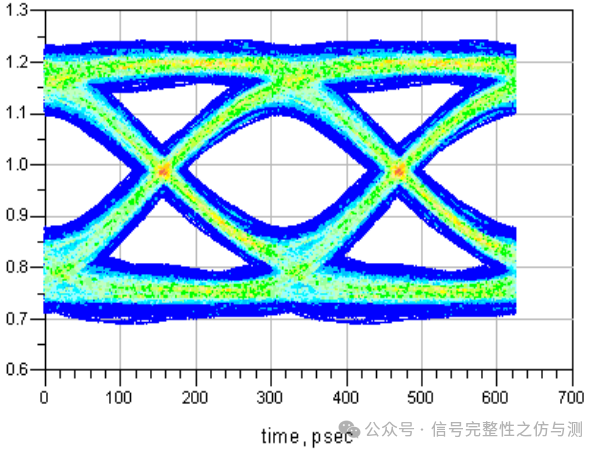

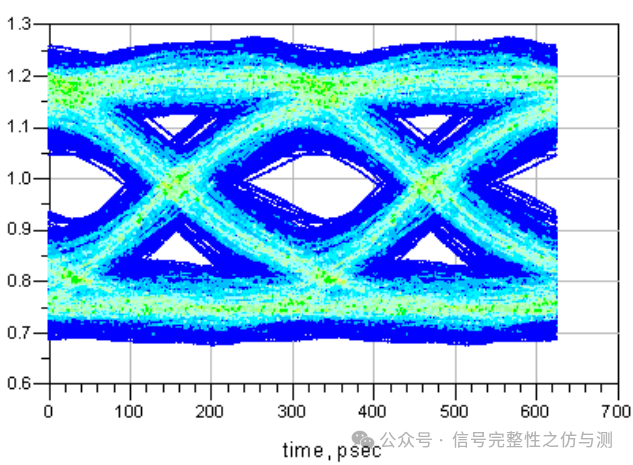

分别对上述两类信号基于3200速率仿真,眼图如下:

|

|

|

| DQ-0/1/4/5眼图 |

DQ-2/3/6/7眼图 |

仿真结果显示,同一组Byte数据走线,不同走线方式结果差异明显。DQ-2/3/6/7信号质量很差,抖动、眼宽眼高都受到极大影响。

使用示波器测试DQ信号质量,分别选择DQ1/DQ3进行测试:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2629

2629

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?