一、参考文章

转!!!

关于cache的原理和使用,看着两篇文章就够了!!

1、 STM32H7的Cache和MPU_qlexcel的专栏-CSDN博客

2、 例说STM32F7高速缓存——Cache一致性问题(一)_人人都懂物联网-CSDN博客

二、针对第一篇文章做一点补充

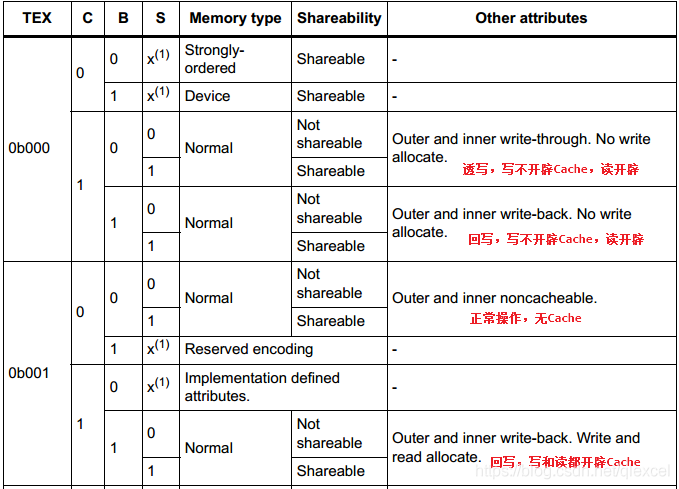

1)、TEX、C、B、S:H7支持4种Cache策略,这几位就是用来控制这个MPU保护区域使用哪一种。

S位用于解决多总线或者多核访问的共享问题,一般不要开启;

TEX = 000表示读开辟,RA; TEX= 001表示读写开辟RWA;

C表示缓存使能标志--cacheable,1表示使能;

B表示bufferable,1表示回写,0表示透写。

1475

1475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?