STM32H7系列芯片集成了L1高速缓存,即L1 CACHE,包括D-CACHE和I-CACHE。提升CPU访问数据或指令的速度,改善MCU的性能。关于STM32H7 L1 CACHE的应用,有个数据一致性问题需要注意。

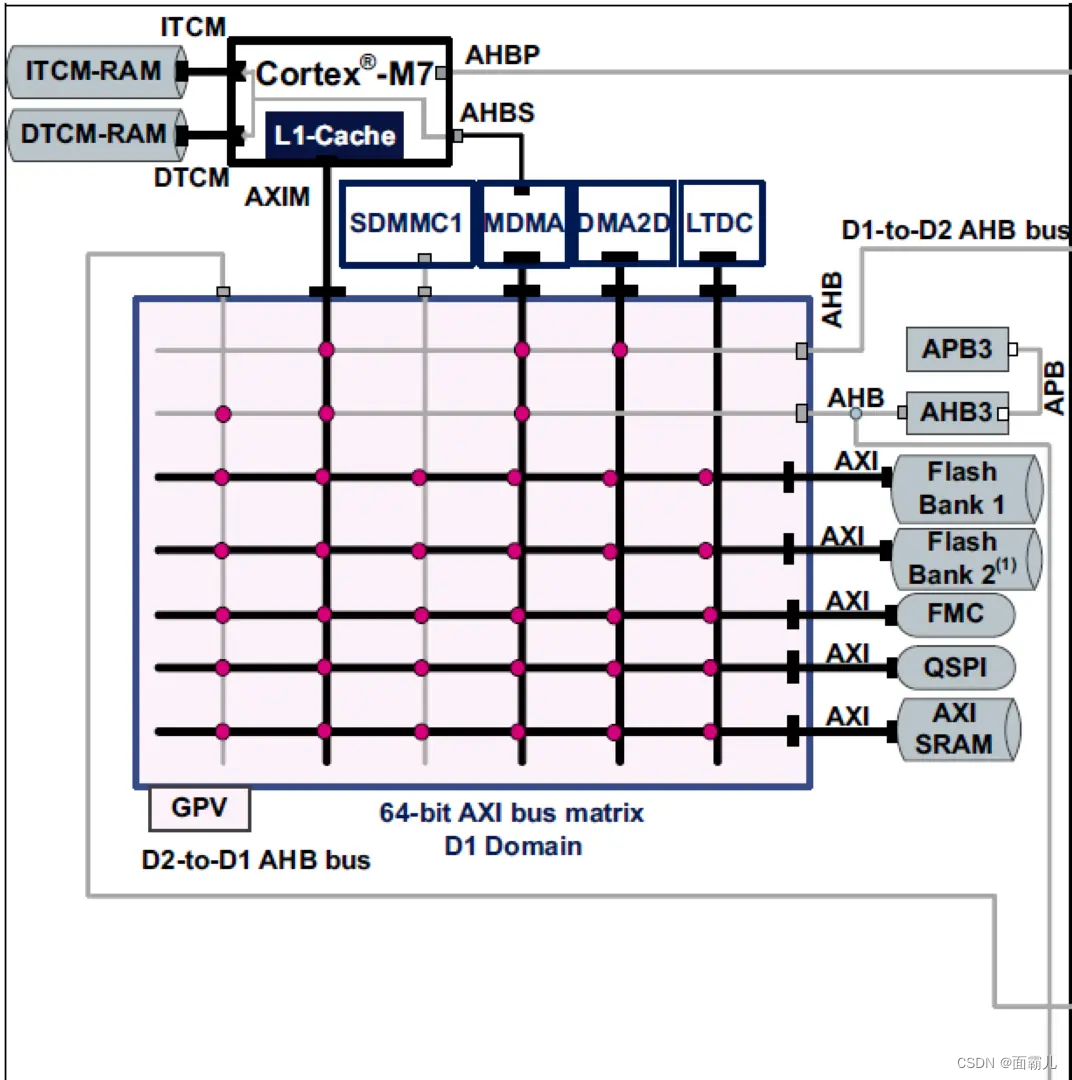

1、对于STM32H7来说,只有经过AXI总线接口访问时才用到L1 CACHE。换句话,通过其它总线【TCM/AHBP/AHBS】做数据或指令访问时是不涉及到L1 CACHE的。

2、回写【WRITE BACK】:在写数据时,只是把数据写进D-CACHE而未写入二级存储器,并将缓存行里的数据标识为DIRTY,直到执行CACHE的清除操作才将D-CACHE里的内容写进二级存储器。

3、透写【WRITE THROUGH】:在写数据操作时同时将数据写入D-CACHE和二级存储器。这对于保持数据的一致性有好处,代码编写也相对简单。不过它需要消耗更多的写数据时间。当然,下次访问相同内容时还是可以直接从缓存里读取。跟回写相比,算是一种折衷处理办法。

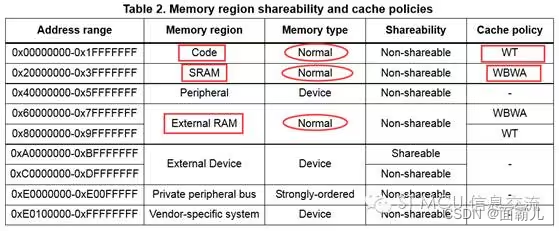

4、STM32H7片内外各个存储单元的存储属性是通过MPU来配置的。在芯片复位之后,MPU是默认关闭的,此时各存储单元的存储属性遵照如下的默认配置。

那什么时候会发生数据一致性问题?

当有CPU和其它主设备【如DMA】共同访问某可缓存的二级存储器比方SRAM1,同时该存储器又具有回写属性,此时就可能发生数据一致性问题。因为该存储器的回写属性,导致通过CPU欲写入存储器的数据只是缓冲在CACHE里,而没有及时写入存储器。如果此时DMA访问该二级存储器的话,读到的数据可能跟预期不一致。

为了避免数据不一致的问题,我们需要做D-CACHE维护操作。一般有如下四种方法:

1、当对一个可缓存的二级存储器做了写数据操作之后,通过软件对D-CACHE进行清除操作,即运行SCB_CleanDCache()。这样将CACHE里的缓存内容写回到二级存储器,比如把那些DIRTY CACHE行的数据写进SRAM1。

2、通过MPU调整可缓存存储器的存储属性,将其CACHE使用方式改为透写模式。这样保证每次写入CACHE里的内容也同时写入二级存储器,比如写进SRAM1。

3、通过MPU调整可缓存存储器的存储属性,将其共享属性改为可共享的【SHAREABLE】。此后该二级存储器将变为不可缓存。

4、通过配置CACR寄存器中的D-CACHE位,强制将所有写操作配置为透写属性。

当然,跟上面描述相对应的还有一种情形。那就是DMA更新了可缓存存储器比如SRAM1的数据后,CPU再去读SRAM1,此时也会发生数据不一致的问题。因为CPU此时读的数据还是之前CACHE里的旧数据。为了避免这个问题,保证数据的一致,就得在CPU读SRAM1之前通过软件执行CACHE失效操作,这样保证CPU直接从二级存储器比方SRAM1读取数据。

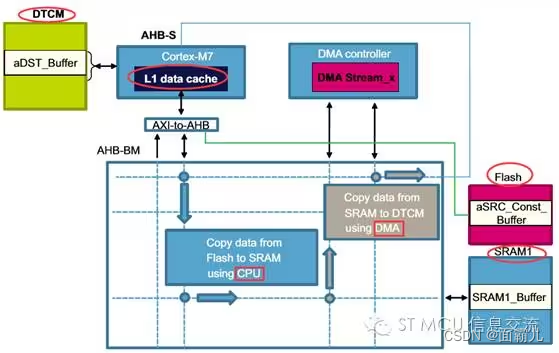

下面有个关于数据一致性的实例供大家思考。

首先CPU从片上FLASH存储块aSRC_Const_Buffer的128字节常量数据拷贝到SRAM1里的一个名为pBuffer的缓存区。

然后CPU配置并使能DMA执行从内存到内存的传输,将SRAM1里pBuffer缓存区的数据传输到DTCM RAM的另一个aDST_Buffer缓存区。

最后,CPU将aDST_Buffer缓存区的数据与flash存储块aSRC_Const_Buffer的常量数据进行比较是否一致。

小结:对于STM32H7系列MCU来说,可能发生数据一致性问题需要的几个因素:

1、有CPU和DMA参与数据访问;

2、有被CPU和DMA共同访问的可缓存的带回写属性的物理存储块;

3、开启了D-CACHE;

程序采用串口+超时中断+DMA接收不定长数据,串口变量使用AXI_SRAM存储空间,开启MPU并把AXI内存区域设置为回写模式(Write-Back,Read-Allocate,Write-Allocate),

当串口接收完一帧数据并进入超时中断后,由于DCache的存在,为防止DMA未及时写入到相应内存中,又为了防止后续读取串口数据存在和实际数据不一致的隐患,需要在读取前串口数据进行数据一致性处理。

作者:ST MCU信息交流 出处:微信公众号

2232

2232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?