一.差分对约束参数主要有如下:

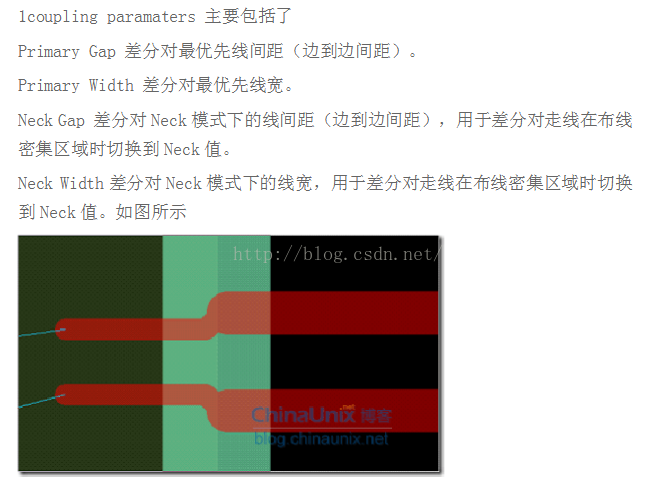

coupling paramaters

主要包括了

coupling paramaters

主要包括了

coupling paramaters

主要包括了

coupling paramaters

主要包括了

需要注意的是在物理

(

physical

)

约束中同样可以设置差分规则,

但是电气规则

约束在布线时更优先,

同时电气规则可以设置更多的约束,

推荐在电气规则中设

置差分走线的约束。

一.差分对约束参数主要有如下:

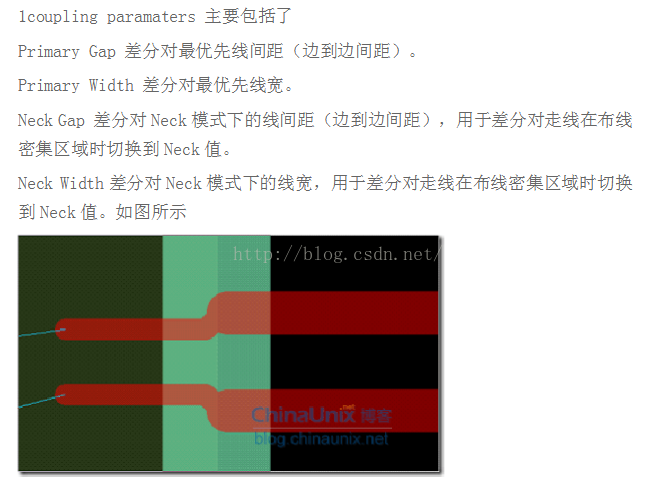

coupling paramaters

主要包括了

coupling paramaters

主要包括了

coupling paramaters

主要包括了

coupling paramaters

主要包括了

需要注意的是在物理

(

physical

)

约束中同样可以设置差分规则,

但是电气规则

约束在布线时更优先,

同时电气规则可以设置更多的约束,

推荐在电气规则中设

置差分走线的约束。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?