第一部分:前言

因为刚拿到zedboard这块板子,所以一直在尝试先跑上一个例程。这篇博客https://blog.csdn.net/weixin_42639919/article/details/81130581的整个流程相当详细,而且在vivado2018.2上尝试后确实是可以正常运行的。但有几个点想补充一下,也是在尝试的过程中碰到的问题。

第二部分:尝试

2.1 vivado2018在界面上相对于之前的版本有些不一样,但基本的选项还是一样的。

2.2 在IP diagram连线的时候,注意按照步骤中,连接GPIO至led引脚,这一点要注意,不要选择默认的选项

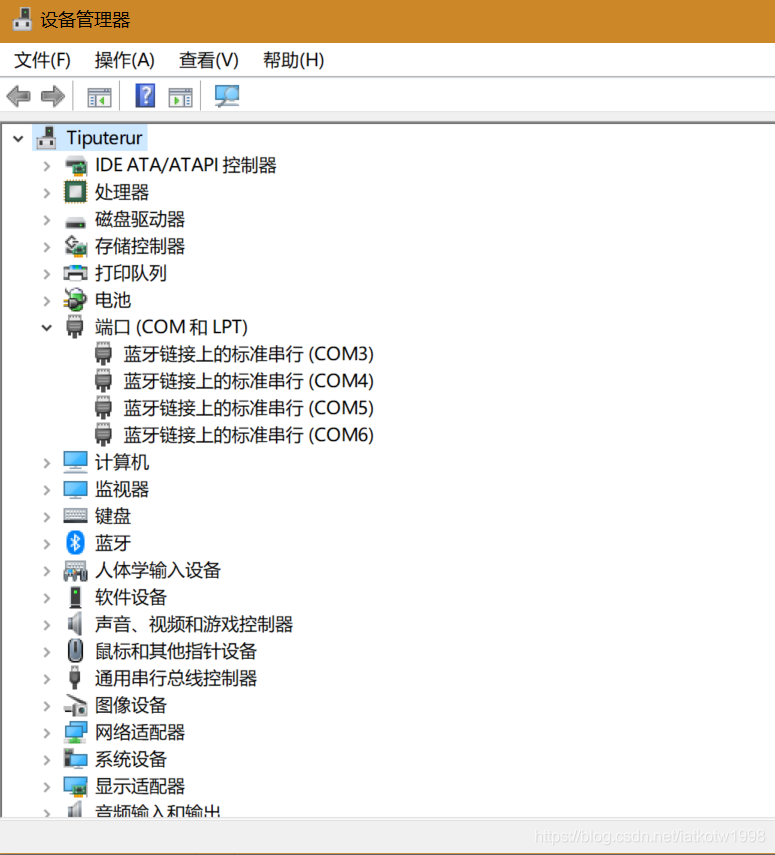

2.3 之前的很多教程里,都没有提到hardware manager这一过程,都是直接让看设备管理器里的端口配置。但是很遗憾,我的电脑无论如何都显示不出有探测到zedboard设备,还是之前做项目时添加的几个蓝牙com。所以检测有没有连上还是要看hardware manager。

然后,别人的博客也说了,如果板子的status是closed,要右键,然后open

2.4 uart to usb是可以在设备管理器的端口中被发现的,而且一般会提示你安装相应的驱动,如果没有相应提示,建议换一条数据线试试。

第三部分:补充与理解

做这么个例程,说白了还是想要借助来理解整个zynq7 ip的使用过程和流程。但我也才刚开始看,很多理解和补充可能不到位,仅供参考,之后也就慢慢学,慢慢完善咯。

参考的资料有《vivado从此开始》、《Xilinx Zynq-7000嵌入式系统设计与实现基于ARM Cortex-A9双核处理器和Vivado的设计方法》。对应的资源下载https://download.csdn.net/download/iatkotw1998/10840227。抱歉收了一个积分。

3.1 理解VIVADO和SDK的关系:一个最直观上的感受便是VIVADO负责硬件部分的设计,然后导入至SDK中进行软件部分的设置。这和以前使用的系列单片机是不一样的,当然,这也归功于zynq架构的设计理念。其次,很多之前的教程都还是基于像是PlanAhead、XPS或者ISE,近些年VIVADO的教程才开始多了起来,但是VIVADO是一个大综合,把几乎所有的流程功能集成到一个框架下,不用四处切换工具。

3.2 国内的原创稿比例还是比较少,像如果直接搜vivado+zedboard之流水灯例程,几乎全是一样的,转过来转过去,流程多,理解少。反正也都是在入门,之后可能会写几篇有关自己对zynq和vivado开发工具的理解和学习笔记。这一篇还是回到结合例子理解流程的话题上来。

3.3 zynq这个ip的使用流程与传统的FPGA在VIVADO的设计流程很不一样,我们甚至可以在使用zynq架构的板子时,一句HDL代码都不用写,直接上ip integrator部分就行。我们知道,zynq架构有PS和PL两个重要的组成部分。二者之间的互联通过AXI(AMBA协议中的的一种规范)总线。还有AXI4-Lite功能和AXI4-Stream功能,前者专用与和原件内的控制寄存器进行通信,后者则用于连接希望交换数据的元件,如果不是很清楚的话可以先看一看这个博客进行学习(https://www.cnblogs.com/milinker/p/6474706.html)。说到这里,先上来这个例程的整体框图,图片转自博客http://blog.chinaaet.com/cuter521/p/35978,非常具有原创性的一个博主。

本文详细记录了使用Vivado 2018.2在Zedboard上实现流水灯例程的过程,包括硬件连接、IP配置、硬件管理等关键步骤。强调了在IP Integrator中正确配置GPIO与LED的连接,并指出Vivado与SDK在硬件和软件设计中的分工。此外,讨论了Zynq架构中PS和PL的交互,AXI GPIO IP的使用及其与传统FPGA设计的区别,以及Processor System Reset模块的作用。

本文详细记录了使用Vivado 2018.2在Zedboard上实现流水灯例程的过程,包括硬件连接、IP配置、硬件管理等关键步骤。强调了在IP Integrator中正确配置GPIO与LED的连接,并指出Vivado与SDK在硬件和软件设计中的分工。此外,讨论了Zynq架构中PS和PL的交互,AXI GPIO IP的使用及其与传统FPGA设计的区别,以及Processor System Reset模块的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

258

258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?