由于疫情STM32被炒上天了。原来二十元芯片炒到几百元,还的等货。

原来板子用的STM32:这片子被吵到300元还供货不稳定。采用雅特力雅特力AT32F403ZGT6取代STM32F103VET6完全OK,感谢国产!使得产品更稳定。

AT32F403ZGT6取代STM32F103VET6相同点:

1) 管脚定义PIN to PIN 兼容:相同封装管脚定义相同。为扩增的外设作管脚复用定义延伸,电源 VSS 晶振都相同。更换上去就可以了。

2) 寻址空间:内存与寄存器逻辑地址相同。扩增的外设占用SXX32保留空间

3) 编译工具:完全相同,例如Keil, IAR

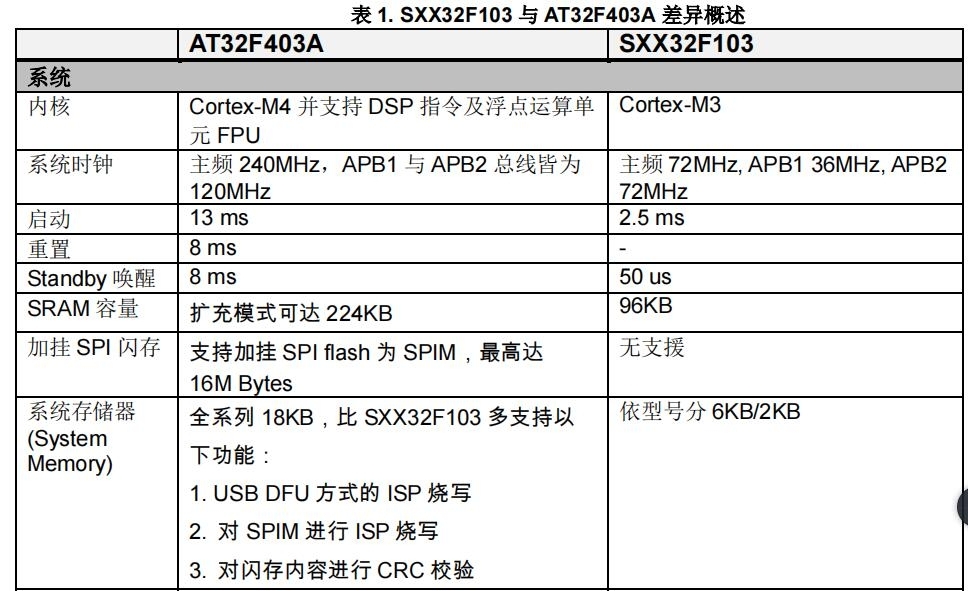

不同点:AT32F403ZGT6比STM32F103VET6更高,更快,更强!主频240M,所有,哪些对时序敏感的要做延时兼容。

替换步骤:

1,步骤一:解焊SXX32F103,换成AT32F403对应型号

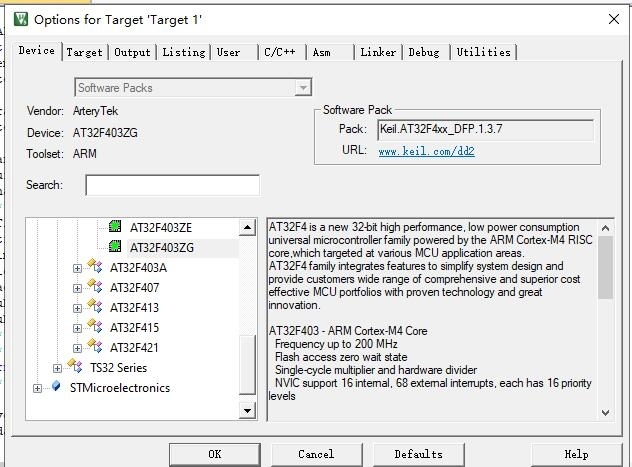

2,keiL添加:Keil.AT32F4xx_DFP.1.3.7.pack

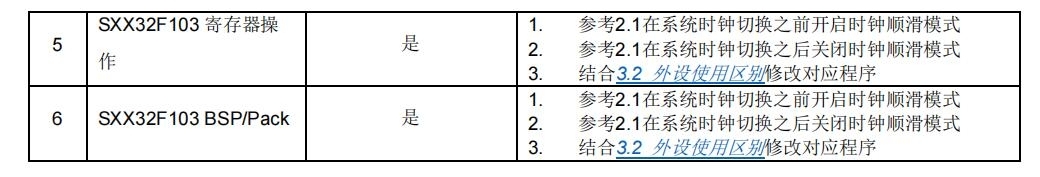

3,startup_stm32f10x_atf403a.s替换 AT32标准库(BSP)模板建立 参见附件文档 “AT32F4xx标准库BSP&Pack应用指南”

完美替换!

AT32F403A 兼容性解析:

时钟处理:系统时钟源采用HSE, 为了确保量产稳定性, 请修改时钟初始化源代码, 方法如下:打开 system_at32f4xx.c 找到当前的系统时钟频率配置函数,如 168MHz 函数:static void SetSysClockTo168(void)然后按如下方式配置自动顺滑频率切换功能。

复制

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

*((unsigned int *)0x40021054) |= (0x30);// 开启自动滑顺频率切换功能

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{ }

//此时不需再等待 200us

*((unsigned int *)0x40021054) &=~ (0x30); //关闭自动滑顺频率切换功能

BSP工程替换:

内部温度传感器存在差异:

描述:AT32F403A 温度传感器为正温度系数,SXX32F103 为负温度系数

解决方法:

按照数据手册中的值并利用下列公式得出温度:

温度(℃) = {(V25 - VSENSE) / Avg_Slope} + 25

这里:V25 = VSENSE 在 25°C 时的数值

Avg_Slope = 温度与 VSENSE 曲线的平均斜率 (单位为 mV/℃).

V25 和 Avg_Slope 必须根据数据手册中的典型值参与运算, AT32F403A 与 SXX32F103 不同。

ADC 要求较长的采样时间

描述:ADC 采样电路为适应采样率提升至 2Msps,内部等效 RADC 和 CADC值较大,要求较长的采样时

间。特别在 ADC 输入源阻抗较大时,需满足足够的采样时间以获得准确的转换数据并消除不同

ADC 输入通道转换时的 cross-talk。

解决方法:

使用时若遇到转换值不如预期,可先尝试设置采样时间至最大 239.5 个 ADC 时钟,再逐步减小

采样时间至合适设置。若可接受较长采样间隔,在不同通道转换间插入 VREFINT 转换也有让转换

数据准确的效果

AT32F4xx标准库BSP&Pack应用指南.pdf (1013.81 KB, 下载次数: 26)

---------------------

作者:abner_ma

链接:https://bbs.21ic.com/icview-3161408-1-1.html

来源:21ic.com

此文章来自于21ic网站,著作权归21ic所有,未经允许禁止转载。

5685

5685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?