CAN数据帧格式

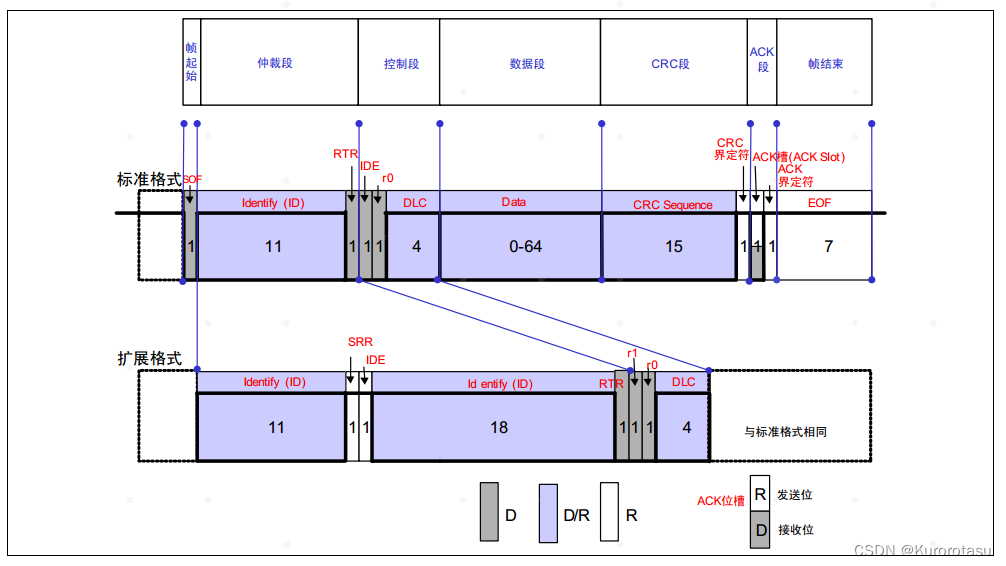

CAN总线的数据帧有标准帧和扩展帧两种格式,区别在于标准帧具有 11-bit 的帧ID,扩展帧具有 29-bit 的帧ID;

CAN数据帧由以下七个段组成:

- 1、帧起始,又叫SOF(Start of Frame):帧起始位,表示一帧的开始;

- 2、仲裁段:决定该帧在总线传输上的优先级的数据段,根据仲裁段ID码长度的不同,分为标准帧(CAN 2.0A)和扩展帧(CAN 2.0B);

- 3、控制段:表示数据的字节数及保留位的段;

- 4、数据段:数据的内容,可发送0~8个字节的数据;

- 5、CRC段:检查帧的传输错误的段;

- 6、ACK段:表示确认正常接收的段;

- 7、帧结束,又叫EOF(End of Frame):表示数据帧结束的段;

具体这七个段在标准帧和扩展帧当中的分布如下图:

对上图做以下说明:

- 1、图中各个段中的数字代表这一段所占的 bit 数,例如标准格式帧的ID部分占 11-bit 对应图中的 11;

- 2、数据段是不定长的,因为一个CAN数据帧可以在数据段携带至多 8-byte 的数据,所以这部分的空间所占位的大小为 0~64-bit;

- 3、在标准格式帧中的r0和扩展格式帧中的 r1、r0 为保留位,一般为 0 ;

- 4、在标准格式帧中的IDE位表示标识符扩展位(Identifier Extension Bit)。它指示了标识符是标准标识符(11位)还是扩展标识符(29位)。当IDE位为0时,表示标识符为标准标识符,即11位;当IDE位为1时,表示标识符为扩展标识符,即29位。这个位的值会影响到CAN数据帧的标识符的长度和格式;

- 5、在扩展格式帧中的SRR位与第4点的IDE相同,可以理解为在扩展格式帧中的IDE位,名称不同,含义一致;

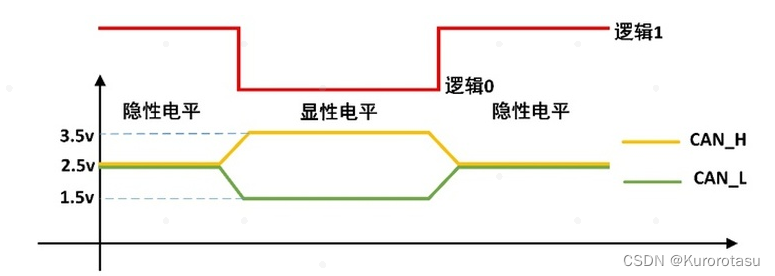

CAN总线信号说明

对CAN信号在CAN总线上的表现形式做简单介绍:

- 完整的CAN电路是由CAN控制器和CAN收发器组成的,二者之间一般通过TTL电平的收发信号(CAN_RX、CAN_TX)连接,由CAN收发器将CAN_TX的TTL信号转换为CAN规范差分信号输出(CAN_H、CAN_L),同时接收差分线上的实际信号并转换为TTL信号输出到CAN_RX管脚上;

- 当CAN_H与CAN_L存在差值时,被认为是一个显性电平,视作逻辑0;反之,被认为是一个隐性电平,视作逻辑1;

CAN波形实例

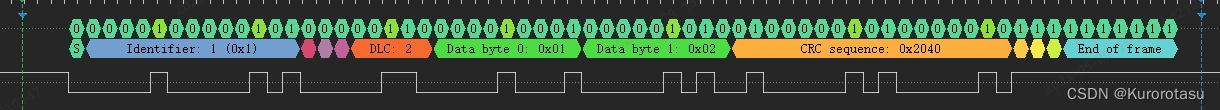

结合具体的逻辑分析仪波形和示波器实测波形来分析一帧标准格式帧,以及对比的问题帧数据;

使用 STM32F3Discovery开发板与CAN收发器 对接 FPGA仿真的CAN设备;

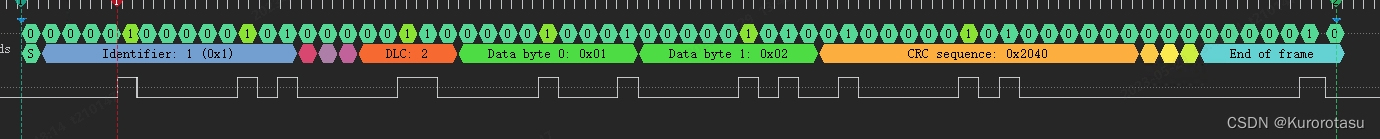

发送的是:标准数据帧---帧ID 0x1---帧长 2---数据 0x1 0x2

ST to FPGA——FPGA能够正常接收到ST设备发送来的帧数据

逻辑分析仪结果:

示波器实测波形:

根据逻辑分析仪的结果,我们按段将数据帧拆解:

0 ||

SOF,一个显性位代表帧起始;

0000[1]00000[1]01 ||

仲裁段的ID部分,这里的数据表明这个数据帧的ID为0x1

0 ||

仲裁段的RTR部分,RTR位表示远程传输请求位(Remote Transmission Request Bit)。它用于指示发送的帧是否为远程帧请求。当RTR位为1时,表示这是一个远程帧请求。远程帧请求是用于请求另一台CAN节点发送一个数据帧的帧类型。当RTR位为0时,表示这是一个数据帧;这里的数据为0,说明为一帧数据帧;

0 ||

控制段的IDE部分,这里的值为0,表示当前帧为标准格式帧;

0 ||

控制段的保留位

00[1]10 ||

控制段的DLC部分,表示后面数据段的数据长度,虽然有四位,但是最大只能是1000,也就是表示8个byte的数据长度;

0000[1]0001 ||

数据段的第一个数据,这里的值为0x1;

00000[1]010 ||

数据段的第二个数据,这里的值为0x2;

0100000[1]0100000[1]0 ||

CRC段,是一个15-bit的数据,根据的是标准的CRC-16/XMODEM算法

101 ||

ACK段,这三位分别代表:CRC界定符,ACK槽(ACK slot),ACK界定符;可以理解为CRC结束标志,接收机的ACK应答位和ACK结束标志,如果接收机确认收到这个帧,那么ACK槽这一位就由接收机返回显性信号;

在逻辑分析仪的结果当中将ACK槽这一位解析为了1,是因为两边CAN收发器的电平标准不同,逻分的电压阈值没法兼顾二者的高低电平点,参考示波器的实际波形(最后一个小的显性信号),这里应该是一个0;

1111111 ||

EOF,七个连续的隐性信号表示帧结束;

注意:当CAN总线信号连续输出5个相同的位,则需要插入一个反码位 ,如连续输出5个0则需要插入一个1,但这个1在读数时要去掉,如上述数据帧拆解当中的[1],就是补位,在实际数据解析当中要忽略;这是CAN总线协议的位填充机制,它的作用是:CAN网络同步需要足够多的上升沿;确保数据帧不会被当作错误帧(由6个连续的显性或隐性位组成)、确保正确识别帧结束标志(7个连续隐性位);

在逻分的数据解码结果当中也可以看到,补位的数据标识颜色与其他数据不同

FPGA to ST——ST不能接收到FPGA设备发送来的帧数据

逻辑分析仪结果:

示波器实测波形:

可以对比看到在CRC段出现了连续6个显性位0,没有正常补位1,这样就会被对端设备识别为错误帧,所以没有去接收;

文章详细介绍了CAN数据帧的结构,包括标准帧和扩展帧的区别,帧的七个组成部分如SOF、仲裁段、控制段、数据段、CRC段、ACK段和EOF。此外,还提到了CAN总线信号在CAN_H和CAN_L线上的表现形式,以及如何通过逻辑分析仪和示波器解析波形。通过一个STM32F3Discovery发送数据到FPGA的实例,展示了正确和错误帧的数据波形,强调了连续相同位的位填充机制和CRC的重要性。

文章详细介绍了CAN数据帧的结构,包括标准帧和扩展帧的区别,帧的七个组成部分如SOF、仲裁段、控制段、数据段、CRC段、ACK段和EOF。此外,还提到了CAN总线信号在CAN_H和CAN_L线上的表现形式,以及如何通过逻辑分析仪和示波器解析波形。通过一个STM32F3Discovery发送数据到FPGA的实例,展示了正确和错误帧的数据波形,强调了连续相同位的位填充机制和CRC的重要性。

1717

1717

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?