FPGA内同步时序电路的运行时钟,受到这样一些(包括但不限于)因素的影响,不可避免的具有周期间抖动(Cycle-to-Cycle Jitter):

- 电源噪声;

- FPGA内部时钟网络的复杂线路连接引起信号完整性问题;

- FPGA内部时钟网络上同步元件同时动作数量的变化…

当设计的目标运行时钟频率较高时,应考虑到时钟抖动对设计时序性能的制约。

Xilinx在UG612(v14.3) -- Timing Closure User Guide的194页“Clock Uncertainty”部分指明,设计者应通过System Jitter这一时序约束参数告诉工具软件,本设计预计将面临的时钟系统抖动情况,从而布局/布线、时序分析工具可根据设计者的要求对布局/布线进行优化,并给出考虑了时钟系统抖动的静态时序报告。UG612(v14.3)指明:XST软件为部分器件预置了缺省System Jitter参数(如,Spartan-6缺省为70ps),若设计者在UCF文件中指定了这一参数,则覆盖软件的缺省值,并推荐设计者按照300ps约束此参数。UG612中未对此参数传递关系做更多的说明,一个直观的理解是:设计者在UCF中指定多少,XST软件即按照多少进行时序优化及分析?

笔者近日一个基于Spartan-6 XC6SLX150-2的设计,其中部分电路设计为240MHz的运行时钟,决定在设计中添加System Jitter约束,而这个约束参数的使用,一度给我造成了相当大的困扰,经过仔细研读XST静态时序分析报告,确认了以下现象:

- 设计者在UCF文件中通过SYSTEM_JITTER关键字指定的系统抖动参数是直接传递至XST静态时序分析工具的。

- XST静态时序分析工具使用SYSTEM_JITTER约束时会根据被分析路径中同步元件的数量,按照“和方根”的方式对本路径的系统抖动进行合成,这一点在UG612中并无说明。

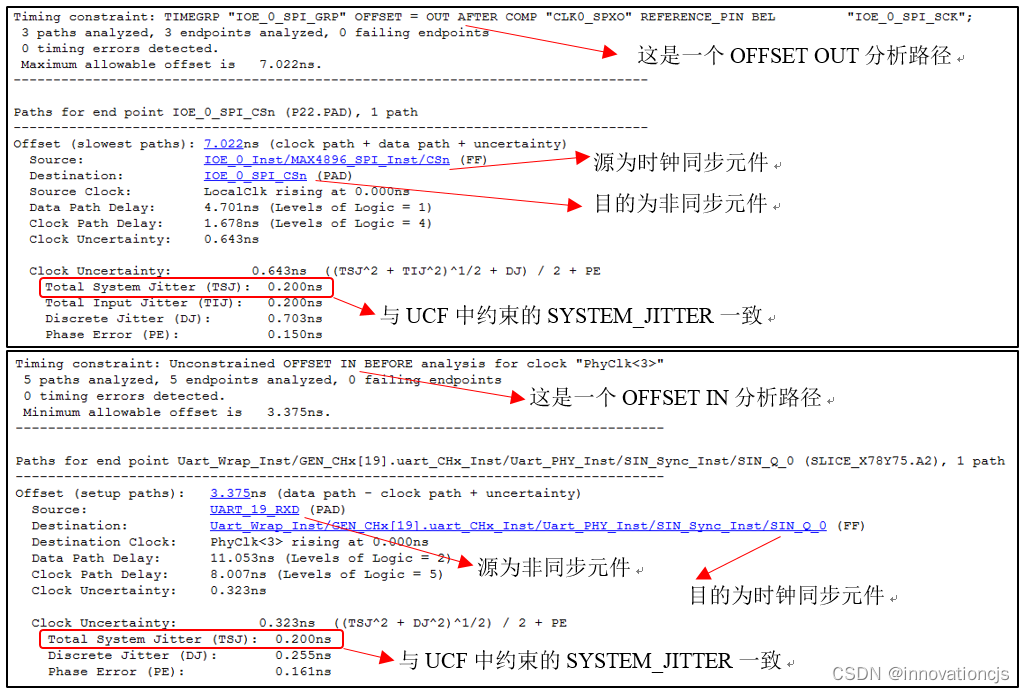

一个添加了200ps SYSTEM_JITTER约束的设计,查看布局/布线完成后的静态时序报告,其中OFFSET IN或OFFSET OUT路径,由于这类分析路径中只有一个同步元件,静态时序报告中给出的Total System Jitter (TSJ)数据与UCF文件中的设定值一致,如下图:

对于在FPGA逻辑设计中,关注度最高的Register-to-Register建立时间的分析路径,源/目的均为时钟同步元件,XST静态时序分析工具将UCF文件中SYSTEM_JITTER约束值![]() 后导入时序分析。如下图:

后导入时序分析。如下图:

那么,应该如何理解XST静态时序分析工具的这一(![]() )处理方式呢?我的理解有两点:

)处理方式呢?我的理解有两点:

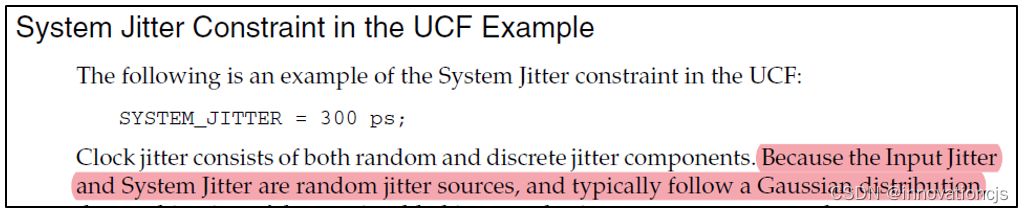

UG612第195页指明:XST静态时序分析工具将SYSTEM_JITTER处理为附加于时钟之上的满足高斯分布的随机变量,见下图:

Register-to-Register建立时间的分析对象为两个相邻时钟边沿,这两个边沿各自受SYSTEM_JITTER的影响是独立随机的,则SYSTEM_JITTER对两个边沿的综合影响自然按照独立同分布随机信号的合成方法处理:和方根。本项分析中随机信号的数量为2,合成时即为![]() 。

。

2640

2640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?