0. 前言

UART(Universal Asynchronous Receiver/Transmitter),即通用异步收发器。IEEE Spectrum发布的芯片名人堂系列文章《Chip Hall of Fame: Western Digital WD1402A UART》这样写道:1960年代,为了实现电传打字机(Teletype)与PDP-1小型计算机之间的连接,DEC(Digital Equipment Corp)公司的Gordon Bell采用大约50个分离元件设计了一个电路板,发明了UART。大约在1971年,西部数据(Western Digital)公司推出了世界上第一块UART集成电路芯片——WD1402A。

时至今日,虽然在个人消费类电子产品中,UART已近乎绝迹;但在工业、科研、国防、航空/航天等领域,UART却无处不在。

1. UART的基本原理

大多数嵌入式软件/硬件工程师、数字IC前端工程师、FPGA逻辑设计工程师,在他们学习或工作中,都会接触乃至深研UART的相关知识。

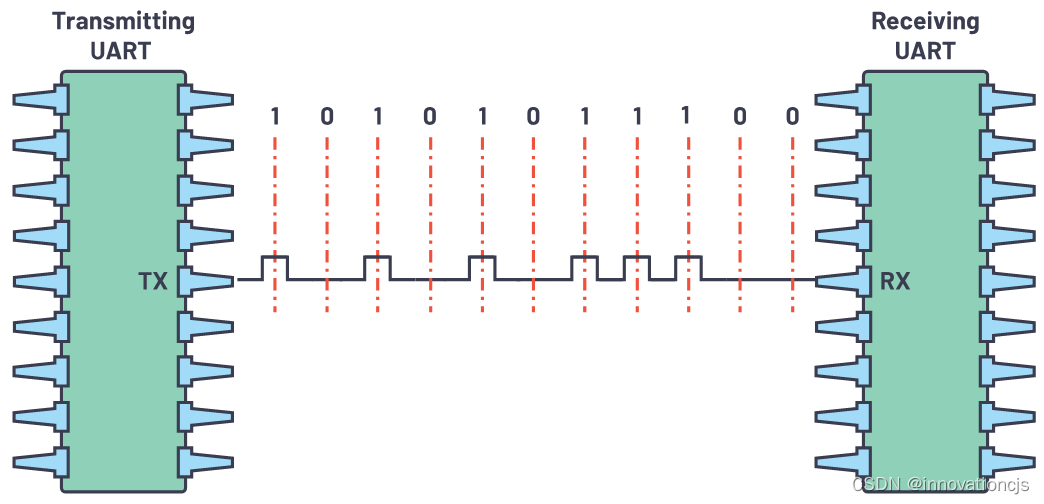

UART是一个异步的串行数字通信协议,实际应用时可工作于全双工或半双工的模式。收/发终端之间的信号传输属于数字基带传输,信道编码方式为非归零(NRZ)编码。NRZ编码采用传输媒介(光、电)的两种物理状态分别表示二进制的逻辑0和1,并且在整个比特位时期间没有状态的变化。如下图所示(图源:ADI. UART:了解通用异步接收器/发送器的硬件通信协议):

由于UART收发终端之间是异步的,而且NRZ编码方式决定了传输的数据码流中不包含时钟信息,接收机只能看到自己的输入端一会儿高电平,一会儿低电平,怎么确定高/低电平这段时间内,发送端到底发送了几个1/0?靠约定,比如8.68μs的低电平表示一个0,没错,就是这么简单粗暴!这个多长时间表示一个比特1或0的约定,就是我们通常所说的UART波特率设定(由于UART采用NRZ编码,其波特率和比特率在数值上是相等的,通常在描述UART时大家并不作严格的区分,而且波特率的使用更为常见,本文也不作严格的区分。)

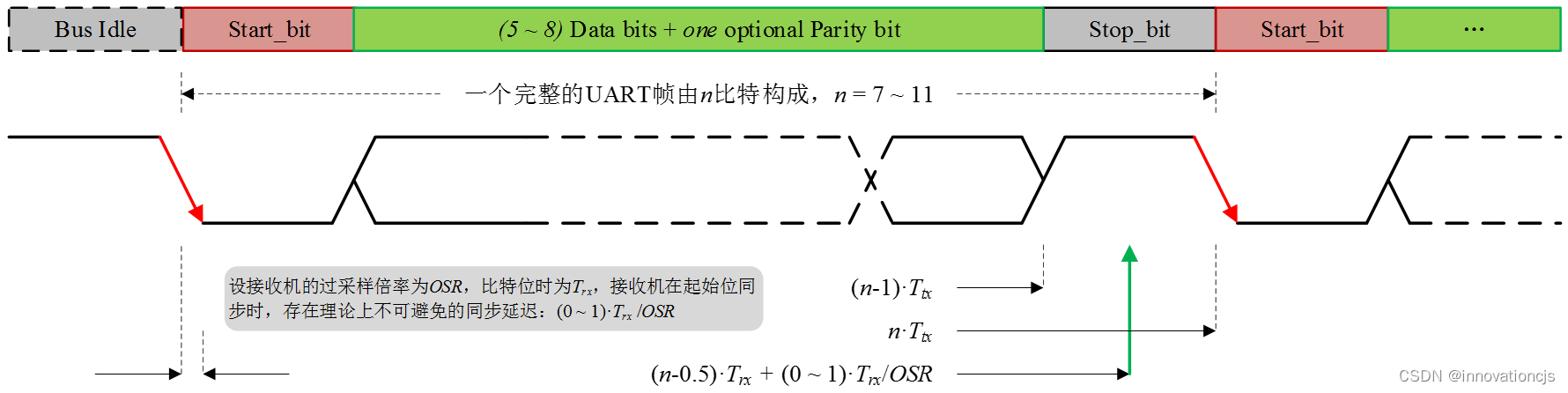

约定好波特率后,我们还需要约定传输什么时候开始(起始位),什么时候结束(停止位),中间传输多少比特的数据位,这通常称为一个UART信息帧(Frame)。几十年的发展过程中,芯片厂商和国际标准化组织为不同的应用场景制定了一些可变的UART帧格式:

- 一个比特的起始位;

- 5 ~ 8比特的数据位;

- 可选的1比特校验位;

- 0.5/1.0/1.5/2.0比特的停止位,其中1或2比特停止位的应用最为常见。

2. UART接收机波特率容差的分析

由于UART发射机和接收机之间是异步的,接收机必须基于本地时钟采样接收数据线以完成解码,并在每个数据帧起始位的前沿(下降沿)复位比特定时器。这个过程中至少有两个因素可能导致接收机解码错误:

- 发射机和接收机的本地时钟频率存在偏差,即发送位周期\( T_{tx} \)与接收位周期\( T_{rx} \)之间存在偏差;

- 起始位的同步时机是一个下降沿,理论上是一个无限短的时刻,而接收机的本地采样时钟频率是有限的,故接收机同步后的下降沿时刻一定是滞后真实的接收数据线下降沿的。设接收机的过采样倍率为OSR,则起始位下降沿同步存在一个理论上不可避免的延迟:\( (0~1)\cdot T_{rx}/OSR \)。

一个背靠背(相邻两个信息帧间无总线空闲间隔)的UART传输如下图所示,本文将以FPGA逻辑设计工程师的角度来分析UART接收机的波特率容差理论极限。

UART接收机工作时,起始位下降沿同步后,将按照\( T_{rx} \)的固定时间间隔对接收数据线采样,并在设计上对齐于每位的中点,对于一个\( n \)位(起始位+数据位+校验位+停止位)的数据帧,无差错解码需要最后一个比特(即停止位)的接收采样时刻落在如上图所示的\( (n-1)\cdot T_{tx} \)到\( n \cdot T_{tx} \)区间范围内,考虑发送波特率(\( B_{tx}=1/T_{tx} \))和接收波特率(\( B_{rx}=1/T_{rx} \))的大小关系分析发送波特率相对接收波特率的允许偏差范围:\( \frac{B_{tx}-B_{rx}}{B_{rx}} \times 100\% \) 。

2.1 接收波特率大于发送波特率(收快发慢)时

最后一个采样点应位于最后一个比特的前沿之后,此时应考虑的最坏情况是起始位下降沿同步时几乎无延迟,有:

\[ \begin{aligned}

(n-1)\cdot T_{tx} &\leq (n-0.5)\cdot T_{rx} \\

T_{tx} &\leq \frac{n-0.5}{n-1} \cdot T_{rx}

\end{aligned} \]

即:

\[ B_{tx} \geq \frac{n-1}{n-0.5} \cdot B_{rx} \]

可计算出发送波特率相对接收波特率允许的负偏差极限值为:

\[ (\frac{n-1}{n-0.5}-1) \times 100\% = \frac{-0.5}{n-0.5} \times 100\% = -\frac{1}{2n-1} \times 100\% \]

UART帧长度范围为7 ~ 11比特,各帧长度下允许的波特率负偏差限值(百分比)如下表:

| 帧长(n) | 7 | 8 | 9 | 10 | 11 |

| 允许偏差 | -7.69% | -6.67% | -5.88% | -5.26% | -4.76% |

2.2 接收波特率小于发送波特率(收慢发快)时

最后一个采样点应位于最后一个比特的后沿之前,此时应考虑的最坏情况是起始位下降沿同步时延迟\( T_{rx}/OSR \),有:

\[ \begin{aligned}

n\cdot T_{tx} &\geq (n-0.5+1/OSR)\cdot T_{rx} \\

T_{tx} &\geq \frac{n\cdot OSR-0.5OSR+1}{n\cdot OSR}\cdot T_{rx}

\end{aligned} \]

即:

\[ B_{tx} \leq \frac{n\cdot OSR}{n\cdot OSR-0.5OSR+1}\cdot B_{rx} \]

可计算出发送波特率相对接收波特率允许的正偏差限值(百分比)为:

\[ \begin{aligned}

(\frac{n\cdot OSR}{n\cdot OSR-0.5OSR+1} -1)\times 100\%

&= \frac{0.5OSR-1}{n\cdot OSR-0.5OSR+1}\times 100\% \\

&= \frac{0.5 - 1/OSR}{n-0.5+1/OSR}\times 100\%

\end{aligned} \]

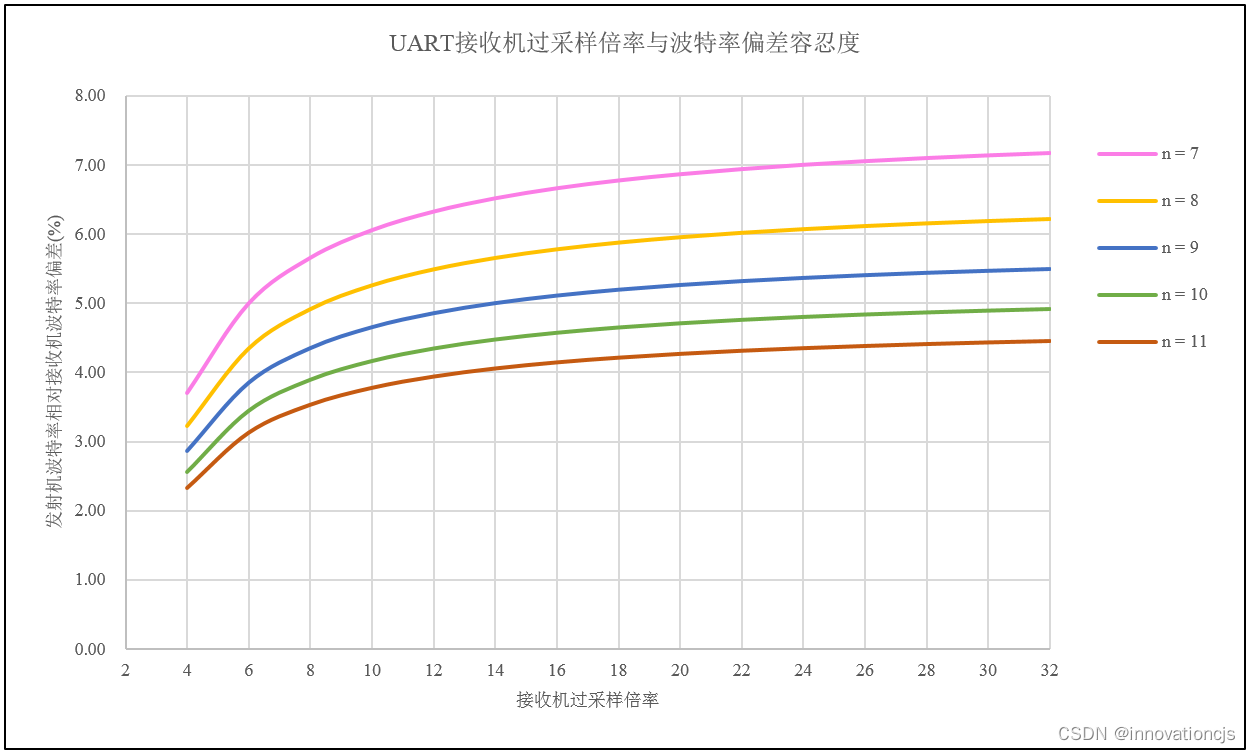

可以看到,当接收波特率小于发送波特率时:

- 随着字长\( n \)增大,允许的波特率偏差变小,符合一次同步后,以固定时长采样的误差累积规律;

- 当过采样倍率OSR趋于\( \infty \)时(即接收机实现起始位下降沿的理想同步),则允许的波特率偏差将趋于极限\( \frac{0.5}{n-0.5}\times 100\% \) 。

绘制4 ~ 32倍接收过采样倍率,7 ~ 11比特字长时,发送波特率相对接收波特率允许的正偏差限值如下图:

可以看到:

- 当接收机过采样倍率OSR低于8时,OSR对波特率容差的影响很明显;

- OSR在8 ~ 16范围是可接受的;

- OSR超过16后,进一步提高OSR对波特率容差的改善并不明显。

综合来看,16倍的过采样倍率在UART接收机设计的工程实践中是一个很优化的选择。

备注:本文将接收机的无差错采样点定义在了停止位的中点,这在背靠背传输时是必要的,是一种对接收机设计更严苛的考虑,若需放宽约束至最后一个数据位(或校验位),为上述公式代入不同的帧长度 n 即可,不赘述。

3. 高波特率容差的设计建议

到目前为止,本文对UART接收机波特率容差限值的分析还停留在FPGA逻辑设计的理论层面,是我们能够达到也应该达到的理论极限,这一极限是可以在RTL仿真阶段验证的。

如何设计一个波特率容差足够大的UART接收机,笔者认为最重要的是理解UART起始位和停止位的真实含义和用法,供广大FPGA逻辑工程师参考。

UART的起始位和停止位并不用于发射机和接收机之间的信息传递,是为了实现信息传递而添加的必要冗余,甚至可以把UART的起始位和停止位理解为专为咱们逻辑工程师制定的。

UART的起始位和停止位是配套的,不是孤立的,是为了解决收/发机间异步工作引起的两个问题而制定的机制。

收/发机间传输的是NRZ编码的二进制串行码流,无时钟信息,那么接收机如何划分码元(比特)边界?依据预先约定的波特率,接收机对收到的二进制码流按时间等间隔划分。那么,第二个问题来了,时间的起点在哪里?没错,起始位。需要注意的地方来了,起始位是用来标记时间的起点,这是一个点,理论上是一个无限短的时刻,什么能代表这个时刻?起始位的前沿(即下降沿),所以我们需要的是起始位的下降沿。故UART接收机的起始位检测包含两个必不可少的动作:

- 时间起点的捕捉,即起始位下降沿检测;

- 时间起点的标记,即复位接收机本地的位定时器。

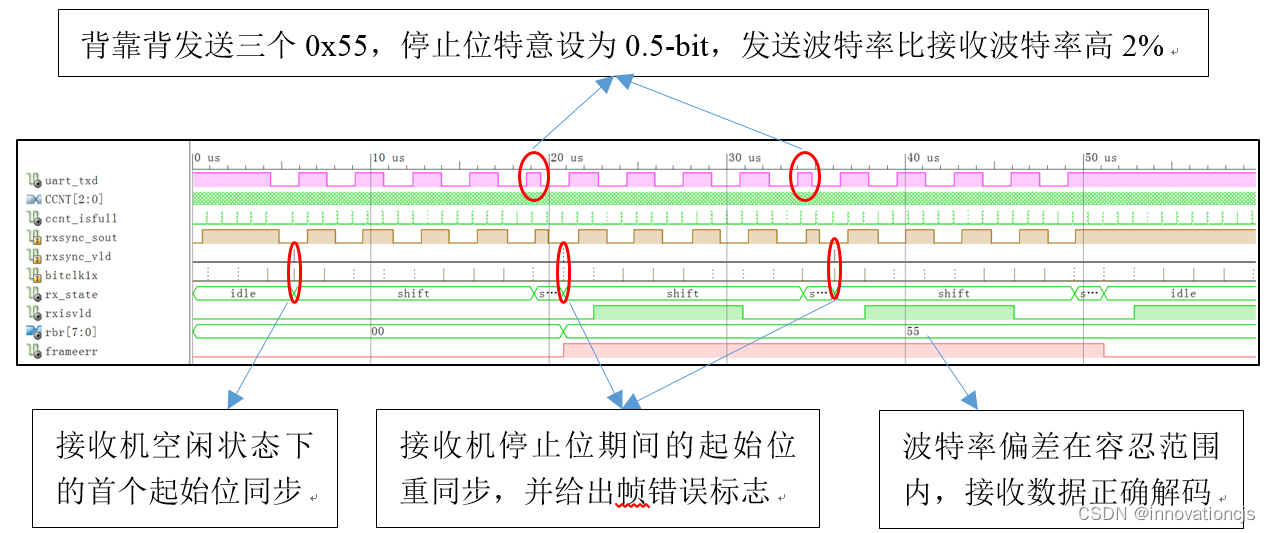

前文提到,起始位和停止位是配套的,如何理解?这是因为UART发射机和接收机各自的本地时钟间不可避免的存在频率偏差,即便我们能实现起始位时间起点的绝对同步,也会在后续比特解码中累积时间误差,所以我们还需要在传输一定数量(5 ~ 9)的比特之后再次同步以消除时间的累积误差。怎么再次同步?再发一个起始位。不要忘记,起始位不是一个位时的逻辑0,而一定要有一个下降沿的脉冲前沿,但当我们需要再次发送起始位时,前一比特的数据位是逻辑1还是逻辑0?这不由我们控制,是由用户的应用来决定的,故而为了能确保起始位的前沿是下降沿,UART协议规定了一个固定为逻辑1的停止位(这在逻辑上与总线空闲时的状态是一致的),看到了吗,停止位是为起始位服务的,是为了确保能再次检测到一个起始位下降沿而制定的,所以,UART接收机在停止位这个时间段应该完成的动作有:

- 捕捉一个预期的起始位下降沿;

- 若成功捕捉到起始位下降沿,则复位本地位定时器以再次同步;

- 在停止位中点处采样一个预期的逻辑1,若失败则标记一个“帧错误”,提醒用户存在可能的波特率超差或线路噪音过大。

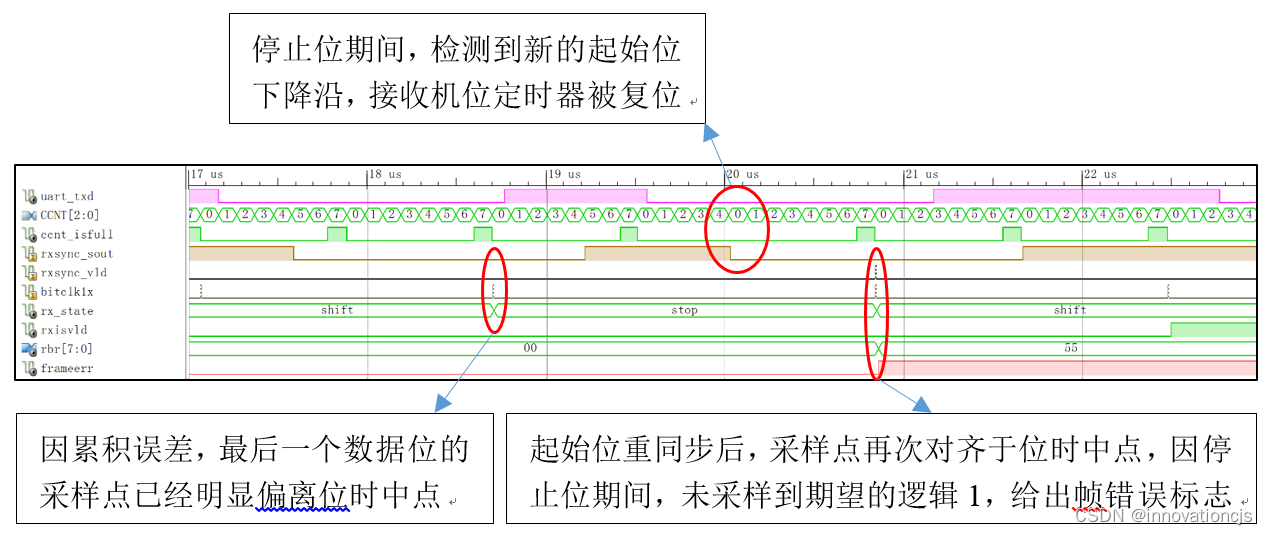

为反映本文建议的UART接收机起始位/停止位检测原理,笔者对设计的UART接收机仿真,如下图所示:

放大第一个字节停止位的局部仿真波形,可更为清晰地反映起始位的重同步过程,如下图所示:

附上几个网友分享的与本文内容相关的案例(愿国产芯片“少一些弯道超车,多造一点自己的轮子”,愿国产芯片的路越走越宽!):

1121

1121

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?