cache(包括电路)能稳定运行的最低电压称为Vccmin,当实际电压Vcc低于Vccmin时,就会影响微处理器的稳定性。论文首次运用架构级的技术来使cache在低于500mV电压下稳定运行。

cache在低电压下出错:

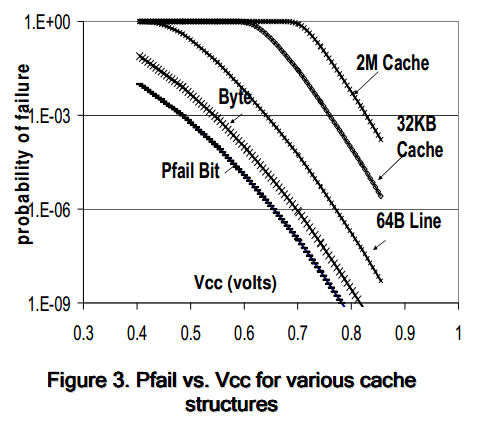

当电压下降,伴随参数变化(parametric variation),例如intra-die Random Dopant Fluctuations(RDF)会通过影响阈值电压Vth来影响SRAM cell读和写得稳定性,造成cache failure。随着电压下降,失效概率呈指数增加,如下所示:

我们可以看到,本来正常电压下cache极不可能failure,但在低电压(如近阈值或亚阈值电压)下cache可能failure,或许运行一阵子便会出现错误。在500mV电压下,几乎每一条64字节的cache line都有一个缺陷位(defective bit),因为一条cache line包含很多cell,任何一个cell失效,都会让这条cache line有缺陷(defective)。

这里我们认为当失效率(probability of failure)不高于1.E-03是可以接受的,以此为标准,当我们将研究对象由整个cache缩小到单个bit时,实现低电压同时保证失效率在容忍范围是可以做到的,论文给出下图:

ECC是常用的位错误检测及纠正方法,但也存在高的存储开销和对多位错误需要复杂的操作等缺陷,接下来我们在第二部分讲解论文中提出的两个新颖的fault-tolerant方法:Cache word-disable和Cache bit-fix。

1038

1038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?