HDLBits【学习记录(难点)】

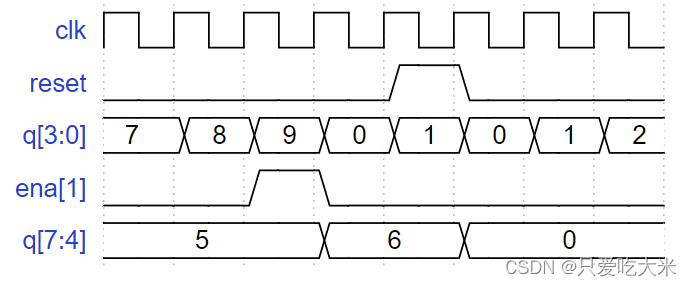

1.4-bit decimal counter

Build a 4-digit BCD (binary-coded decimal) counter. Each decimal digit is encoded using 4 bits: q[3:0] is the ones digit, q[7:4] is the tens digit, etc. For digits [3:1], also output an enable signal indicating when each of the upper three digits should be incremented.

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

assign ena[3:1]={(q[3:0]==4'd9)&&(q[11:8]==4'd9)&&(q[7:4]==4'd9),(q[7:4]==4'd9)&&(q[3:0]==4'd9),(q[3:0]==4'd9)};

// assign q={q[15:12],q[11:8],q[7:4],q[3:0]};

BCD_Decade_Counter Ge_BCD(

.clk(clk),

.reset(reset),

.enable(1'b1),

.q(q[3:0])

);

BCD_Decade_Counter Shi_BCD(

.clk(clk),

.reset(reset),

.enable(ena[1]),

.q(q[7:4])

);

BCD_Decade_Counter Bai_BCD(

.clk(clk),

.reset(reset),

.enable(ena[2]),

.q(q[11:8])

);

BCD_Decade_Counter Qian_BCD(

.clk(clk),

.reset(reset),

.enable(ena[3]),

.q(q[15:12])

);

endmodule

module BCD_Decade_Counter(

input clk,reset,enable,

output [3:0]q

);

always@(posedge clk)begin

if(reset)

q<=4'b0;

else

if(enable)

if(q==4'd9)

q<=4'd0;

else

q<=q+4'd1;

else

q<=q;

end

endmodule

2.12-hoursclock

用计数器设计一个12小时时钟(AM与PM)。通过一个CLK进行计时,用ena使能信号来驱动时钟的递增。

reset端口用于复位时间至12:00 AM。其中当pm=0为AM(上午),pm=1为AM(下午)。hh、mm和ss由两个BCD计数器构成,例如其中ss[3:0]代表秒钟的个位,ss[7:4]代表秒钟的十位。mm为分钟,hh为小时。

关键点(思路):

1.秒钟个位ss[3:0]的使能信号ena是一直有效的

2.秒钟十位ss[7:4]的使能信号只有在秒钟个位为9才能够进位有效,对于分钟个位mm[3:0]的进位条件为秒钟达到59,分钟十位进位条件为 分钟个位到9,秒钟十位和个位为59,后面如此进行推理…

3.当时间达到12:59:59pm会转变成01:59:59,此刻需要注意时hh的高四位和第四位变化

4.对于pm的切换,当0为AM,1为PM.变化条件为例如11:59:59am,下一个时钟clk到来则变成12:00:00pm.

下图所示的时序图为11:59:59 AM 到12 :00 : 00 PM。

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire ss_ge_start;

wire ss_ge_end;

wire ss_shi_start;

wire ss_shi_end;

wire mm_ge_start;

wire mm_ge_end;

wire mm_shi_start;

wire mm_shi_end;

wire hh_ge_start;

wire hh_ge_end;

wire hh_ge_reset1;

wire hh_shi_start;

wire hh_shi_end;

wire hh_shi_reset2;

wire pm_alert;

//秒ss个位

assign ss_ge_start=ena;//ss个位使能端

assign ss_ge_end=ss_ge_start&&ss[3:0]==4'd9;//ss个位计数9复位||为十位开始计数的使能条件

always@(posedge clk)begin

if(reset)begin

ss[3:0]<=4'd0;

end

else begin

if(ss_ge_start)begin

if(ss_ge_end)begin

ss[3:0]<=4'd0;

end

else begin

ss[3:0]<=ss[3:0]+1'b1;

end

end

end

end

//秒ss十位

assign ss_shi_start=ss_ge_end;//ss十位使能端

assign ss_shi_end=ss_shi_start&&ss[7:4]==4'd5;//ss十位5个位计数9-复位||为分钟个位开始计数的使能条件

always@(posedge clk)begin

if(reset)begin

ss[7:4]<=4'd0;

end

else begin

if(ss_shi_start)begin

if(ss_shi_end)begin //当个位计数到9&&十位计数到5,

ss[7:4]<=4'd0;

end

else begin

ss[7:4]<=ss[7:4]+1'b1;

end

end

end

end

//分mm个位

assign mm_ge_start=ss_shi_end;//ss十位使能端

assign mm_ge_end=mm_ge_start&&mm[3:0]==4'd9;

always@(posedge clk)begin

if(reset)begin

mm[3:0]<=4'd0;

end

else begin

if(mm_ge_start)begin

if(mm_ge_end)begin //当个位计数到9&&十位计数到5,

mm[3:0]<=4'd0;

end

else begin

mm[3:0]<=mm[3:0]+1'b1;

end

end

end

end

//分mm十位--计数到5

assign mm_shi_start=mm_ge_end;//ss十位使能端

assign mm_shi_end=mm_shi_start&&mm[7:4]==4'd5;

always@(posedge clk)begin

if(reset)begin

mm[7:4]<=4'd0;

end

else begin

if(mm_shi_start)begin

if(mm_shi_end)begin //当个位计数到9&&十位计数到5,

mm[7:4]<=4'd0;

end

else begin

mm[7:4]<=mm[7:4]+1'b1;

end

end

end

end

//时hh个位

assign hh_ge_start=mm_shi_end;

assign hh_ge_reset1=hh_ge_start&&hh[7:4]==4'd1&&hh[3:0]==4'd2;//计数到12:59:59,下一个clk到达则个位为1

assign hh_ge_end=hh_ge_start&&hh[3:0]==4'd9;

always@(posedge clk)begin

if(reset)begin

hh[3:0]<=4'd2;

end

else begin

if(hh_ge_start)begin

if(hh_ge_reset1)begin

hh[3:0]<=4'd1;

end

else if(hh_ge_end)begin

hh[3:0]<=4'd0;

end

else begin

hh[3:0]<=hh[3:0]+4'd1;

end

end

end

end

//时hh十位

assign hh_shi_start=hh_ge_end;//当计数到_9:59:59时,_十位加1

assign hh_shi_reset2=hh_ge_start&&hh[7:4]==4'd1&&hh[3:0]==4'd2;//当时间到12:59:59,hh的十位置0

always@(posedge clk)begin

if(reset)begin

hh[7:4]<=4'd1;

end

else begin

if(hh_shi_reset2)begin

hh[7:4]<=4'd0;

end

else if(hh_shi_start)begin

hh[7:4]<=hh[7:4]+4'd1;

end

end

end

//pm:0为上午,1为下午

assign pm_alert=hh_ge_start&&hh[7:4]==4'd1&&hh[3:0]==4'd1;//达到条件11:59:59时下个时钟切换上下午

always@(posedge clk)begin

if(reset)begin

pm<=1'b0;//复位为0 早上

end

else begin

if(pm_alert)begin

pm<=~pm;

end

end

end

endmodule

4160

4160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?