最近使用Vivado编写CPU遇到了synthesis failed(synth_design ERROR)问题,但是Message里面居然没有ERROR信息,只有一些warnings。而且综合的时间特别长,相较于平时的综合时间大概多了2、3倍。

我用了两天时间钻研这个问题都没有解决。期间,我检查了多次都没有发现模块或者顶层文件出现问题,感到非常郁闷。

本来我以为是自己的电脑问题,后来在别人的电脑上面依然出现问题。而且别人的电脑根本没有出现synthesis failed(synth_design ERROR)问题,就是一直综合,十分钟之后都没有结束!

在网上查找很久,只查找到极少的信息,而且大部分都没有什么用处。其中有一个人说自己更换了2017.2的版本解决了此问题,我感到似乎有了一些头绪。因为我的版本是2015.2.。后来准备下载2017.2的时候,发现2017.2居然有20多个G!此处吐槽一下百度云,实在是太慢了。

在下载的时间我仍然在思考,后来让同学在他的机子上面用ISE综合了一下我的文件,综合前面都没有问题,但是最后告诉我文件太大,所需资源不足。因为ISE绑定的是Basys 2的板子,而我的vivado绑定的是Nexys 4DDR的板子,所以我想Nexys 4DDR的板子应该不会资源不够用。但是,我还是试着把我在指令寄存器、数据寄存器、寄存器堆里面申请的数组数量减少。不过,其实本来也用不到那么多。

在我大幅减少数组数量之后,我重新综合了一下,在综合期间和同学聊了一会,结果回来一看,居然综合成功了!

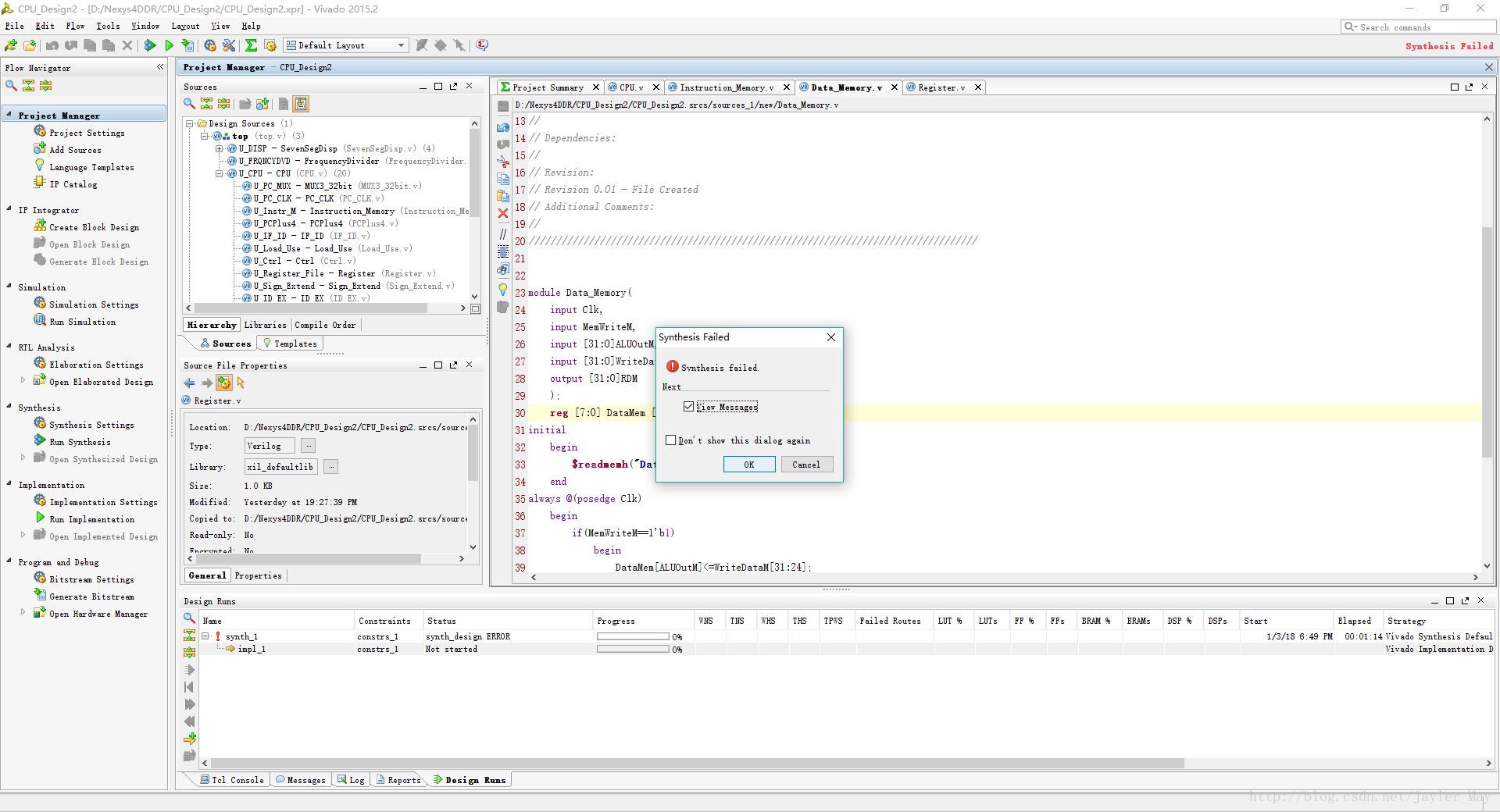

下面是失败情况的截图:

此处synth_1的进度一直为0:

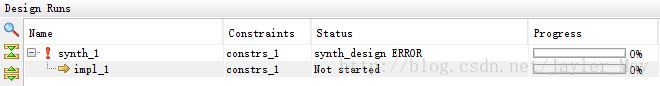

然后Message里面也没有ERROR信息:

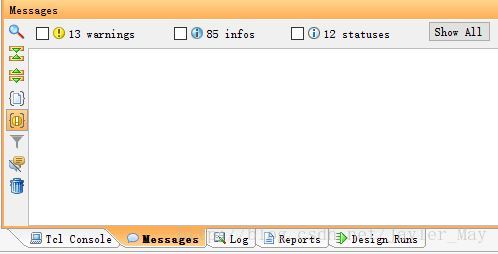

问题出在这里面:

reg [7:0] InstMem [0:1023];

还有这里:

reg [7:0] DataMem [0:1023];

Register.v里面倒是没有申请那么多的数组,但是之前的两个申请的太多了!

reg [31:0] Regfile[0:31];

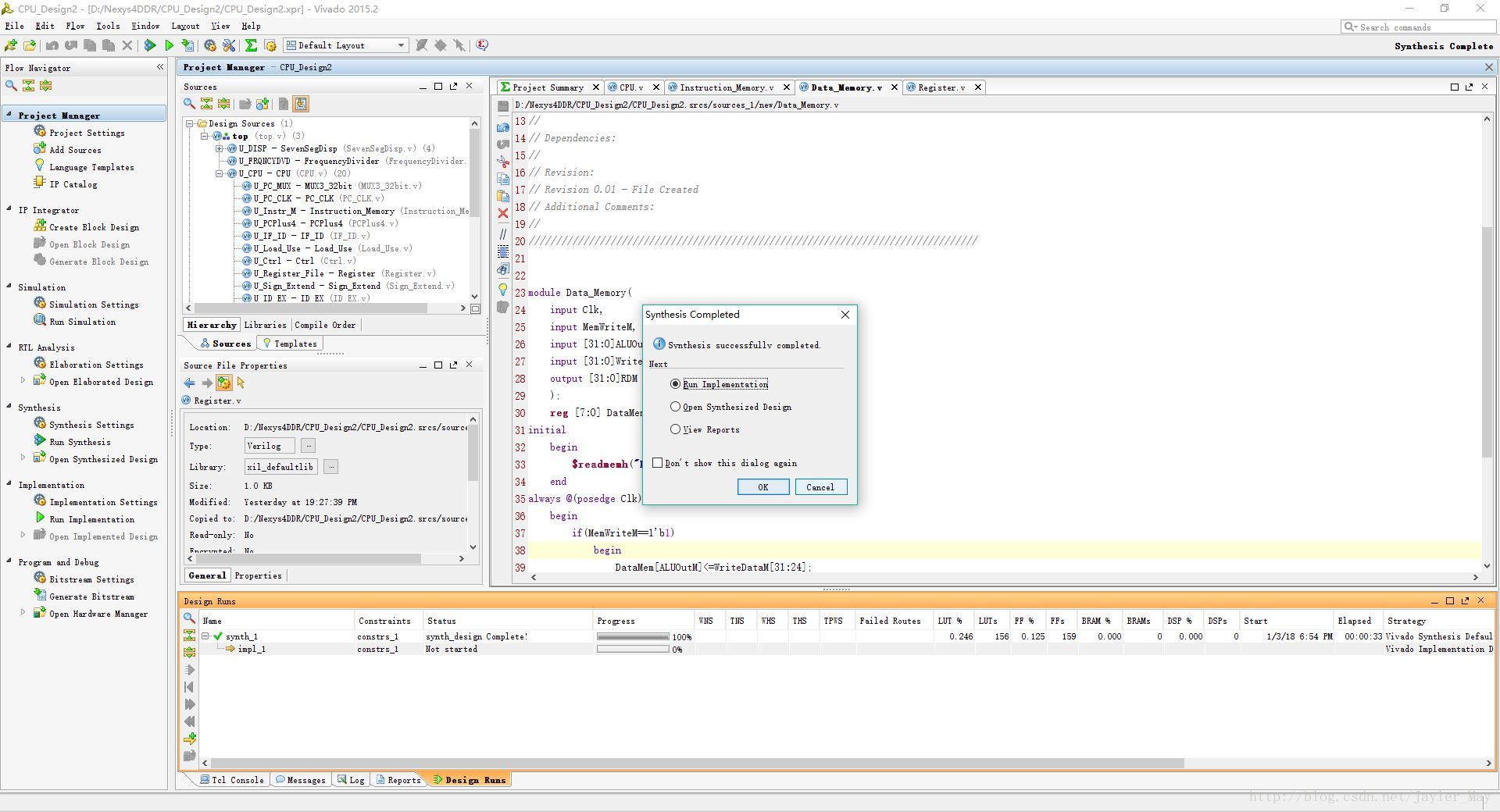

改成了这样:

reg [31:0] InstMem[0:15];reg [31:0] DataMem[0:15];然后顺利通过:

而且,我发现综合的速度大大提高!

不能随便申请数组数量,一定要考虑自己的需求。综合实际上是按照开发板对程序实现的电路进行布线(此处可能不准确,欢迎指正),所以数组大了之后电路也就大了,综合起来当然更加耗费时间。

4170

4170

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?