Cadence软件的原理图和PCB是两个软件,原理图到PCB需要创建网表,然后在PCB中放置已经建好分封装的元器件;

如果对于已经画好的PCB,后期发现需要更改原理图的某个部分,原理图更改后,怎么同步更新到PCB中,而不变动原来已经布好局、布好线的的PCB呢?

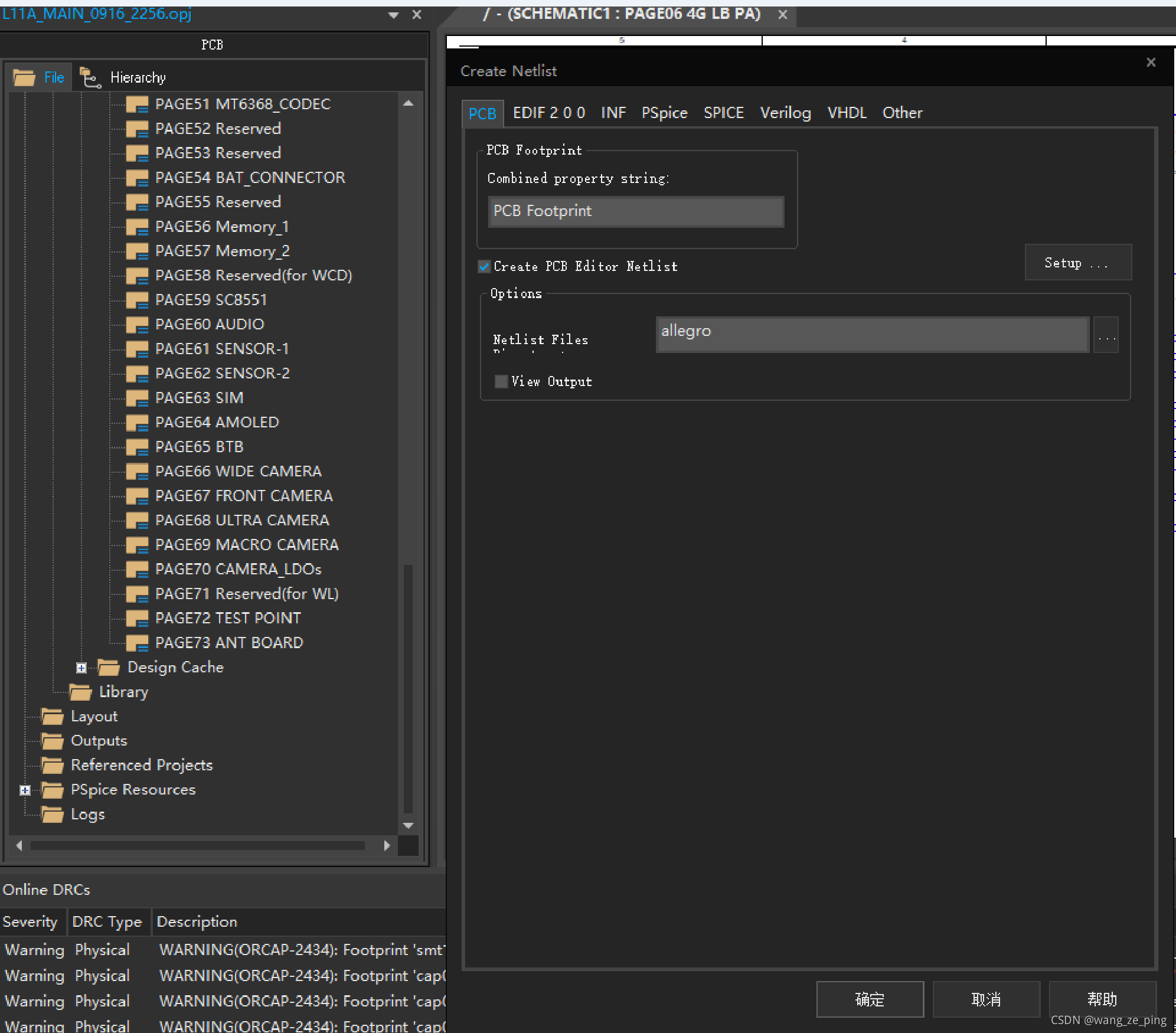

1、打开原理图,点击选中下打开的DSN文件,点击Tools中的Create Netlist,点击确定,创建成功后,output下输出的就是三个网表文件

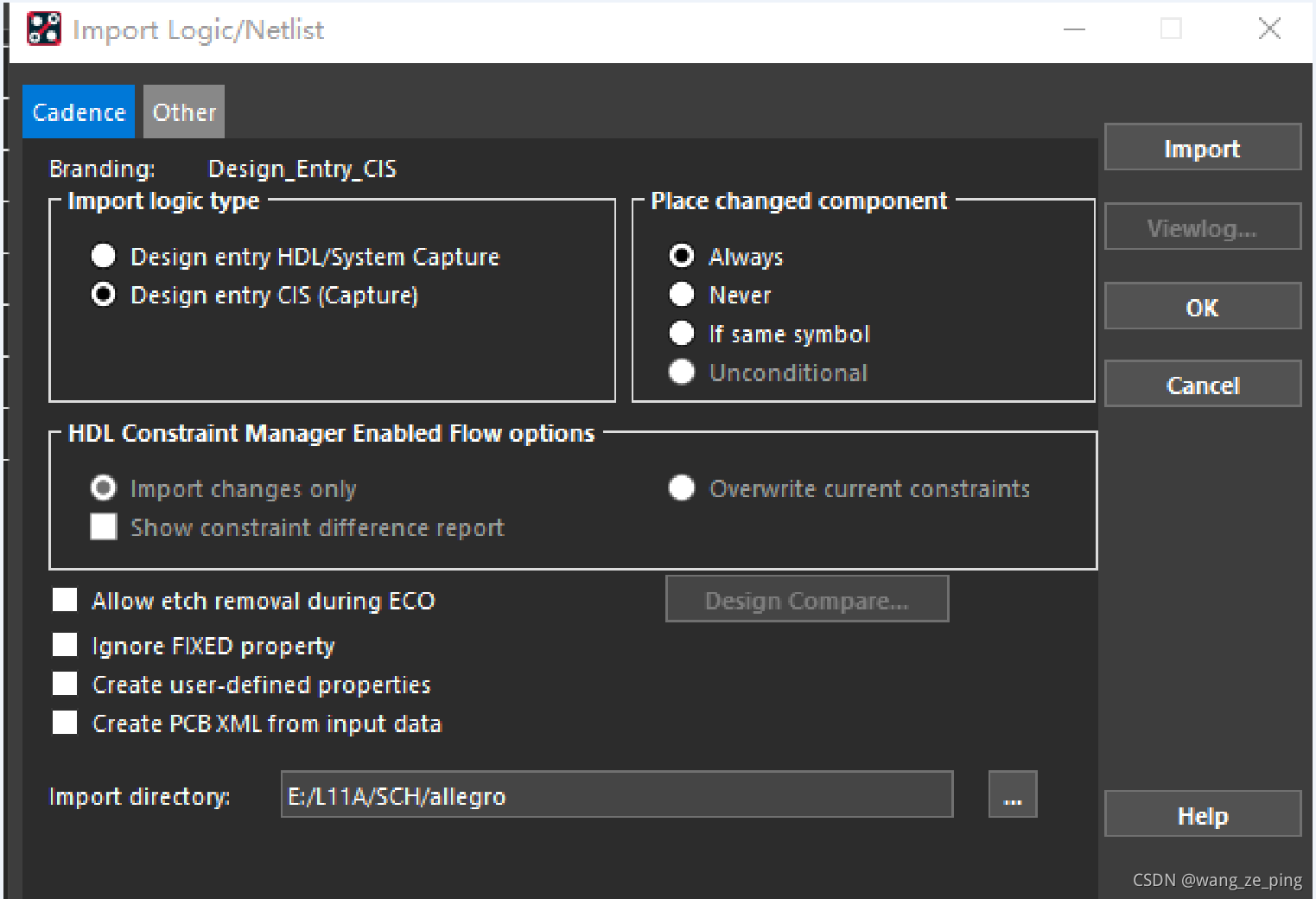

2、网表创建成功后,回到Allegro PCB的页面,点击File中Import Logic;如下图所示,一定要取消Ignore FIXED property前面的勾,否则每次更改原理图更新PCB时,原来的布局布线都被打乱(当然,如果出现cannot modify element the object or a parent has the fixed property导入网表错误,可以勾选Ignore FIXED property卡面的勾);另外导入网表的路径(Import directory一定要是网表的根目录,否则导出不成功)

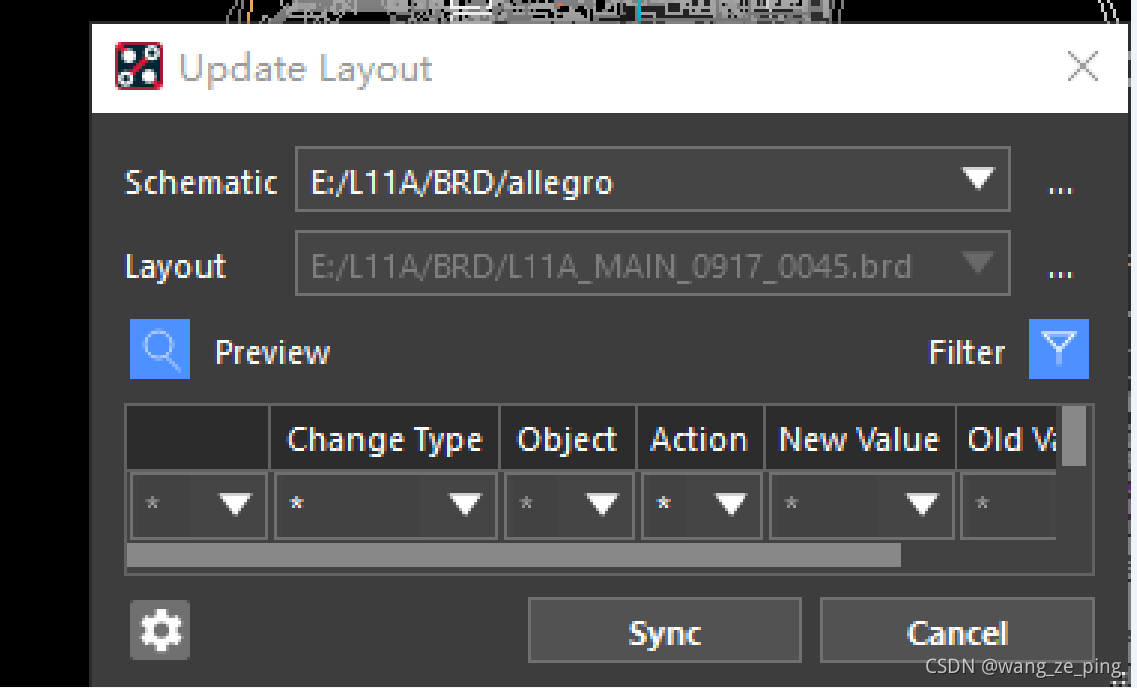

3、allegro PCB中导入网表成功后,原理图和PCB就建立了一一对应关系;此时如果想修改原理图,修改保存后,重新生成创建网表Create Netlist后,回到Allegro PCB页面,点击File中的Update Layout,

4、点击上述的同步Sync后,在Display的Status查看相关状态,如果有未放的元器件可以点击Place中Manually放置相关器件

---------------------

作者:wang_ze_ping

来源:CSDN

原文:https://blog.csdn.net/wang_ze_ping/article/details/120571849

版权声明:本文为作者原创文章,转载请附上博文链接!

内容解析By:CSDN,CNBLOG博客文章一键转载插件

5262

5262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?