目录

从Verilog到SV的进场

1. 修改tb1.v 为 tb1.sv ,编译仿真,查看仿真行为是否同tb1.v的仿真行为一致?这说明了什么呢?

没有变化,仿真行为一致,说明编译器对 SV 的语法和Verilog语法是全部兼容的

2. 将tb1.sv中的信号变量类型由reg或者wire 修改为 logic 类型, 再编译仿真,查看行为是否同修改前的一致呢?这是为什么?

没有变化,仿真行为一致,说明在SV中, reg 和 wire 类型都可以简化为 logic类型

3. 在2)的基础上,将 rstn 的类型由logic 修改为 bit 类型, 再编译仿真,行为是否同步骤2)的一致?这是为什么?

复位信号(rstn)的拉低由第一个时钟下降沿(也就是程序里的10ns)变为了时钟一开始就拉低,因为 bit 是二值类型,默认没有给值的时候是0,然后拉低就一直是0, 而 logic 是 四值类型,一开始没有给值,默认是X, 然后经过10ns 被拉低

任务task 和 函数function

1. 不做修改的情况下,对 tb2.sv进行编译仿真,时钟信号和复位信号还正常吗?为什么?

不正常

2. 在两个initial 块中分别调用产生时钟和复位的task, 再编译仿真查看时钟信号和复位信号,是否恢复正常?

把 task 放到 initial 块中恢复了正常,说明 task 和 function 一样,是需要被调用的,不调用不执行,必须被过程块调用(initial 和 always)

3. 为什么要将两个task 在两个 initial 块中调用?是否可以在一个initial 块中调用呢?如果可以调用它们的顺序是什么?

不可以放在一个initial 块中,放在一起的话,如果时钟信号放在前面,仿真波形里面只会产生clock时钟信号,并没有产生复位信号,这是因为多个initial块是并行的,在initial块内部的执行顺序是串行的,执行clk_gen()时,forever会一直执行,不断产生时钟信号,导致rstn_gen()方法无法调用执行。

4. 目前的时钟周期和频率是多少? 如何测量?改进clk_gen() 方法, 使其变为可以设置时钟周期的任务 clk_gen(int period), 那么该如何修改clk_gen() 呢? 修改成功后, 请在initial 块中调用任务clk_gen(20), 看看波形中的时钟周期是否变为 20ns 呢?

时钟周期是 10ns , 频率是 100MHz , 但是下面的周期是 40ns

task clk_gen(int peroid);

clk <= 0;

forever begin

#peroid clk <= !clk;

end

endtask

initial begin

clk_gen(20);

end

5. 如果将 `timescale 1ns/1ps 修改为 `timescale 1ps/1ps, 那么仿真中的时钟周期是否发生变化?这是为什么?

左边的1ns 是时间单位,右边的1ps 是 时间精度

改为 1ps/1ps,当然会变化 时间单位变为了1ps, 时钟周期也就变为了40ps

数组的使用

1. 如果我们现在要先生成100个数,b并对它们按照目前的数值规则进行赋值,那么创建3个动态数组,分别放置要发送给3个 slave 的数据。

2. 利用之前生成的数组数据,将他们读取并发送给三个 channel。

logic [31:0] chnl0_arr[];

logic [31:0] chnl1_arr[];

logic [31:0] chnl2_arr[];

// generate 100 data for each dynamic array 为动态数组生成100个数据

initial begin

chnl0_arr = new[100];

chnl1_arr = new[100];

chnl2_arr = new[100];

foreach(chnl0_arr[i]) begin

chnl0_arr[i] = 'h00C0_00000 + i;

chnl1_arr[i] = 'h00C1_00000 + i;

chnl2_arr[i] = 'h00C2_00000 + i;

end

end

// 为每个动态数组调用 chnl_write(id,data)

initial begin

@(posedge rstn);

repeat(5) @(posedge clk);

foreach(chnl0_arr[i]) chnl_write(0, chnl0_arr[i]);

foreach(chnl1_arr[i]) chnl_write(1, chnl1_arr[i]);

foreach(chnl2_arr[i]) chnl_write(2, chnl2_arr[i]);

end验证结构

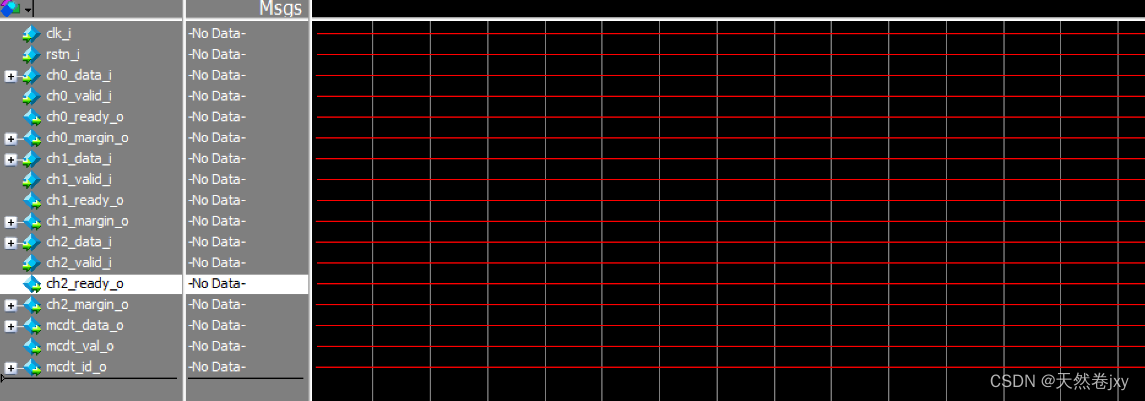

为了实现清晰的验证结构,我们希望将DUT和激励发生器(stimulator)之间划分。因此,我们可以将激励方法chnl_write() 封装在新的模块 chnl_initiator 中,从tb4.sv中可以发现之前的 initial 语句块“channel write task” 已经不见了,在其位置上的变为了三个例化的 chnl_initiator 实例 chnl0_init, chnl1_init 和 chnl2_init 。 它们的作用扮演每个channel slave 通道对应的 stimulator (发送激励),因此我们在其模块 chnl_initiator 中定义了它的三个方法, 即 set_name() , chnl_write() 和 chnl_idle()。

- chnl_idle() 要实现一个时钟周期的空闲 ,在该周期中,ch_valid 应为低, ch_data应为0。

-

task chnl_idle(); @(posedge clk); ch_valid <= 0; ch_data <= 0; endtask - chnl_write() 要实现一次有效的写数据,并随后调用 chnl_idle() , 实现一个空闲周期,结合功能描述的 channel slave 接口时序来看,只有当 valid 为高且 ready 为高时,数据写入才算成功,如果此时 ready 为低,那么则应该保持数据和 valid 信号,直到 ready 拉高时,数据写入才算成功。

-

task chnl_write(input logic[31:0] data); @(posedge clk); ch_valid <= 1; ch_data <= data; @(negedge clk); wait(ch_ready === 'b1); $display("%t channel initial [%s] sent data %x", $time, name, data); chnl_idle(); endtask - set_name() 即设置实例的名称,在 initial 过程块 “data test” 中,在发送各个channel数据显示它们各自的名称,数据发送时间和数据内容,便于阅读和调试。

-

string name; function void set_name(string s); name = s; endfunction - 把他们三个封装在 chnl_initiator模块中作为发送激励,

-

module chnl_initiator( input clk, input rstn, output logic [31:0] ch_data, output logic ch_valid, input ch_ready, input [ 5:0] ch_margin ); string name; function void set_name(string s); endfunction task chnl_write(input logic[31:0] data); endtask task chnl_idle(); endtask endmodule -

把 chnl_iniator模块例化三个实例作为硬件并通过wire传输给channel

-

chnl_initiator chnl0_init( .clk (clk), .rstn (rstn), .ch_data (ch0_data), .ch_valid (ch0_valid), .ch_ready (ch0_ready), .ch_margin(ch0_margin) ); chnl_initiator chnl1_init( .clk (clk), .rstn (rstn), .ch_data (ch1_data), .ch_valid (ch1_valid), .ch_ready (ch1_ready), .ch_margin(ch1_margin) ); chnl_initiator chnl2_init( .clk (clk), .rstn (rstn), .ch_data (ch2_data), .ch_valid (ch2_valid), .ch_ready (ch2_ready), .ch_margin(ch2_margin) ); endmodule -

最后, 之所以提出发送更多的数据,并且发送更紧凑高速的数据,是为了可以观察到,是否你的三个 channel_slave 各自的 chX_ready 信号可以拉低呢? 如果拉低了,这代表着什么? 那么请你试试看,考虑如何发送更多更快的数据,让 MCDT 的三个 chX_ready 信号可以拉低吧!

-

整个实验1的结构图如下:

33

33

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?