目录

前言:

主要从总线协议的特点,信号以及它的功能,读写协议,以及几种传输格式来具体总结它们。

简介:

AMBA(高级处理器总线架构)专门为SOC设计提供的通信标准,不同的速率需求构成了不同的分类。从高到低依次是AXI -> AHB -> APB。

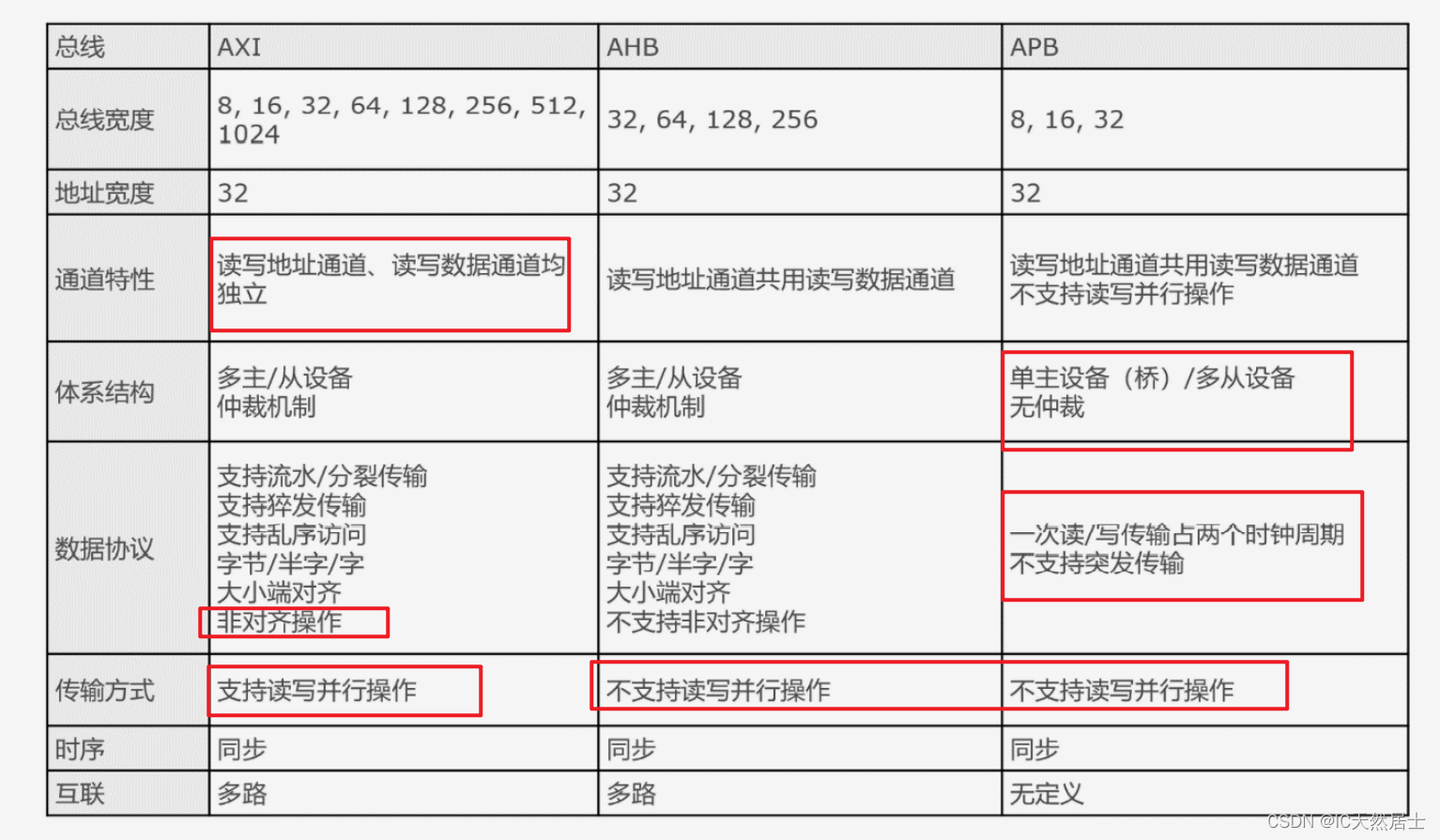

对比:

它们的外接设备的对比:

从上面这个图可以看出AHB和APB的外接

APB: 从端设备分为:

APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4 。

APB2(高速外设)上的设备有:GPIO_A-E、USART1、ADC1、ADC2、ADC3、TIM1、TIM8、SPI1、ALL。

AHB:主设备是CPU,DMA 等控制器 从设备是: RAM等存储器,还有AHBtoAPB Bridge

AXI:和AHB的主从设备差不多。

APB的总结

信号的功能

| 信号 | 描述 |

|---|---|

| PCLK | 时钟,APB协议里所有的数据传输都在 PCLK上升沿进行。 |

| PRESETn | 复位,低电平有效。 |

| PADDR | APB地址总线,最大宽度为 32 bit。 |

| PSELx | 选通从端,APB master 会将此信号生成给每个slave,它表示已选择的slave,并且需要进行数据传输。每个slave 都有一个 PSELx 接收信号。 |

| PENABLE | 使能,当它为高时,表示数据有效。 |

| PWRITE | 读写控制,=1 时表示写操作,=0 时表示读操作。 |

| PWDATA | 写数据,master 通过 PWDATA 将数据写到slave,该总线最大宽度为32bit。 |

| PRDATA | 读数据,master 通过 PRDATA 将数据从slave 读取回来,该总线最大宽度为32bit。 |

读操作

总的来说就是:master读取来自slave的数据,而且APB是固定两周期传输。

在这两个完整周期内,master要发送 PADDR地址以确定要连接哪个slave,要把 PSEL=1 表示对这个slave进行选通,还要把 PWRITE = 0 表示读操作。

在两周期的第二个周期中,master 要把 PENABLE = 1 ,表示使能可以接收数据了。同时 salve 把数据通过 PRDATA 发送给master。

在PENABLE 拉高的下一个上升沿, master 读取数据是准确的,也就是在图中的 T4 上升沿。

最后一次读的传输完成后,PSEL,PENABLE 拉低, PADDR, PWRITE 不变,这样可以紧接着进行下次读传输,实现省电。

写操作

写操作和读操作大致是相同的,唯一不同的是 master 往 slave 里写数据,故 PWRITE = 1 ,数据线 PWDATA 要同地址线一样在两周期内保持。

值得注意的是:依然为了省电,在一次写传输完成后,PADDR 和 PWRITE 要保持不变。

APB2到APB3的变化

在APB2诞生后,随着行业发展,对于APB协议有了新的需求,ARM公司针对这些需求,在APB2的基础上添加了两个端口,一个是PREADY和PSLVERR。PREADY是一个对于slave的准备信号,用于扩展APB的传输协议。PSLVERR是一个错误反馈信号,表示当前传输的数据有误。把这种协议叫做APB3。

除了上面提到的APB2两种基本的读写操作协议,APB3又分别为读写多了一种协议。

针对 PREADY信号

首先是读有等待:

当PSEL和PENABLE都为高的时候,slave 把 PREADY拉低了,说明slave没有准备好,需要等待一段时间。在T5时刻这条虚线,发现PSEL,PENABLE,PREADY都为高,说明这个时候采样的Data是我们想要读取的data。

也就是在有PREADY拉低的情况下,master在 PREADY拉高的下一个时钟上升沿采样数据。

然后是写有等待:

和读操作一样,因为 PREADY的拉低,表示slave没准备好,而使得 控制线,地址线,数据线都再不得不延长几个周期直到 PREADY 拉高为止,数据的传输才算有效,数据的传输才算结束。

针对PSLVERR

我们可以通过使用PSLVERR来指示APB传输上的错误情况。读取和写入事务都可能发生错误。当PSEL,PENABLE和PREADY均为高电平时,仅在APB传输的最后一个周期内才认为PSLVERR有效,其他时间不考虑PSLVERR。

首先是读有等待,并且数据有错误:

在前面的添加了PREADY信号的读操作的基础上,添加PSLVERR,也就是在数据传输的最后一个周期,发现PSEL,PENABLE和PREADY均为高电平的前提下,PSLVERR为高,说明这次数据传输有错误。

然后是写有等待,并且数据有错误:

和读操作是一样的。注意:当任何一个PSEL, PENABLE或者PREADY为低时,你可以将PSLVERR拉低,这是推荐,并不是强制要求。事物处理收到一个错误后,可能或不可能改变外围器件的状态。APB外围设备不要求必须支持PSLVERR引脚,当不使用该引脚时,应被置低。

小总结:

APB2到APB3的变化是多了两个信号,PREADY 和 PSLVERR, 故读写操作也由原来的基础传输多了有等待的传输,有错误标志的传输。

APB3到APB4的变化

APB4在APB3的基础上添加了两个端口,一个是PPROT,一个是PSTRB。

PPROT:一种保护信号,可支持APB上的非安全传输和安全传输。

PSTRB:一个写选通信号,用于在写数据总线上进行稀疏数据传输。

PPROT每一位代表的作用不同,总结如下表。

| PPORT | 一种保护信号,可支持APB上的非安全传输和安全传输。 |

| PPROT [0]: | 0:普通;1:特权。一些master使用它来指示其处理模式。特权处理模式通常在系统内具有更高级别的访问权限。 |

| PPROT [1]: | 0:安全;1:非安全。这用于需要更大程度区分处理模式的系统中。 |

| PPROT [2]: | 0:数据;1:指令。该位指示事务是数据访问还是指令访问。此指示仅作为提示,并非在所有情况下都是准确的。 |

写选通信号PSTRB使写数据总线上的稀疏数据传输成为可能。

PSTRB信号可以使写数据总线上的数据片段化,即指示数据总线上那几个字节数据有效。

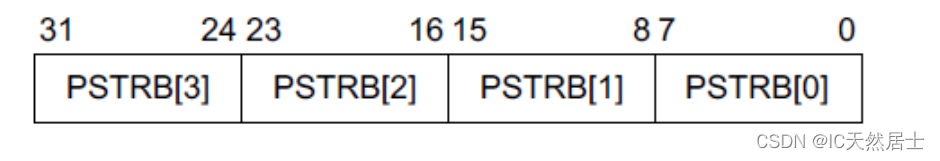

由于数据位最大为32bit,即4个字节。因此PSTRB位宽为4位,每一位对应一个字节,设置为1时,指示该字节数据有效。注意的是,在读操作中,PSTRB所有位必须设置为低电平。

当置为高电平时,写选通脉冲指示写数据总线的相应字节通道包含有效信息。

写数据总线的每八位有一个写选通脉冲,因此 PSTRB [n] 对应于PWDATA [(8n + 7) : ( 8n)]。

下图显示了32位数据总线上的这种关系。

总结:

APB4比APB3又多了两个信号,一个 PPROT 保护信号,一个 PSTRB 写选通信号。

总的来说,APB 读操作时序分为: 无等待,有等待无错误,有等待有错误。

写时序分为: 无等待,有等待无错误,有等待有错误。

959

959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?