EV12AQ605和EV12AQ60 为 Teledyne e2v新推出的高速ADC,相信大家对之前的5G采样的第一代E2V产品并不陌生。

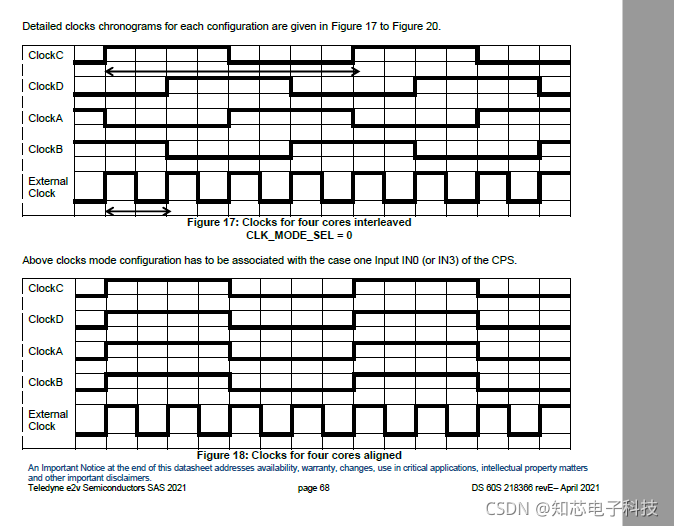

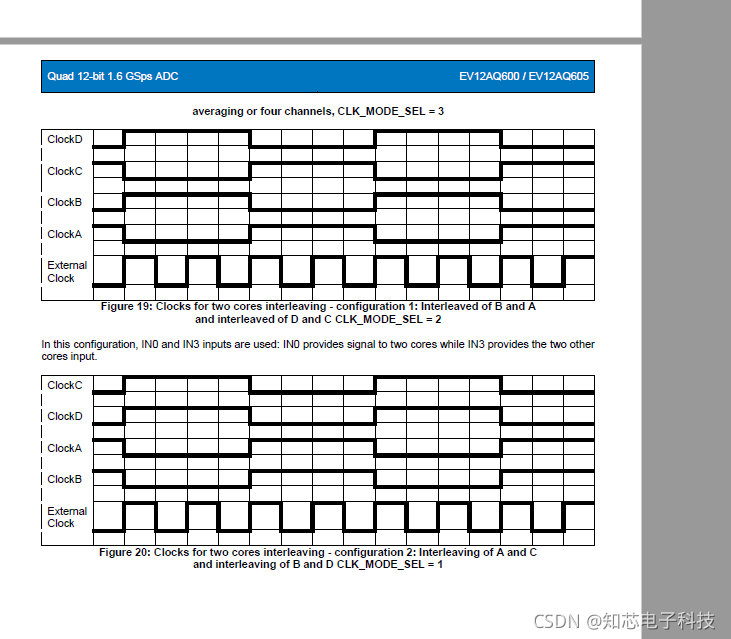

EV12AQ605最高支持6.4G采样率,量化位数为12bit,工作方式和5G采样率的类似,可以4通道独立采样也可以交错单通道采样,不同的是,时钟部分以前如果单通道采样,输入单通道采样率的时钟即可, EV12AQ605即使采样率做4通道独立采样,时钟也为4倍采样率的时钟,例如需要4通道1.6G采样率,时钟需要输入6.4G,时钟关系如下:

接口方面EV12AQ605和主流高速ADC器件一样,采用了高速serdes进行数据传输,相对主流JESD接口,EV12AQ605并没有采用JESD协议,而是自己设计了名为ESIstream的协议,改协议为14/16编码,效率略高与JESD204B的8B/10B编码,另外一大优势就是协议属于免费IP,只需搭载XILINX的transceivers即可,相关链接可以参考

https://semiconductors.teledyneimaging.com/en/products/data-converters/ev12aq600/

程序框架如:

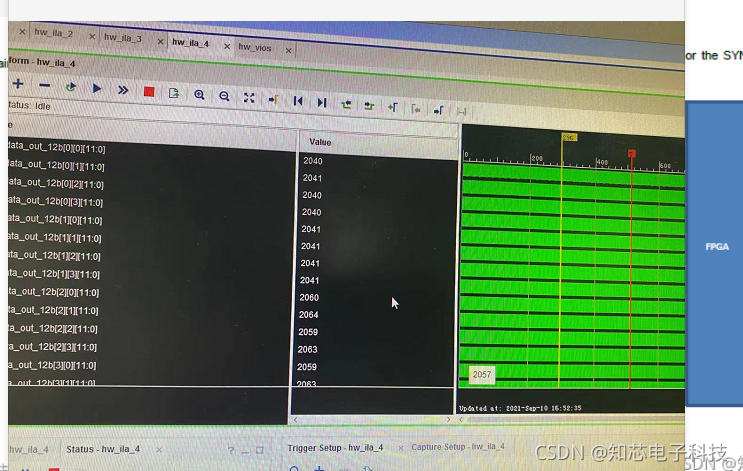

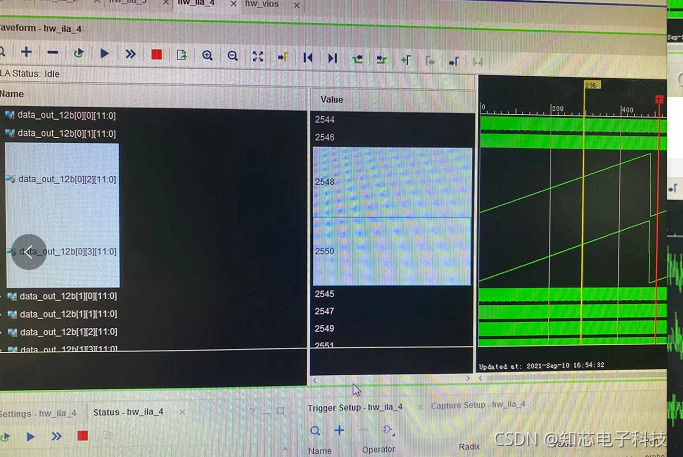

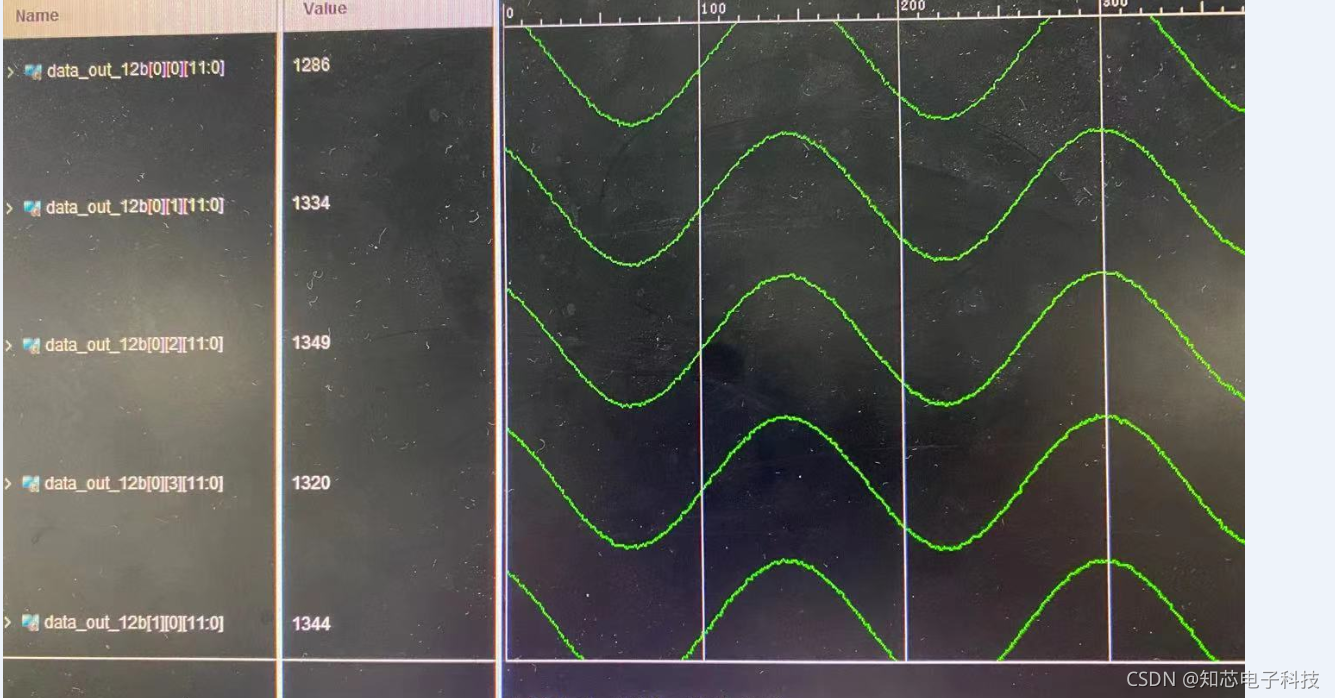

实际效果:

最终得到32相原始数据

硬件:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?