ADRV9361、AD9371、9009是有ADI开发的射频直采芯片。

ADI官方提供的demo都是给予总线架构的,个人认为不方便移植,下面就单独就AD9371的开发架构做一个简单的说明:

ADI官方驱动是基于总线架构的,具体的架构如下图所示:

这种架构,可移植性差,比如AD9371配置可以直接用一个STM32或者其他的单片机来配置,如果用官方的这套框架,是很难移植的。

接下来说下我自己的框架:

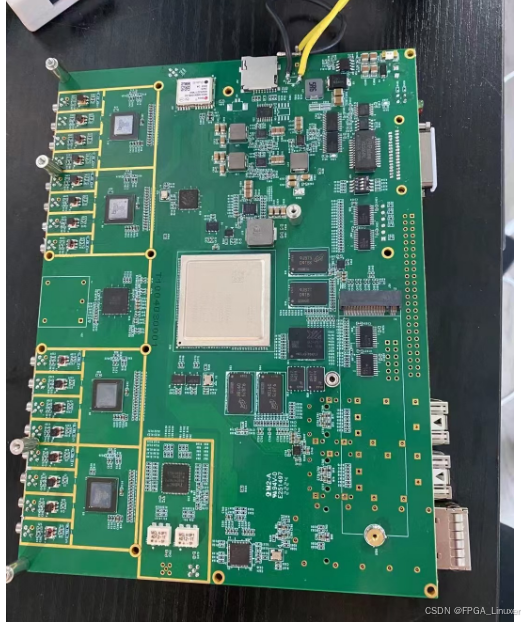

对应的BD文件,如下图所示:

由图可以看出,基本只需要几个emio,就可以搞定,如果移植到对应的MCU上,也只是通过MCU实现一个简单的SPI时序就OK了,对于接收部分,采用的是xilinx的IP核设计(也可以自己设计JESD204B协议实现),对应的程序框架图下图所示:

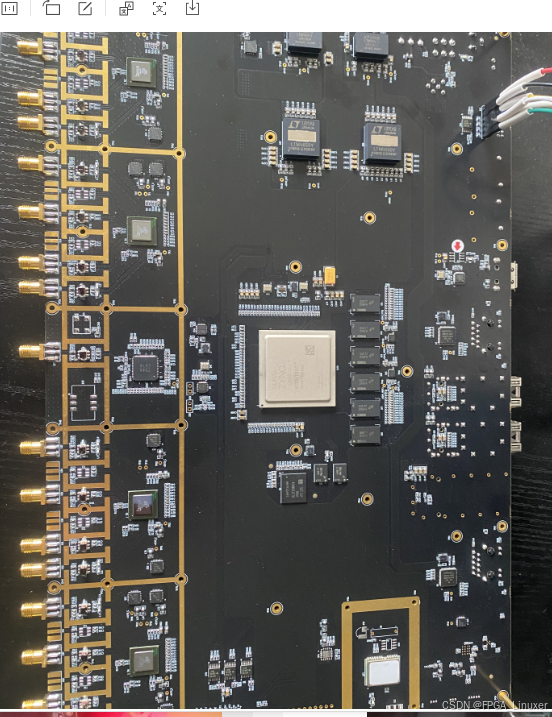

最终效果:

在这里插入图片描述

任意带宽BPSK

总结:本人已经在多个平台上验证,同时具备多片同步的技术,有需要的可以联系本人

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?