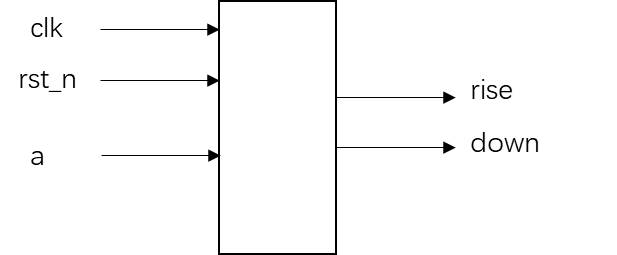

描述

有一个缓慢变化的1bit信号a,编写一个程序检测a信号的上升沿给出指示信号rise,当a信号出现下降沿时给出指示信号down。

注:rise,down应为单脉冲信号,在相应边沿出现时的下一个时钟为高,之后恢复到0,一直到再一次出现相应的边沿。

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,作为待检测的信号

输出描述

rise:单比特信号,当输入信号a出现上升沿时为1,其余时刻为0

down:单比特信号,当输入信号a出现下降沿时为1,其余时刻为0

解题分析

检测信号a的边沿需要缓存信号前一时刻的值,例如记为a_tem。当前一时刻为0,这一时刻为1,说明信号出现上升沿,即 a&&!a_tem = 1; 当前一时刻为1,这一时刻为0,说明信号出现上升沿,即 !a&&a_tem = 1;

输入信号:

系统时钟,复位信号:clk,rst_n;

待检测边沿的信号:a;

输出信号:

上升沿指示信号:rise

下降沿指示信号:down

缓存a的数值

always @(posedge clk or negedge rst_n)

if (!rst_n)

a_tem <= 1'b0;

else

a_tem <= a;

分别使用a&&!a_tem和!a&&a_tem作为判断条件,判断是否出现上升沿或者下降沿。

//检测边沿,给出相应的信号

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

rise <= 1'b0;

down <= 1'b0;

end

else if (!a_tem && a) //当前一时刻a=0,当前时刻a=1,表示a出现一次上升沿

begin

rise <= 1'b1;

down <= 1'b0;

end

else if (a_tem && !a)//当前一时刻a=1,当前时刻a=0,表示a出现一次下降沿

begin

down <= 1'b1;

rise <= 1'b0;

end

else

begin

down <= 1'b0;

rise <= 1'b0;

end参考代码

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output reg rise,

output reg down

);

reg a_tem;

//缓存a的数值

always @(posedge clk or negedge rst_n)

if (!rst_n)

a_tem <= 1'b0;

else

a_tem <= a;

//检测边沿,给出相应的信号

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

rise <= 1'b0;

down <= 1'b0;

end

else if (!a_tem && a) //当前一时刻a=0,当前时刻a=1,表示a出现一次上升沿

begin

rise <= 1'b1;

down <= 1'b0;

end

else if (a_tem && !a) //当前一时刻a=1,当前时刻a=0,表示a出现一次下降沿

begin

down <= 1'b1;

rise <= 1'b0;

end

else

begin

down <= 1'b0;

rise <= 1'b0;

end

endmodule

方法二:

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output reg rise,

output reg down

);

reg apre;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

begin

rise <= 0;

down <= 0;

apre <= 0;

end

else

begin

apre <= a;

if(~apre & a)

rise <= 1'b1;

else

rise <= 1'b0;

if(apre & ~a)

down <= 1'b1;

else

down <= 1'b0;

end

end

endmodule注:解题分析来源于网友,如有侵权,请告删之。

7150

7150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?