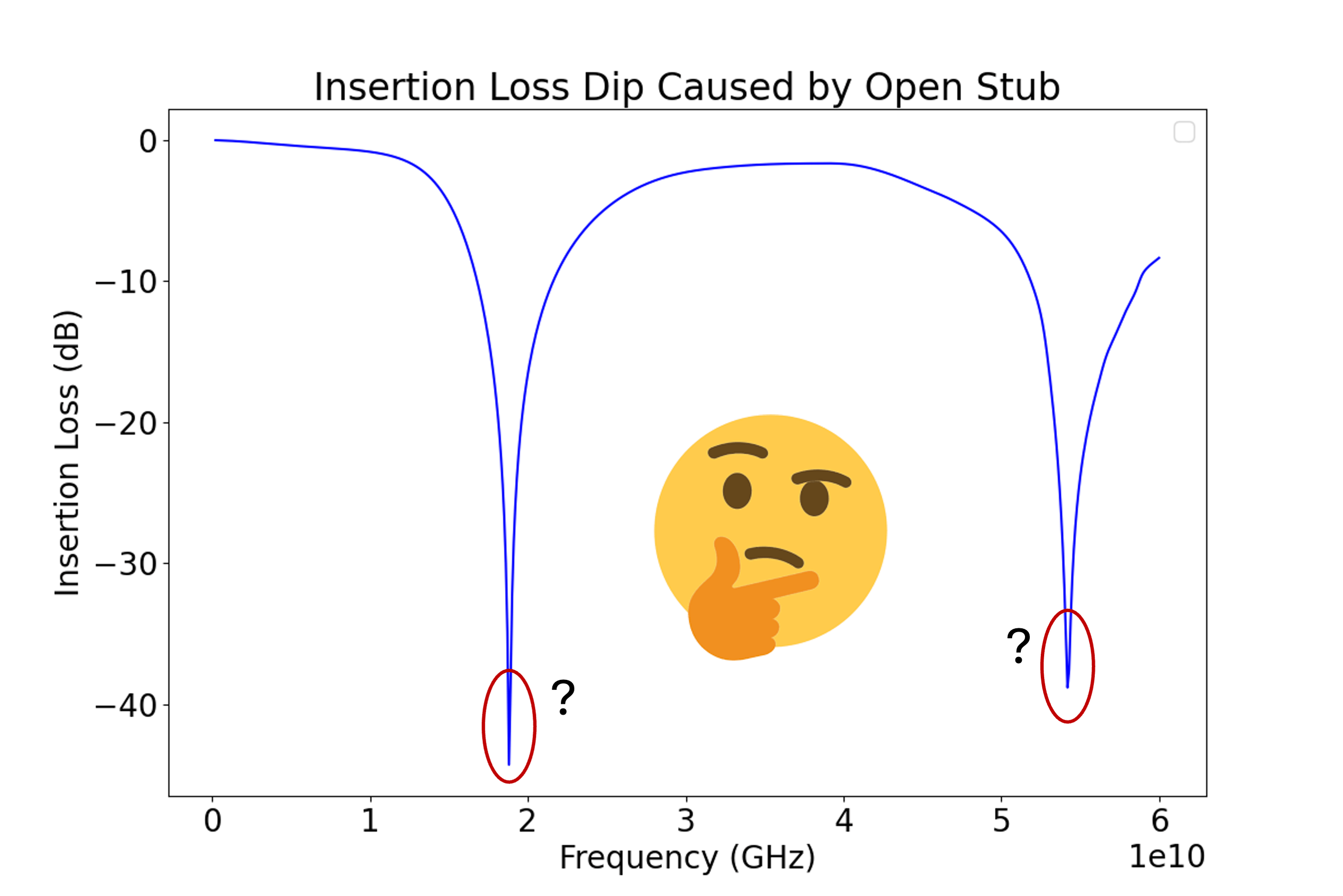

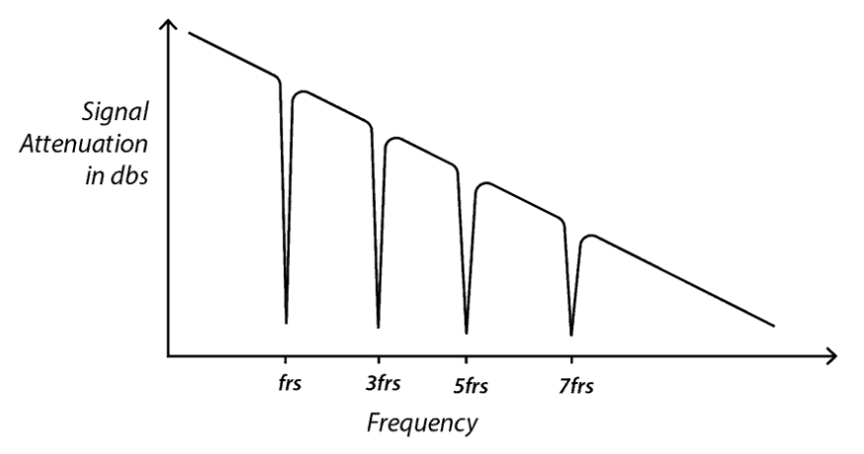

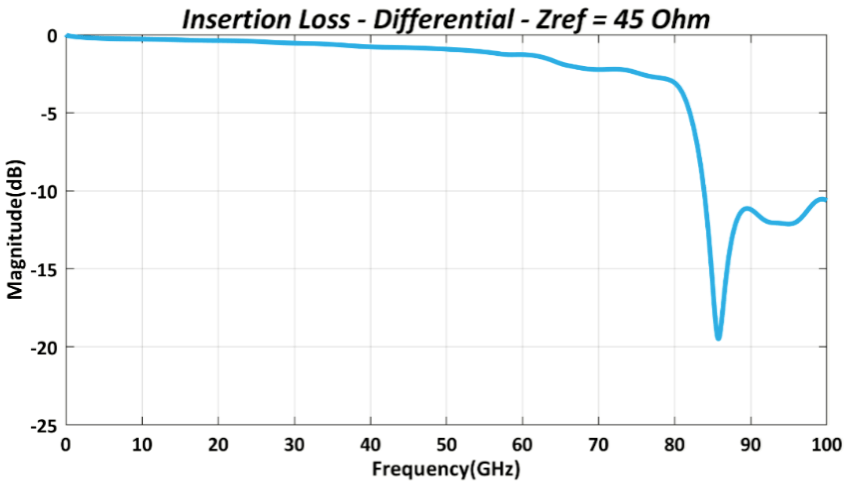

您是否很常跑模拟或是测试时看到这种图? 不知道什么原因一根很深的谐振出现在insertion loss的图上? 这种谐振现象经常对信号完整性造成负面影响,导致严重的反射以及震荡(Ringing),归究其主因,我想大部分都来自于「开路谐振」!

开路谐振的物理机制:反射与驻波

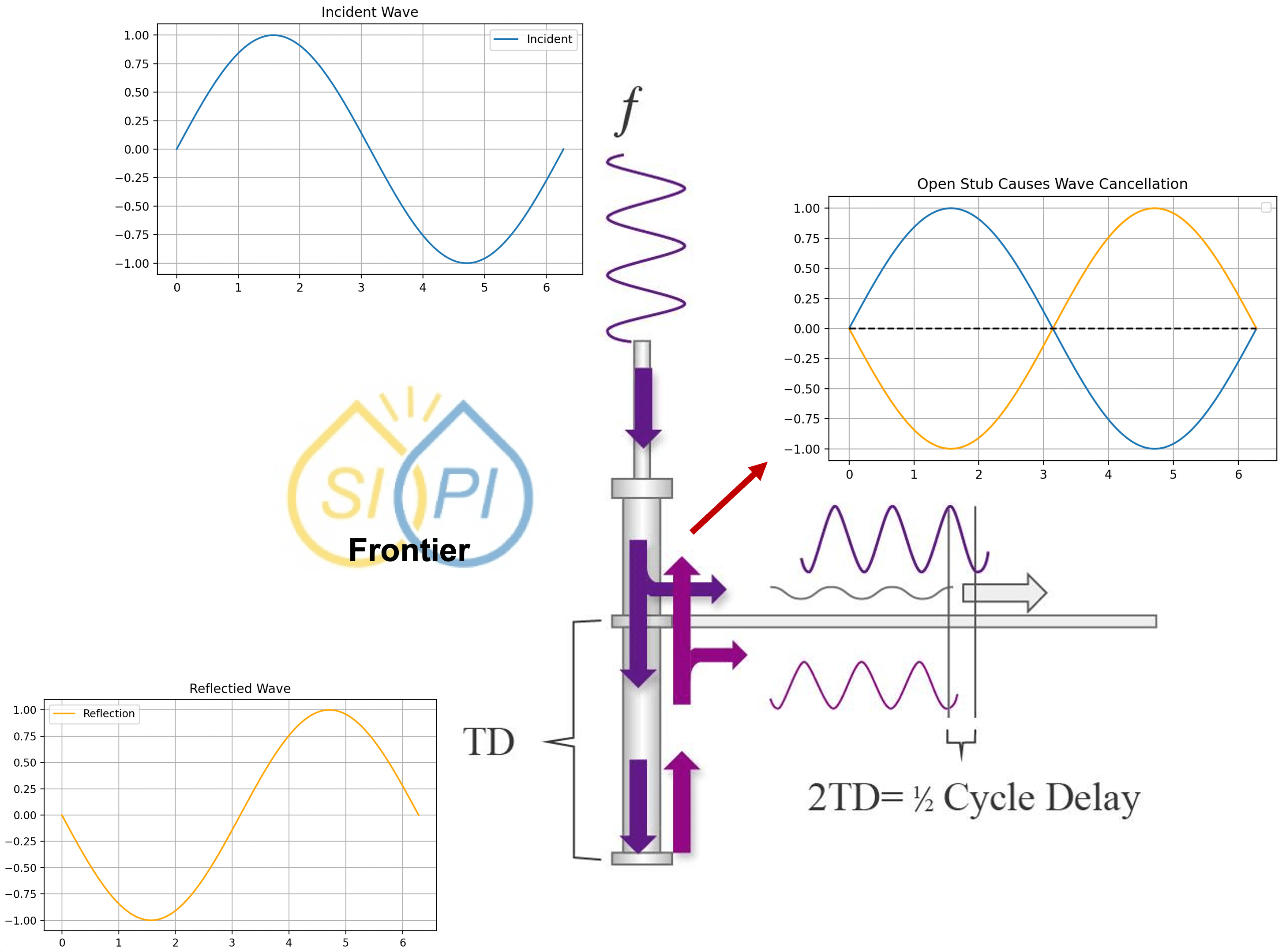

简单来说,当高频讯号在线路上行进时,如果遇到未做匹配处理的开路末端,就会产生全反射现象。 今天我们以Via Stub(过孔残段)作为例子,来看看这个现象是如何产生的,又为什么会对我们的设计造成重大影响!

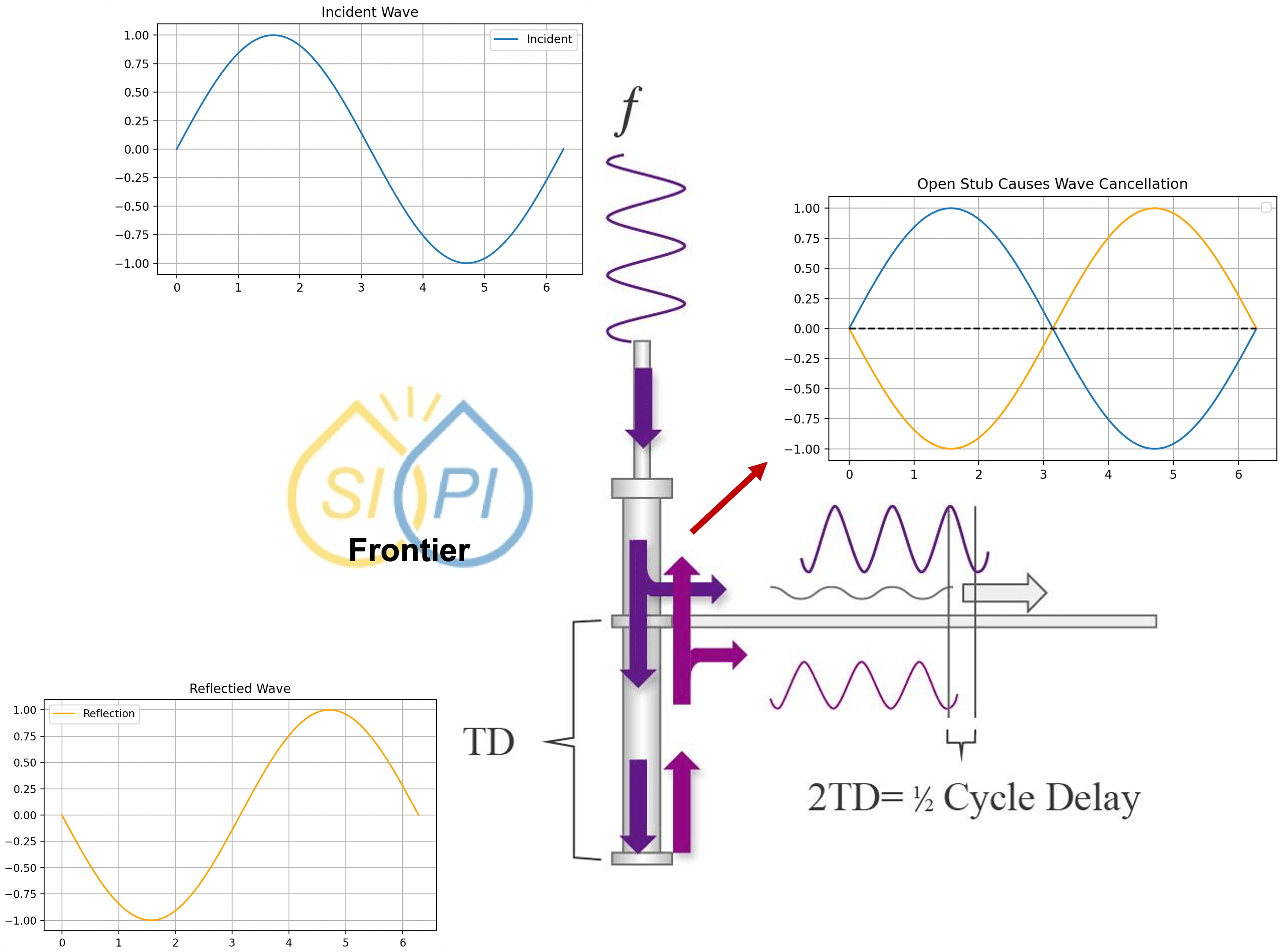

首先,当信号从主线路进入一段Via Stub时,由于该Stub的另一端是开路(也就是说并未接到任何负载或终端),信号到达Stub末端后会发生同相位的全反射。 反射回来的讯号会与原本通过主线路的讯号,在分岔点叠加在一起。 如果这段Stub的长度刚好使得信号从进入到返回的路径比直接走主线路多了半个波长(180度的相位差),那么反射回来的波与原来的波在分岔处就会互相抵销。 这种现象在实务上称作“1/4波长残段谐振”,因为当Stub的长度大约是讯号波长的四分之一时(进出来回就变成半波长),正好满足了形成驻波的条件。

驻波

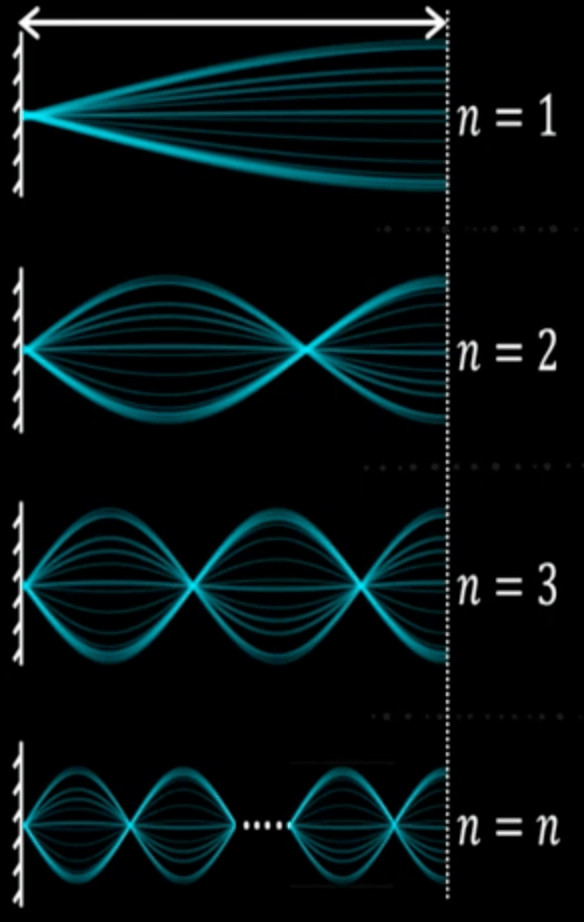

关于驻波,我们趁这机会简单解释一下:

为什么会有驻波? 驻波产生的条件有几种:

- 振幅、频率、波长均相同

- 行进方向相反之两正弦波

产生驻波时会有这些现象:

- 某些位置,质点动位移保持为零,称为「波节」或「节点」

- 某些位置,质点振动的幅度最大,称为「波腹」或「腹点」

- 除节点外,各质点在原处作「简谐运动」(Simple Harmonic Motion, SHM)

- 驻波的波腹与波节保持等距分布

由于驻波会使得波停止不动了,能量完全锁在结构上,所以才会看到insertion loss有个很大的掉落!

开路谐振频率点的计算

假设开路结构(例如Via stub)的长度是L,电磁波在材料中行进的速度v为波长\lambda与频率f的乘积。

v=fλ

前面提到,这种驻波的发生是由于四分之波长残段造成的:

L=λ14

λ1=4L

f=v4L

f=3v4L…

依此类推,可以得到:

f=(2n−1)v4L

L=(2n−1)v4f

n为整数:1, 2, 3...

开路结构固定的情况下,从数学公式来看,这个驻波发生的谐振频率点会每隔固定的频率间隔出现; 从结构层面来看,满足一端短路另外一端开路的正弦波可以是以下这几种,正也符合数学公式所呈现的结果。 这也是为什么在最前面那张图会看到第二个谐振点的缘故!

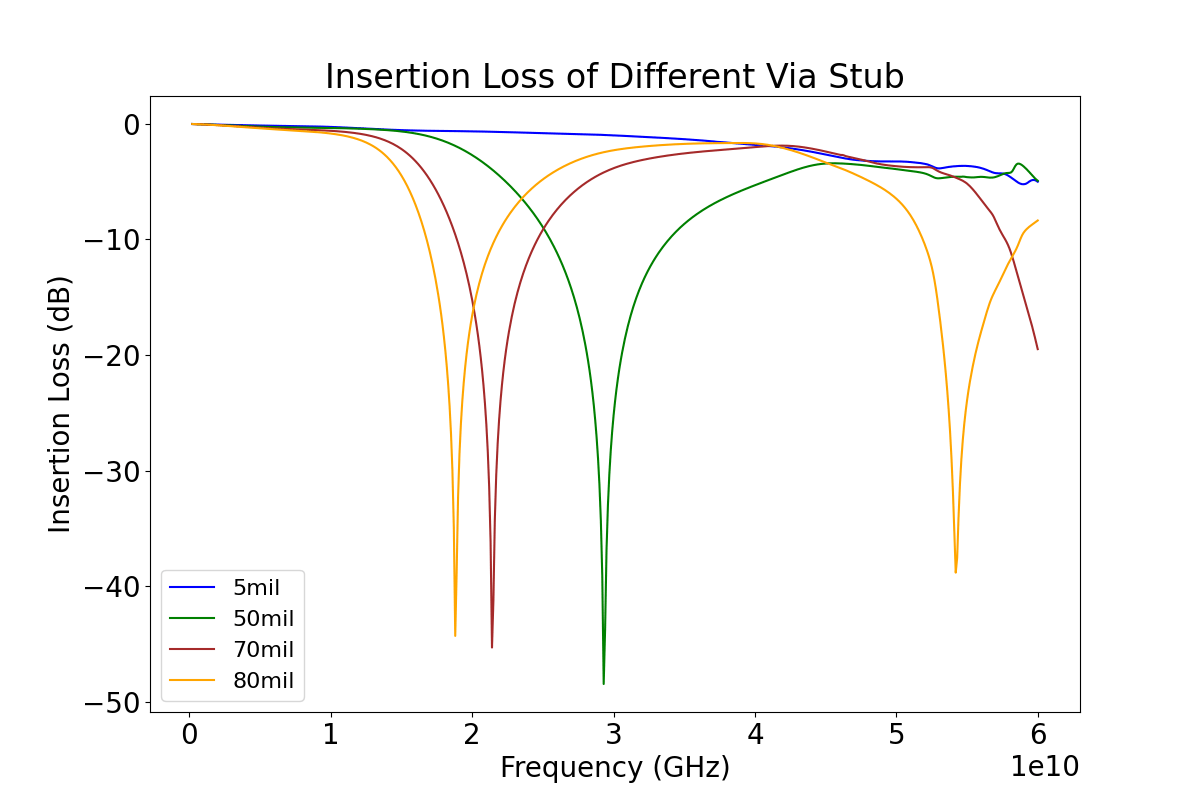

且也可以得知,开路结构越短越小,谐振频率点会越高频,对于高速数字讯号而言会越优异!

3大常见的开路谐振与解决方法

产生开路谐振的结构其实有不少种,但是几乎每个高速产品都会遇到的开路谐振,有以下这几种:

PCB的Via Stub

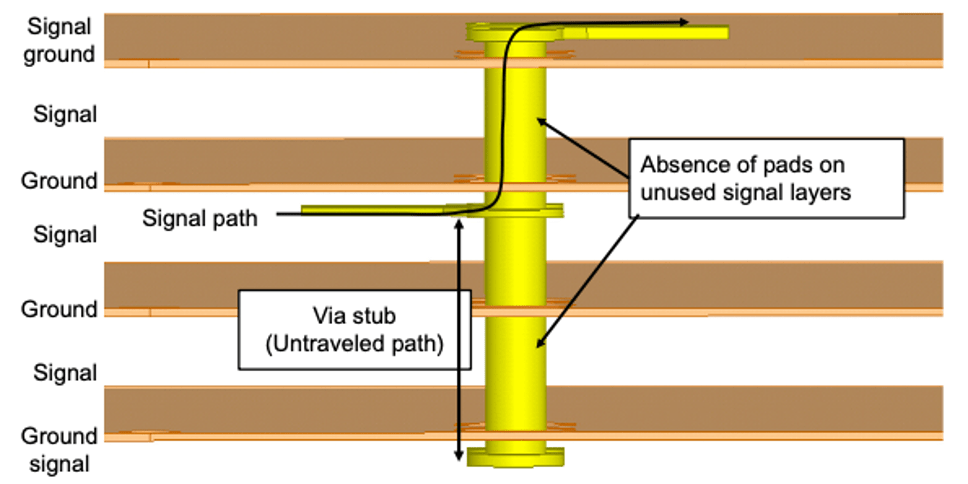

在印刷电路板工艺中,讯号层之间的连接需要通过机械钻孔的方式。 当讯号由表层进入内层时,通常会在Via内留下不必要的金属段,也就是所谓的残段。

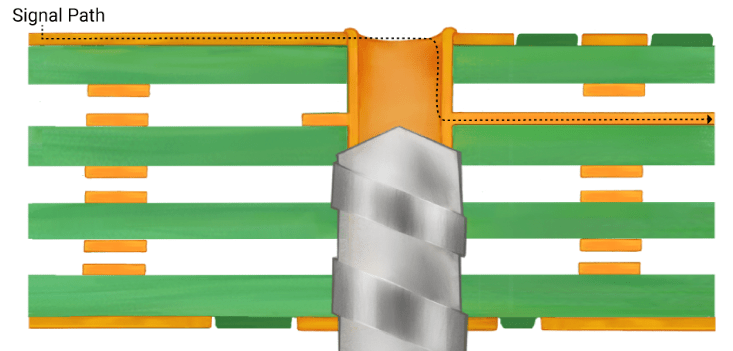

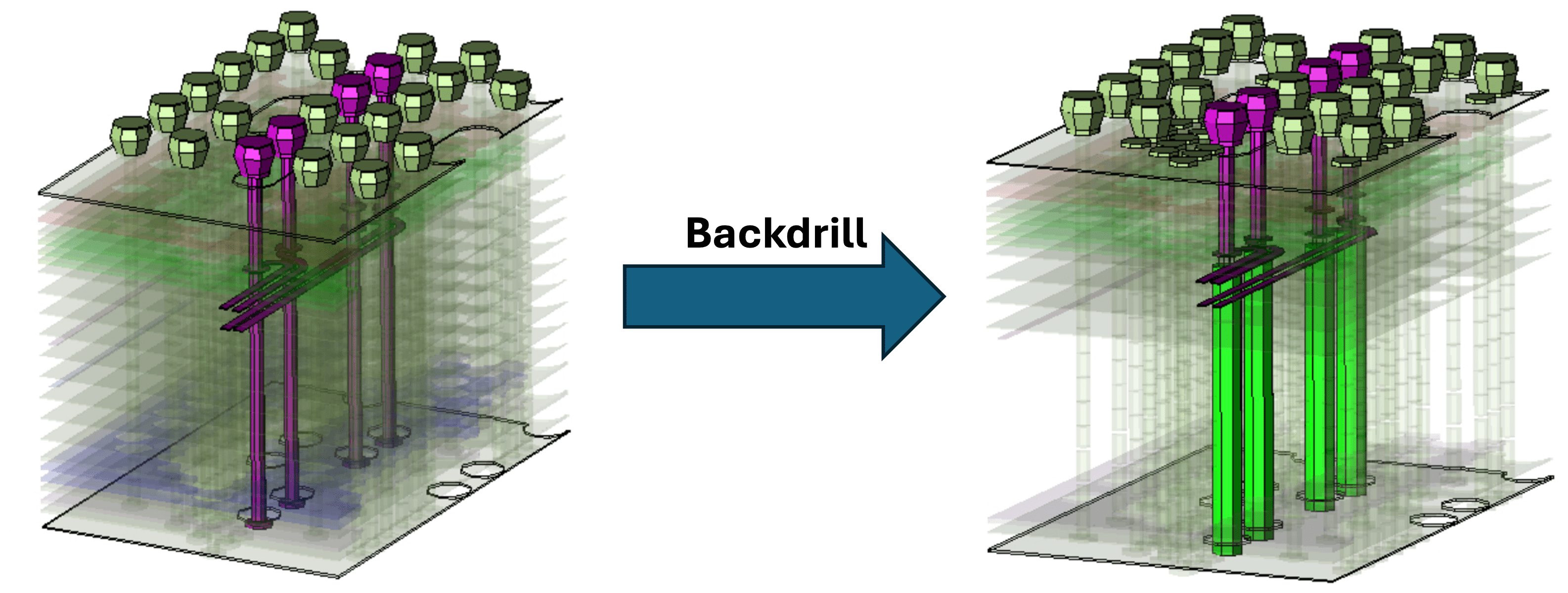

最经济的解法是透过背钻工艺,使用更粗的钻头从Via的背后再钻一次,目的是将不需要的金属部分去除,理想上当然希望将这个残段全部钻掉。 然而,实际生产中,由于钻孔精度及加工限制,无法完全清除所有残留部分,常常还是会留下少量的金属残段!

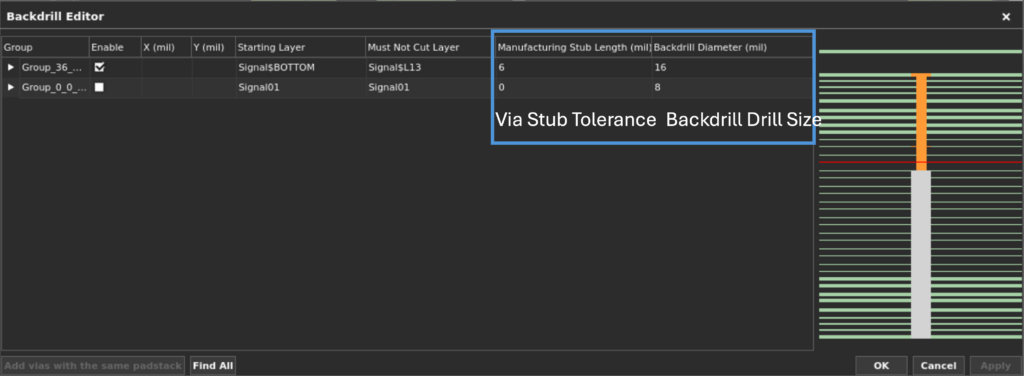

背钻后,Via Stub变短(目前已知最强的工艺是最大保留5mil),我们可以透过Cadence Clarity去模拟不同背钻长度造成的SI表现,我们点按Via之后,按右键选择Backdrill Editor,可以直接设定您需要的Via Stub Tolerance与背钻的钻头尺寸。

Clarity设定完背钻信息后,可以看到,绿色的是背钻掉的洞,这也算是一个对象,可以针对这个物件设定材料,这里其实很关键,背钻后的洞到底会是什么材料? 模拟又该如何设定? 对于高频设计的结果会不会差异很大? (这部分先留给各位思考,有兴趣欢迎留言或寄信讨论! )

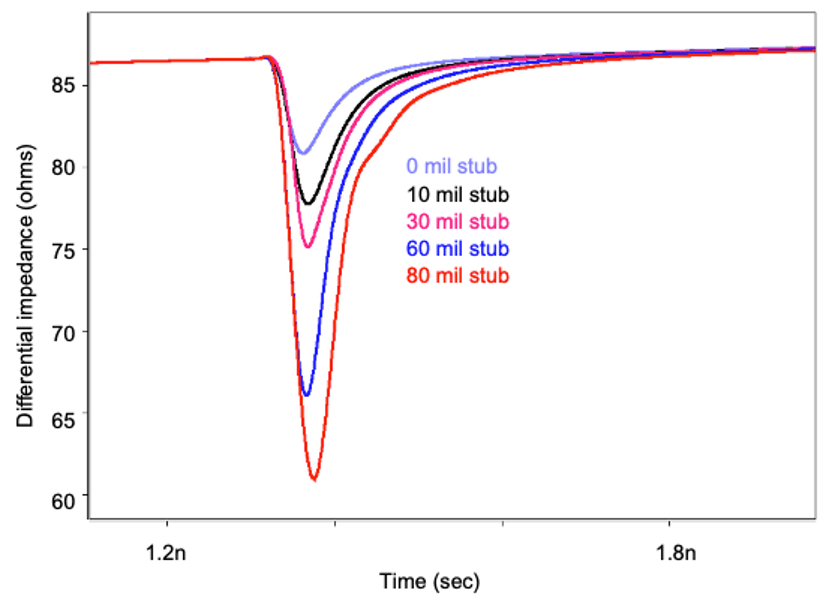

模拟结果告诉我们:越短的Stub,Insertion Loss的谐振频率越高,寄生电容降低带来更小的瞬间阻抗变化,换句话说高速数字讯号的带宽越宽,SI特性越好!

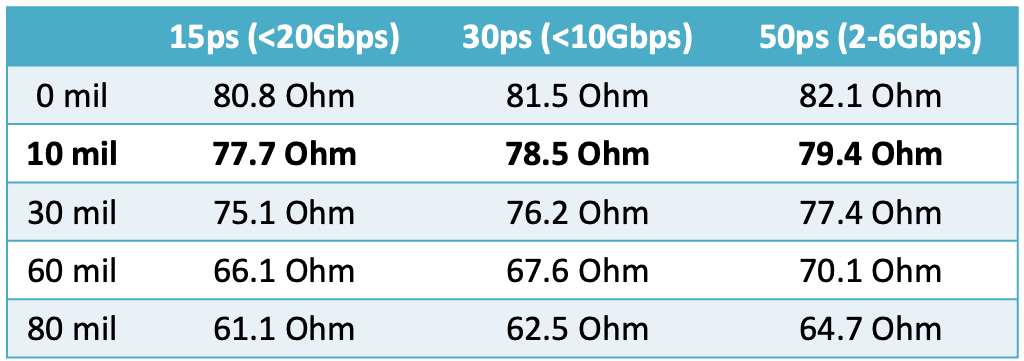

可允许的Via Stub长度

或许您会问,Via stub到底多短才够? 我们工作中已经被问过无数次这个问题,几乎每个硬件设计都会想知道,到底Via stub够不够短? 我们真的需要做背钻吗?

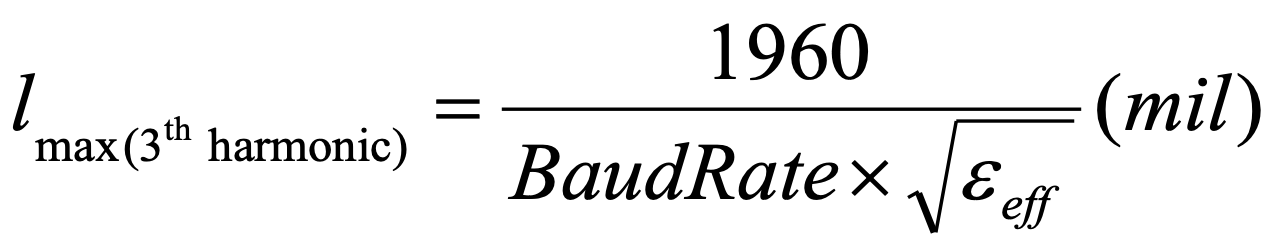

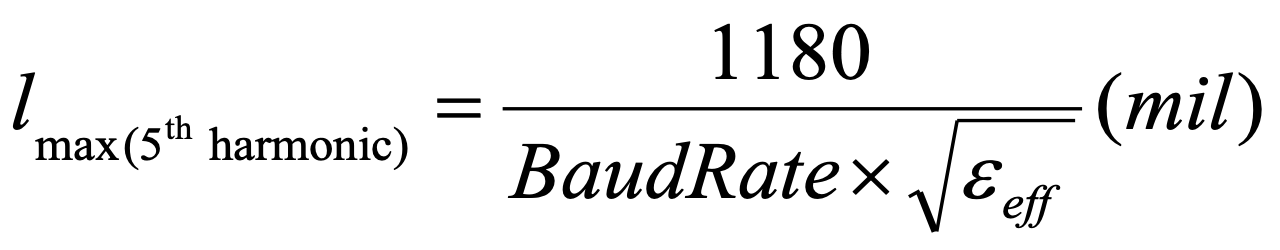

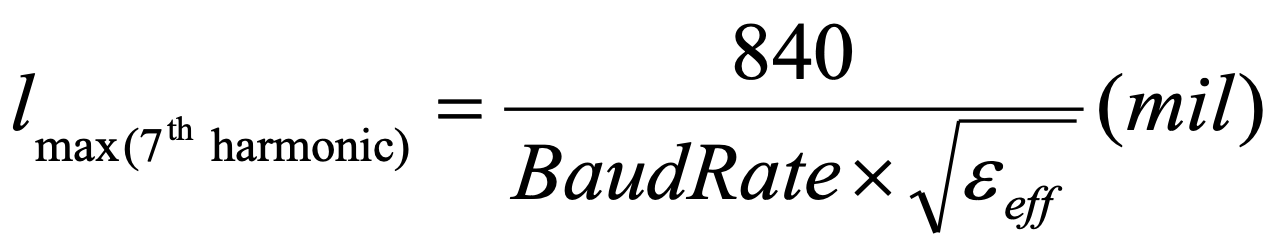

这点各位可以通过下面的公式去得到答案,这公式是我们根据上述的数学公式反推的。 由于上面提到的数学公式只是预测谐振点而已,各位看到前面的模拟图就知道,绝对需要再把有效带宽往更低频看,最好是只看到线性区域,这才符合SI所要求的目标。

所以根据这些条件经由种种计算,得到以下结论:

您只要先知道到底您想看到多少谐波项? 或是说您需要多少带宽?

如果带宽需求高,这样Via stub的理想长度得更短喔!

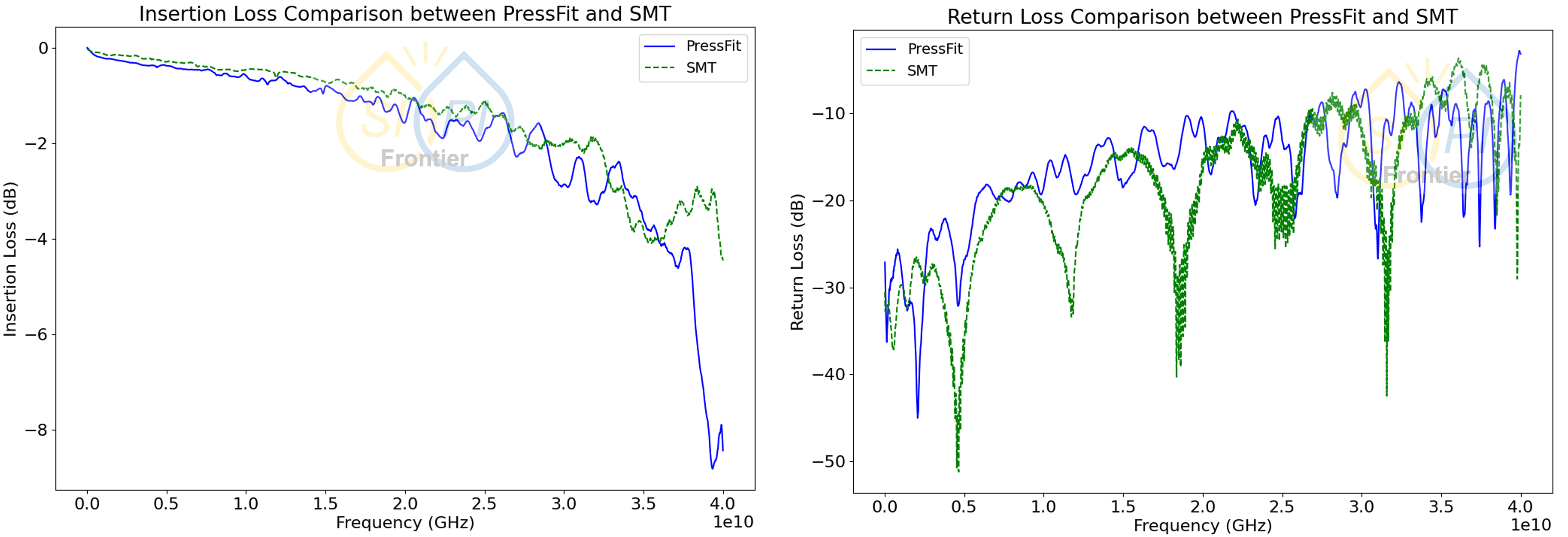

Edge Card Connector

虽然我们先前提过,BGA形式的connector已经广泛用于高速产品上,因为其具有较小的PCB pad,阻抗控制较容易,SI特性极佳! 但在一些分离式接口的连接上,例如QSFP-DD与OSFP,还是得仰赖Edge card connector提供较佳的机械强度。

这种connector的弹簧片与PCB pad的接合位置,也是一个open stub,在高频处也会产生驻波。 如果弹片连接点与PCB pad的末端是0.6mm(我们称作这是Wipe length),而弹片连接点与弹片末端是0.9mm的长度,则驻波频率大约会发生在84GHz,以目前的224G-PAM4来看应该还不会有太大影响,这种设计优化还是留到下一世代 – 448G,再来思考吧。

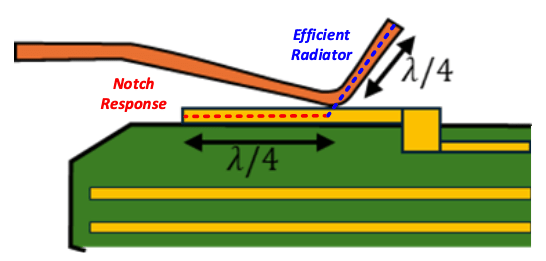

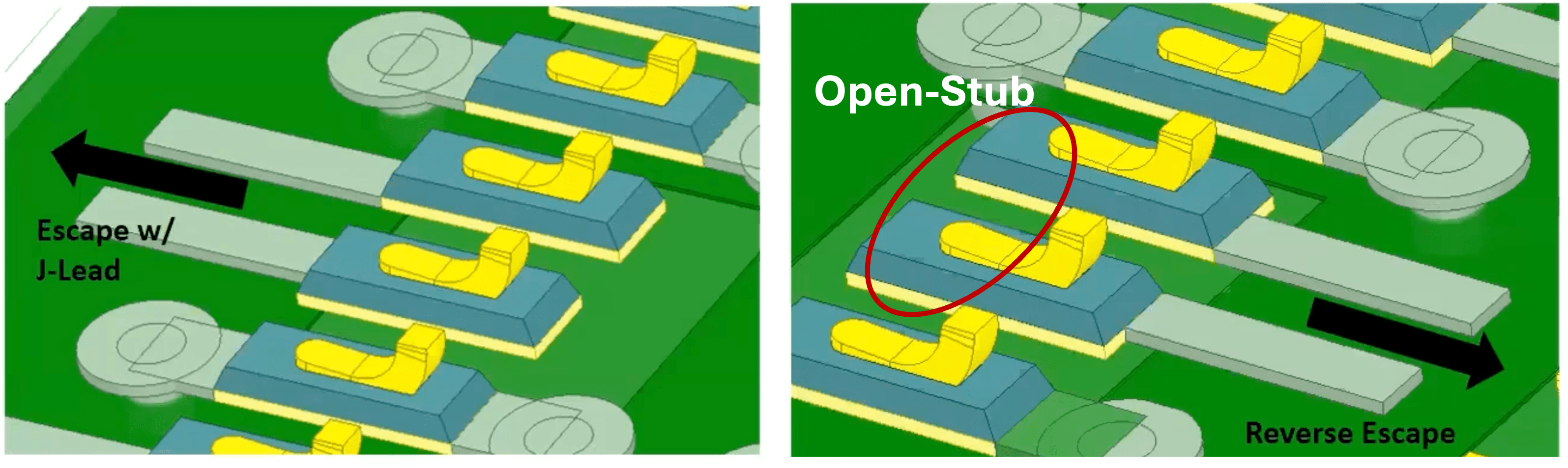

SMT Connector的出线方向

还记得我们在这篇文章中提到SMT connector的出线方向不能跟引脚的方向相反,否则结构上会产生一个较长的开路谐振结构,严重影响SI的特性!

基本上开路谐振是一定会存在的,在一个大系统上很难去避免这种结构,对于设计者而言我们能做的就是透过设计、制造工艺去做补偿,或是说将谐振频率点往高频推移!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?