高速SerDes讯号SI分析,第一步是根据通道损耗规格决定PCB叠构与PCB材料(我们在这里有分析过),其中包含:

- CCL材料选择(包含:树脂系统、铜箔、玻璃纤维布)

- Core/PP厚度设计

- 玻璃纤维布种选择

- 传输线阻抗设计,决定差动对的线宽/线距

- PCB总层数

CCL材料介绍

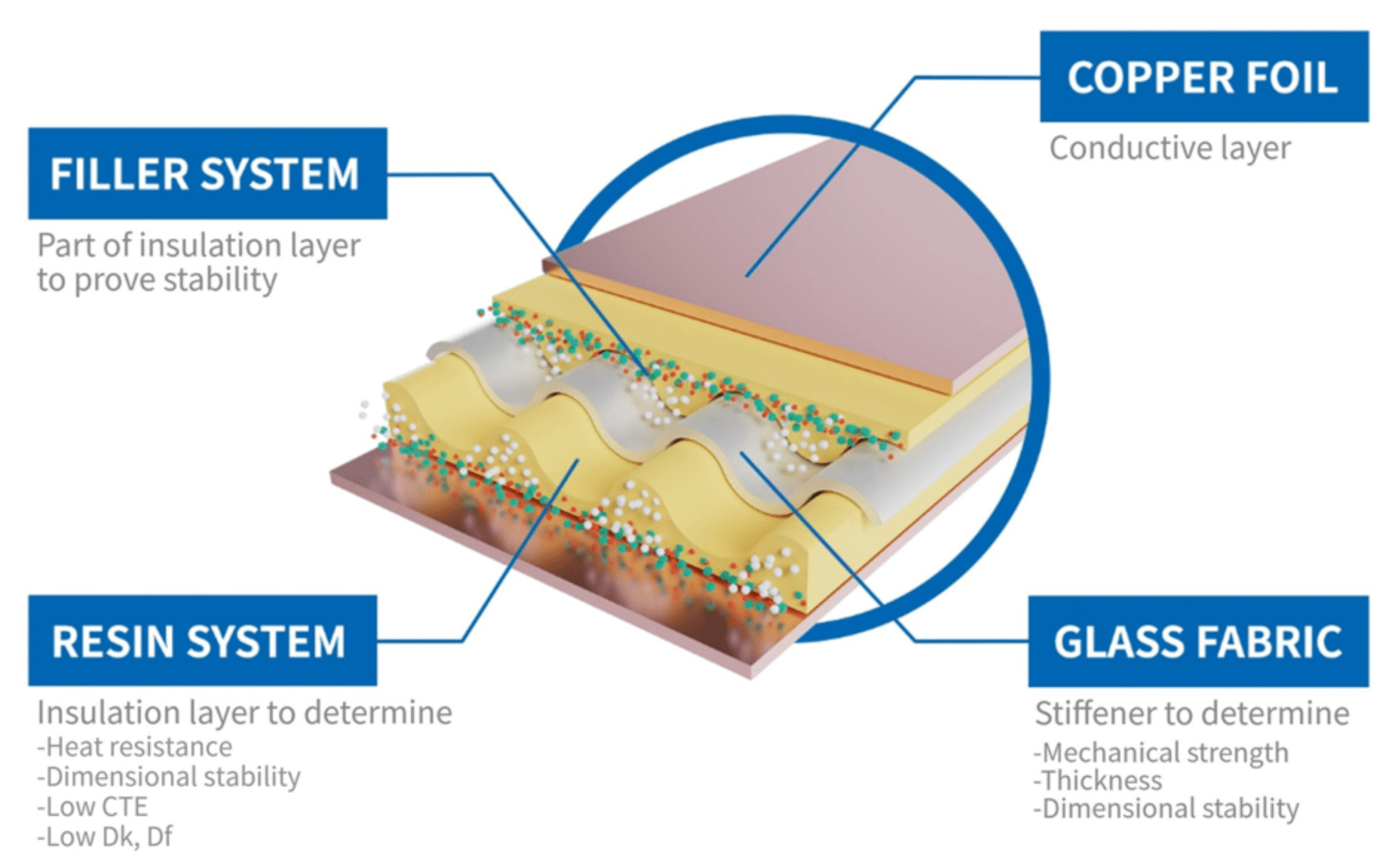

CCL(Copper-Clad Laminate)或者说是覆铜基板,是PCB材料的一种形式,在硬板上几乎无所不在。

那么 CCL 里头到底是什么组成的呢? 其实主要包含几个关键材料:

- 树脂(Resin):这是CCL的「胶水」,负责把所有材料黏在一起,并提供绝缘效果。

- 填充物(Filler):这些是加入树脂里的粉末状物质,主要用来调整机械强度、热膨胀系数 (CTE),这个也是影响损耗参数(DF)的最大因子。

- 铜箔(Copper foil):提供导电路径,表面粗糙度会影响高频讯号的损耗。

- 玻璃纤维布(Fiber weave):提供 CCL 机械强度,避免基材变形,Low DK布有着良好的损耗表现。

CCL材料损耗

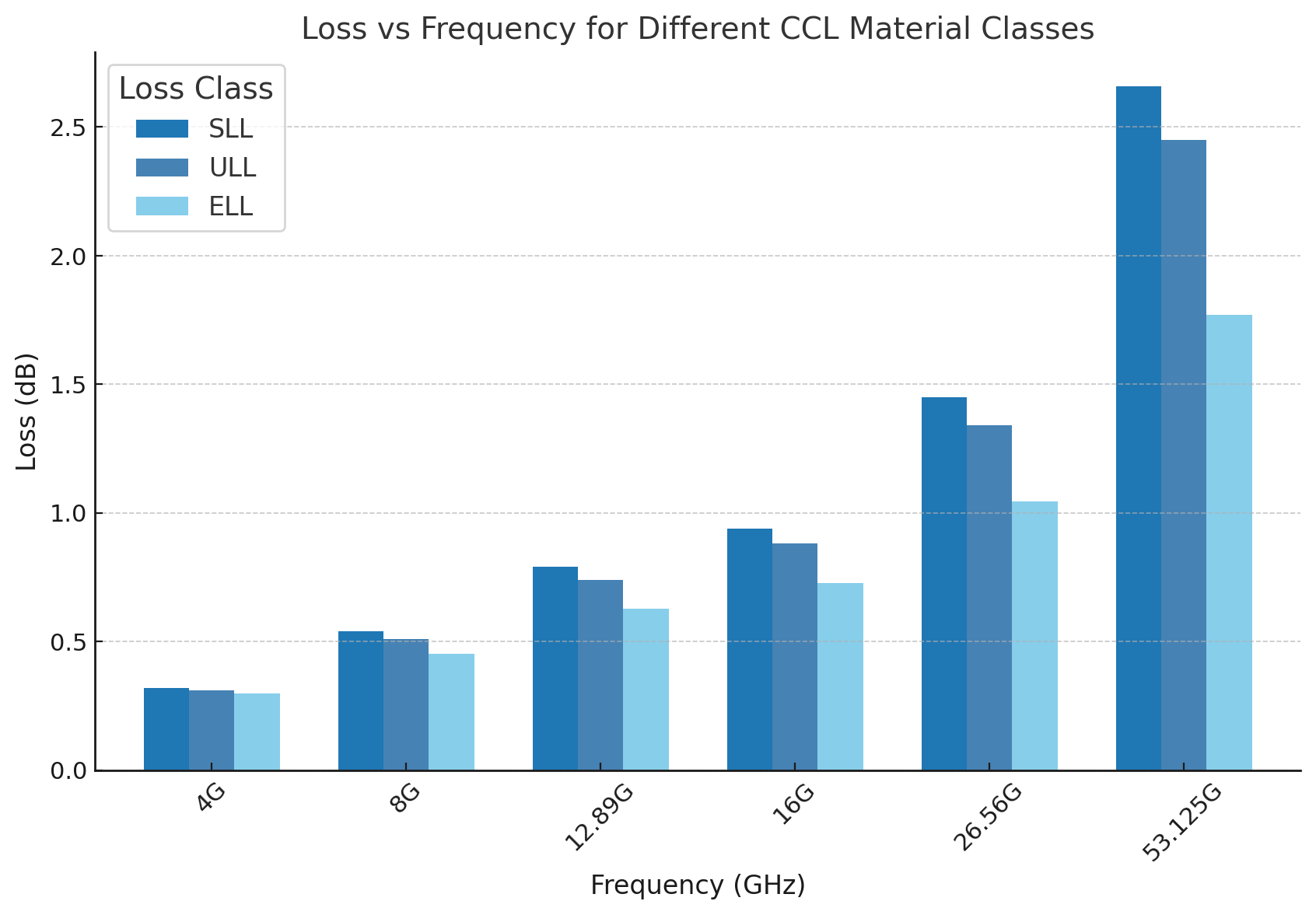

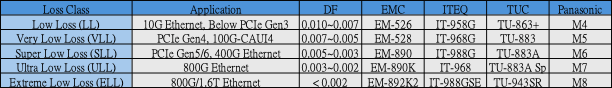

在高速PCB设计中,选择合适的材料是必要的起手式,因为不同材料的损耗会直接影响信号完整性和走线长度。 为了区分不同等级的高速材料,各大板材厂、终端CSP和芯片设计商都会制定自己的分类方式,但命名规则各有不同。

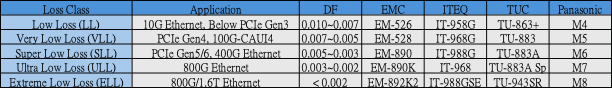

一般来说,常见的材料等级会用 Low Loss (LL)、Very Low Loss (VLL)、Super Low Loss (SLL)、Ultra Low Loss (ULL)、Extreme Low Loss (ELL) 这类名称来标示,或是拿传统CCL大厂Panasonic的命名方式来对标(M4~M9), 等级越高表示材料的介电损耗DF逐渐降低。 简单来说,损耗越低,适用的频率越高,价格当然也会越贵。

根据损耗能力分类CCL

以下是常见的等级划分、对应材料与应用领域:

- Low Loss (LL)

- 适用于 10G以下 应用,如 10G Ethernet、Below PCIe Gen3

- DF值约在 0.010~0.007

- 常见材料:EMC EM-526, ITEQ IT-958G、TUC TU-863+, Panasonic M4

- Very Low Loss (VLL)

- 适用于 10G ~ 25G 应用,如 PCIe Gen4、100G-CAUI4

- DF值约在 0.007~0.005

- 常见材料:EMC EM-528, ITEQ IT-968G、TUC TU-883, Panasonic M5

- Super Low Loss (SLL)

- 适用于 32G-NRZ, 56G ~ 112G PAM4 应用,如 PCIe Gen5/6、400G Ethernet

- 介电损耗 (DF) 约在 0.005~0.003

- 常见材料:EMC EM890, ITEQ IT-988G、TUC TU-883A, Panasonic M6

- Ultra Low Loss (ULL)

- 适用于112G PAM4及以上,如800G Ethernet

- DF值约在 0.003~0.002

- 常见材料:EMC EM-890K, ITEQ IT-968、TUC TU-883A Sp, Panasonic M7

- Extreme Low Loss (ELL)

- 目前最高等级的高速材料,适用于 224G PAM4、800G/1.6T Ethernet

- DF值小于0.002,甚至能接近PTFE

- 常见材料:EMC EM892K2, TUC TU-943SR, ITEQ IT-988GSE, Panasonic M8

🎯 帮大家做个总结

铜箔损耗

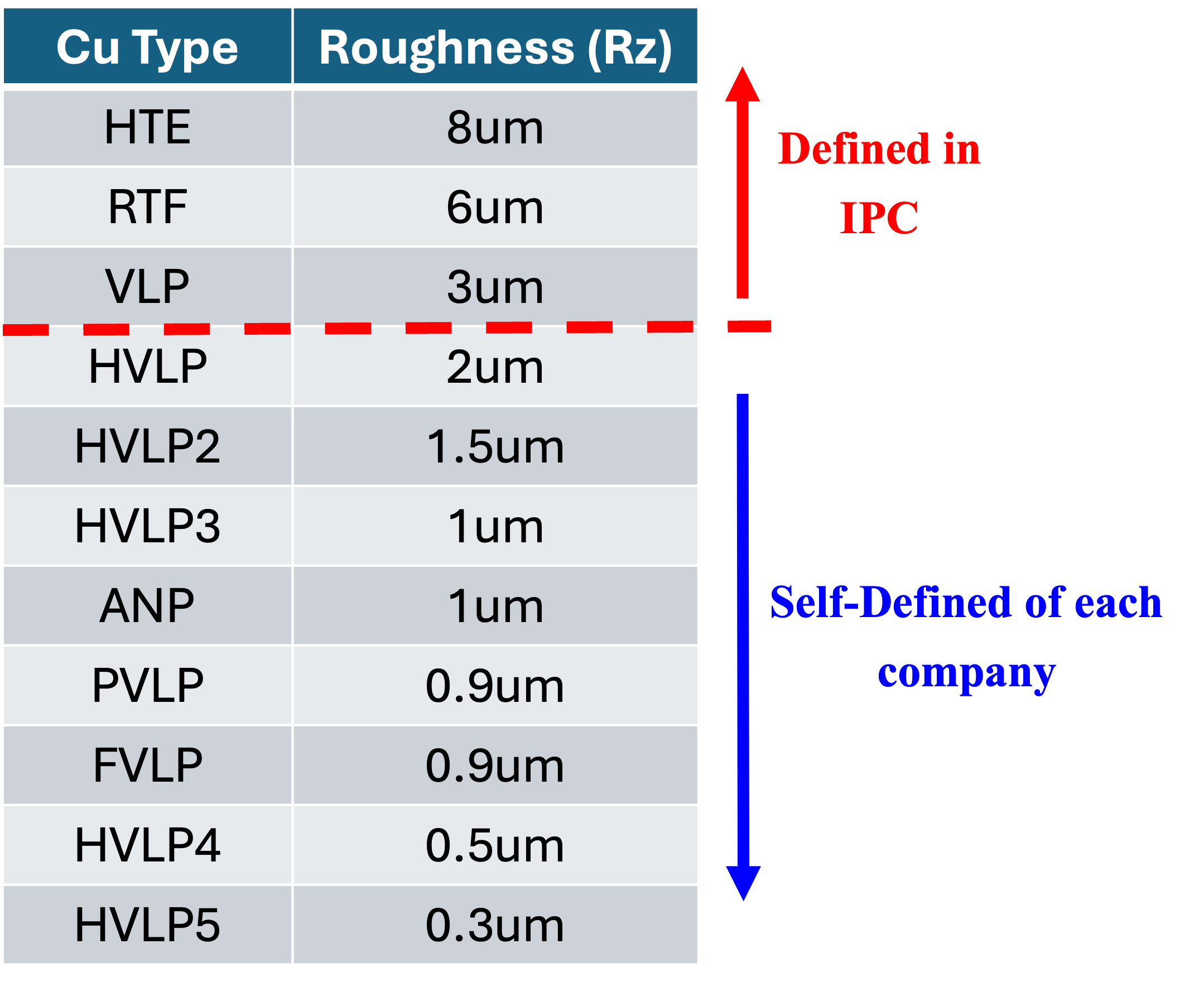

除了树脂系统的改良之外,铜箔的进步也是推动高速CCL持续优化的主因。 国际印刷电路板组织IPC定义的铜箔等级最高只到VLP(Very Low Profile),等级再往上就进入了战国时代,每家铜箔厂与CCL厂都有自己的名称,常见的如HVLP(Highly Very Low Profile),目前最高等级已经到达HVLP4甚至HVLP5。

p.s. 有些人的HVLP4跟HVLP5的铜箔等级是一样的,不能单纯以命名来分类CCL的差异!

什么是铜箔粗糙度?

铜箔的等级差异,主要来自于粗糙度(Roughness),市场上不同等级的铜箔,主要就是通过降低粗糙度来提升高速传输性能。

根据不同测试方法,可以将粗糙度的定义区份成Ra或是Rz。

1️⃣ Ra (Arithmetic Average Roughness,平均粗糙度)

- 计算的是测量区域内表面高度的平均值,不考虑最大与最小的变异。

- Ra 值较小的铜箔表面较为平滑,但它无法完整反映极端峰值 (高点或低点) 的影响。

- 常用于一般机械加工与金属表面检测,但对于铜箔来说,Ra 有时不足以评估其对高速信号的影响。

2️⃣ Rz (Mean Peak-to-Valley Height,十点平均粗糙度)

- 测量样本区域内的五个最高点与五个最低点的距离平均值,因此能够反映表面凹凸的极端变异。

- Rz 的数值通常比Ra高,因为它包含了表面最不规则的区域,能更真实地描述铜箔对高速信号的影响。

- 高速PCB设计更常参考Rz,因为信号传输时,电子会受到局部表面不规则性的影响,而Rz能够提供更贴近实际的数据。

我们常用的粗糙度SI分析模型是Huray Model,这个模型主要以Rz为主要参数去做计算(原因上面有提),因此我们在选择铜箔时主要分析的是Rz。

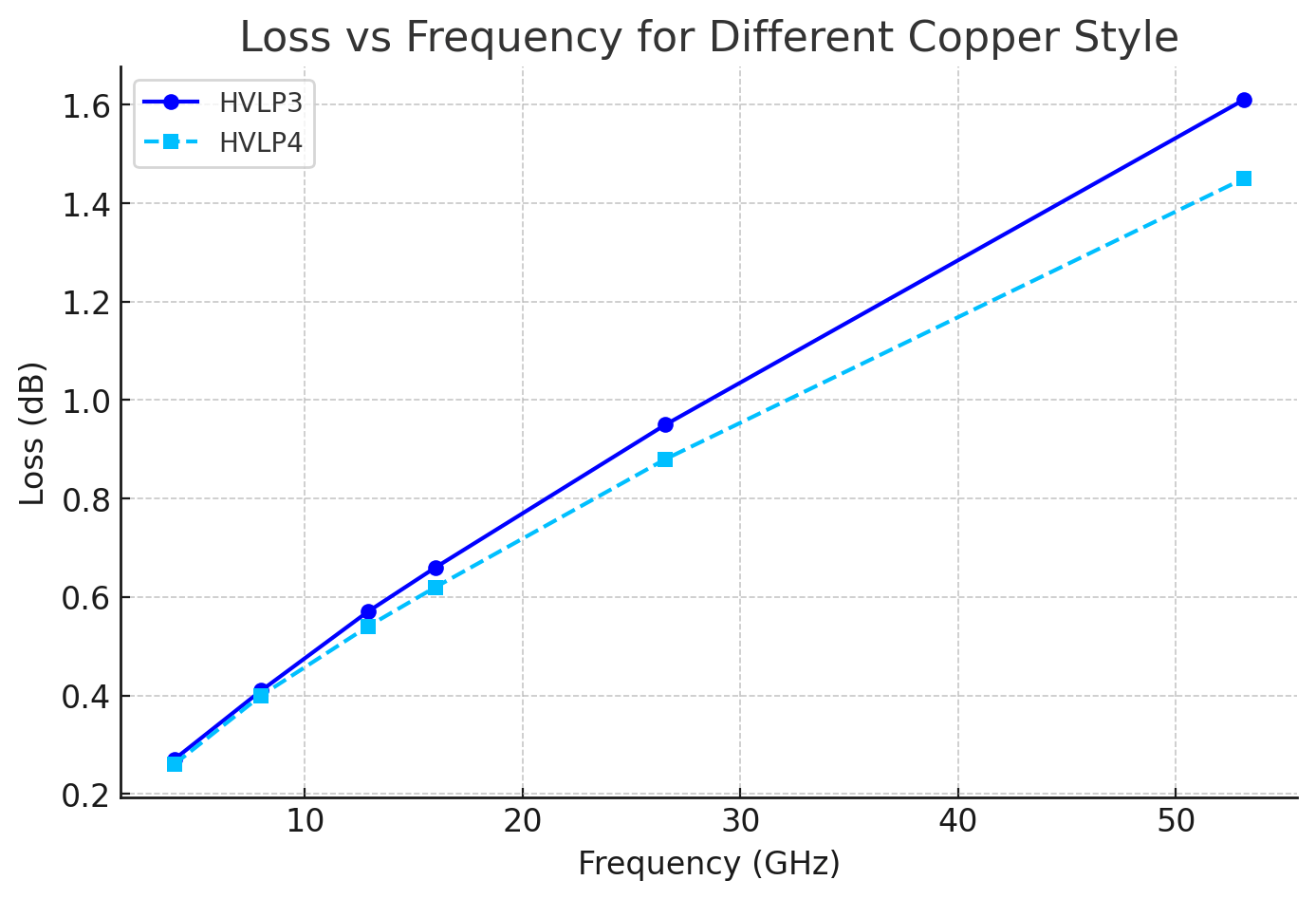

铜箔粗糙度对损耗的影响

Data Rate越快,频宽越高频,铜箔损耗的影响越大,可以看出在53GHz时,HVLP4的损耗离HVLP3的损耗差距变得很大。

玻璃纤维布

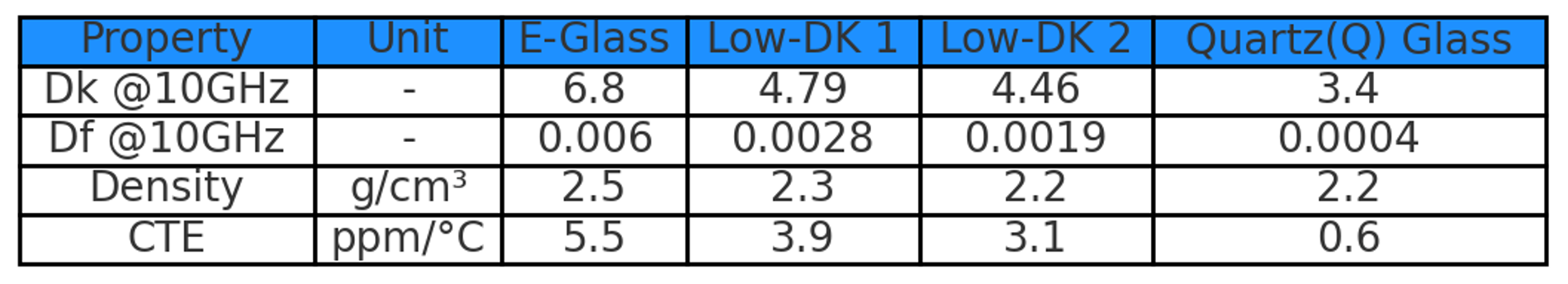

玻纤布(Fiber Weave)强化了CCL的机械特性,让CCL更坚固。 根据DK/DF值,玻纤布的开发已经来到第四代,依序为E-Glass, Low-DK 1, Low-DK 2和石英(Q)布。

传统E-Glass布的DF比较大,连带导致使用此布种的CCL有着较大的损耗,通常应用在PCIe Gen4以前的世代,或其他中低速讯号的应用。

Low-DK 一代布的开发

然而,随着在400G switch进入市场,由于更高频的损耗要求,Low-DK一代布的开发,使PCB损耗在13.28GHz频率下,损耗得以达到0.7dB/inch@13.28GHz。

常见材料:EMC EM890K、TUC TU-943SN

Low-DK 二代布的问世

当 800G switch 开始被市场广泛采用,尤其是在 112G/224G-PAM4 等应用中,Low-DK 一代布 的特性已经逐渐逼近极限,无法满足更高频率下的低损耗需求。 因此,Low-DK 二代布应运而生,这一代材料透过进一步降低玻纤布的 DF,并且搭配更高等级的树脂系统,成功让 PCB 在 26.56GHz 频率下,损耗控制在 0.85dB/inch。

这样的提升幅度是相当惊人的,因为理论上,损耗会随频率线性增加,以 Low-DK 一代布为基准,在 26.56GHz 的损耗应该会达到 1.4dB/inch,但二代布成功将损耗降低近 40%。 这意味着在 800G switch 设计 中,使用二代布的 PCB 能够显著提升 BER (Bit Error Rate) 表现,并确保更长距离的讯号传输可行性。 因此,自 2024 年开始,Low-DK 二代布 逐渐成为高阶数据中心与交换机应用的标准材料之一,许多 CCL 厂商也将其纳入主力产品线。

进入2025年,产业将迎来1.6T交换机(1.6T switch)和224G-PAM4的产品开发,各大网通ODM也将陆续推出搭载Broadcom最新一代网通芯片TH6的产品。 这颗芯片具备512 lanes的224G-PAM4接口,总带宽高达102.4Tbps,是目前市场上最高阶的交换机解决方案之一。

根据目前对市场的理解,Low-DK二代布,尤其是台光电的EM892K2,仍然勉强能够支撑1.6T switch在Optical Transceiver应用上的需求。 不过,这样的选择必须牺牲 Copper Link 或是说DAC cable的应用,因为在 224G-PAM4 这样的超高速传输环境下,二代布的损耗控制已接近极限,难以同时满足铜缆布线的需求。

常见材料:EMC EM892K2、TUC TU-943SR

石英布(Low-DK 三代布)即将到来

石英 (Quartz) 玻纤布被认为是 未来更高频应用的终极材料,因为它具备:

✅ 更低的DF,能进一步降低PCB损耗,适用于224G甚至更高速高频的应用

✅ 更稳定的热膨胀系数 (CTE),能减少高速应用中的热机械应力影响

虽然石英布的特性非常优异,损耗比二代布还能再优化10~15%,更能满足 1.6T switch 甚至3.2T的应用,但目前它仍面临几个严峻的挑战:

1️⃣ 供应量极其有限:目前全球石英布的生产能力非常低,无法快速满足大规模量产的需求。

2️⃣ CCL 量产与认证挑战:尽管各大 CCL 厂商已将石英布纳入开发 roadmap,但目前真正能在 2025 年通过 CCL UL及 PCB UL 认证的供应商仍然不多。

3️⃣ 经济规模问题:即便 2025 年能有少量量产,但真正的大规模应用从这些产品量产时程来看,可能还需要等到 2026Q3~2027Q2,当产业链成熟后,石英布才可能取代 Low-DK 二代布,成为下一代标准材料。

预计会出现的材料:EMC EM-896K3

674

674

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?