线路side by side布局时,最担心的就是边缘耦合干扰到线路特性,其中以远端耦合(FEXT)造成的影响最为可怕,因为从

串音干扰

(3):近端耦合与远端耦合一文里我们知道FEXT有着时间较短能量较强的特性,容易一次大量的干扰讯号,使的接收芯片眼图更差,更容易产生误判断。

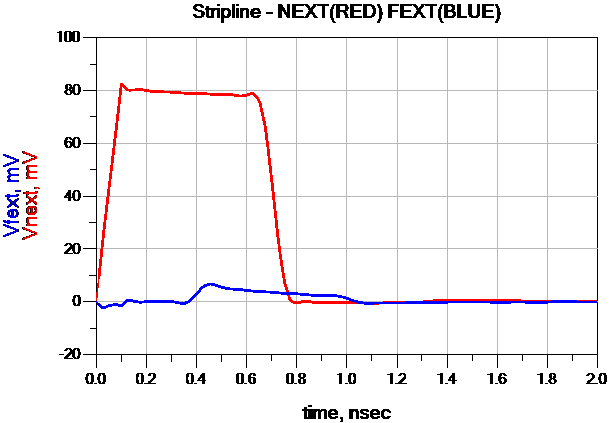

要最有效率地降低FEXT的方法就是将走线布局在内层,也就是带状线(Stripline)。

原因其实很简单,在

差动讯号(2):奇模与偶模文章中我们已经提到奇模与偶模的场型是不一样的,也因此造成线路在这两个模态的速度不一致, 不过那是在微带线的情况下。

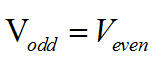

在带状线中,由于板子上下是对称性结构,而且材料一致,所以奇模与偶模不会有场型差异,这将使得奇模速度与偶模速度一致!

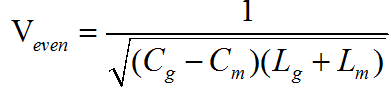

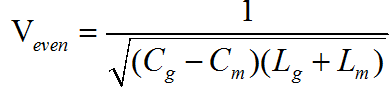

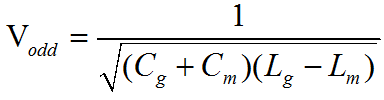

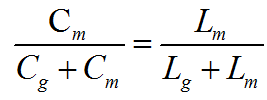

我們可以用數學公式來看待:

因为

所以可以得到结论是

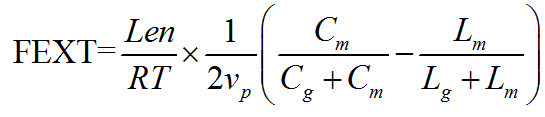

大家有没有觉得这式子很眼熟? 似曾相识的感觉,我们将文章切换到串音干扰(4) :如何降低耦合噪声CROSSTALK,FEXT的数学公式为

这样就一目了然了,带状线的FEXT在数学上的确为0,不过这当然是属于理想的带状线才会有的结果,现实上板子的厚度与材料的DK值不太可能做到上下层完全一样,因此不可能完全没有FEXT,但是已经是现有做法里最有效抑制FEXT的方法了! (除非你想把线距拉的很开)

580

580

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?