前言:上一讲完成了基本时钟和生成时钟的约束,确定了整个工程的时钟频率,本次内容要添加合理的 input 和 output delay, 把接口时序调整到一个最佳状态。

这里写目录标题

一、 I/O常用约束分类:

IO约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(InputDelay 、OutputDelay)、上下拉电阻、驱动电流强度等。

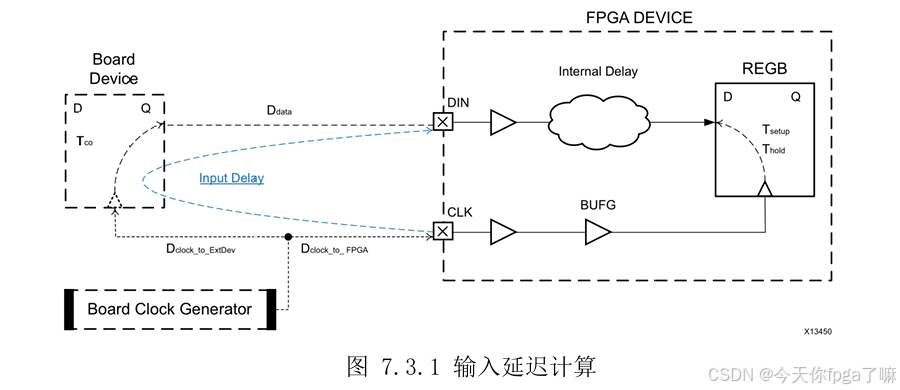

1.input delay

-set_input_delay :设置管脚输入延迟

set_input_delay -clock clk0 5 [get_ports din]

含义:是din 端口与 clk0 关联,输入延迟约束为 5ns。

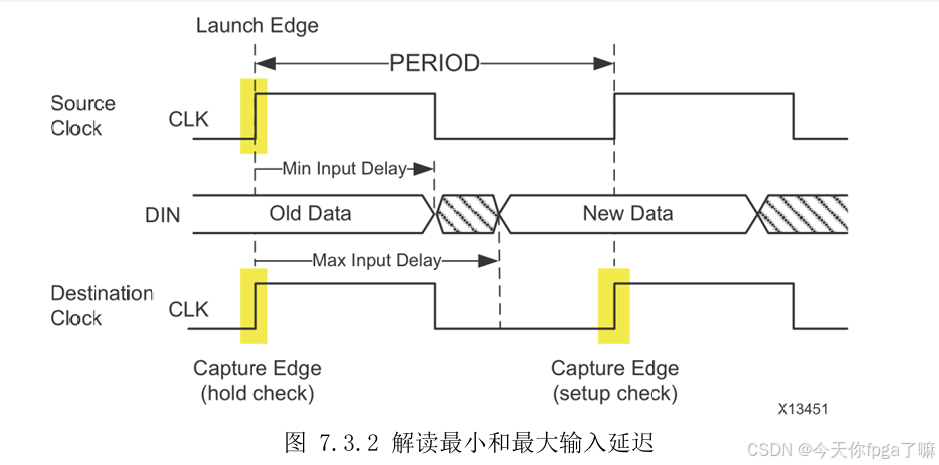

一般分为两类(MAX MIN):

set_input_delay -max -clock sysClk 5.4 [get_ports DIN]

含义:设定最大建立时间为5.4ns,即设计工具将确保数据在时钟边沿到来之前的 5.4 ns 期间保持稳定。

set_input_delay -min -clock sysClk 2.1 [get_ports DIN]

含义:设定最小保持时间为2.1ns,即设计工具将确保数据在时钟边沿到来之后的 2.1 ns 期间继续保持稳定。

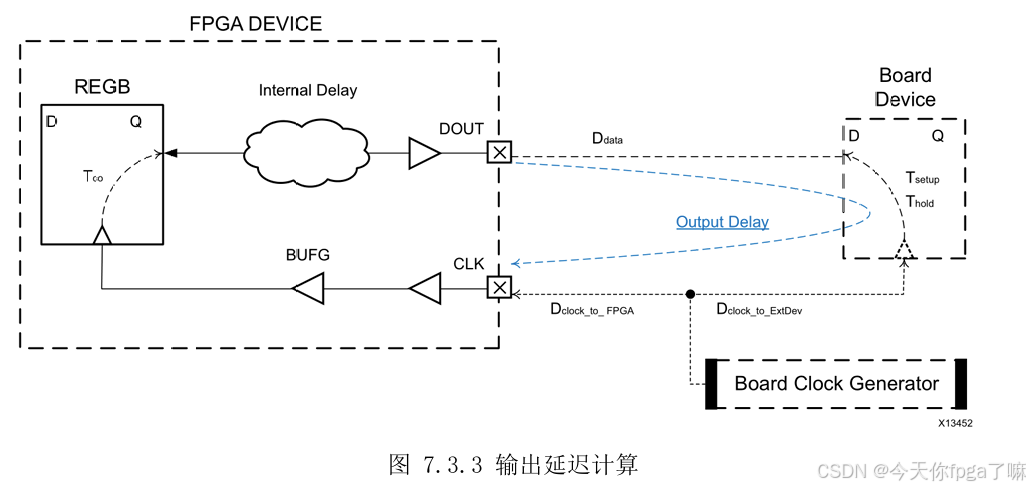

2.output delay

set_output_delay :设置管脚输出延迟

set_output_delay -min -0.5 -clock CLK [get_ports DOUT]

含义:表示设计内部直到DOUT 管脚的延迟必须至少超过0.5ns,才能满足保持时间

的需要。

一般分为两类(MAX MIN):

set_output_delay -max -clock sysClk 2.4 [get_ports

DOUT] 含义:设定最大建立时间为2.4ns,即设计工具将确保输出信号 DOUT 从时钟边沿起,最多延迟 2.4 ns

才

本文介绍了在项目中如何通过调整inputdelay(包括PLL相位调整和数据延时)以及outputdelay来优化接口时序,重点关注了DDR双沿采样方式下的约束设置和时序分析。作者还提到了利用IDELAYE2进行数据延时以及BSKew和ASKew在outputdelay约束中的区别。

本文介绍了在项目中如何通过调整inputdelay(包括PLL相位调整和数据延时)以及outputdelay来优化接口时序,重点关注了DDR双沿采样方式下的约束设置和时序分析。作者还提到了利用IDELAYE2进行数据延时以及BSKew和ASKew在outputdelay约束中的区别。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

646

646

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?