前言:上篇文章实现了MATLAB模拟发送UDP以太网协议数据包到fpga,能实现双沿数据→单沿数据转换,并将转换后的数据进行包过滤和crc校验,本篇内容要实现真正的从pc机下发视频数据,经过千兆以太网传输存储到fpga 的ddr3中,然后通过hdmi读出到显示屏上。

文章目录

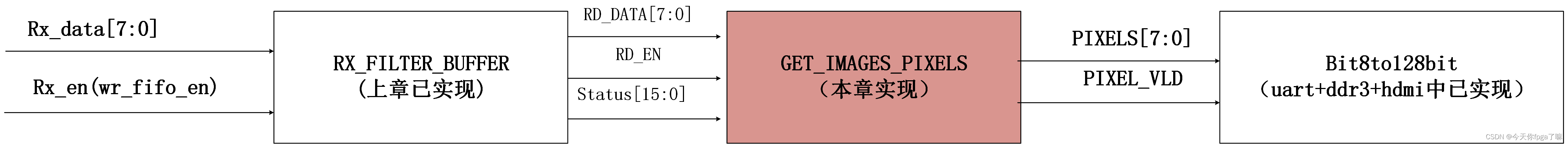

一、模块设计:

过程分析:在真实的视频数据传输过程中,需要考虑到ddr3存储的是有效图像数据(不包含udp的包头和crc等数据),因此需要将过滤出来的有效包进行有效像素提取,然后经过bit8 to 128模块,存储到ddr3中。

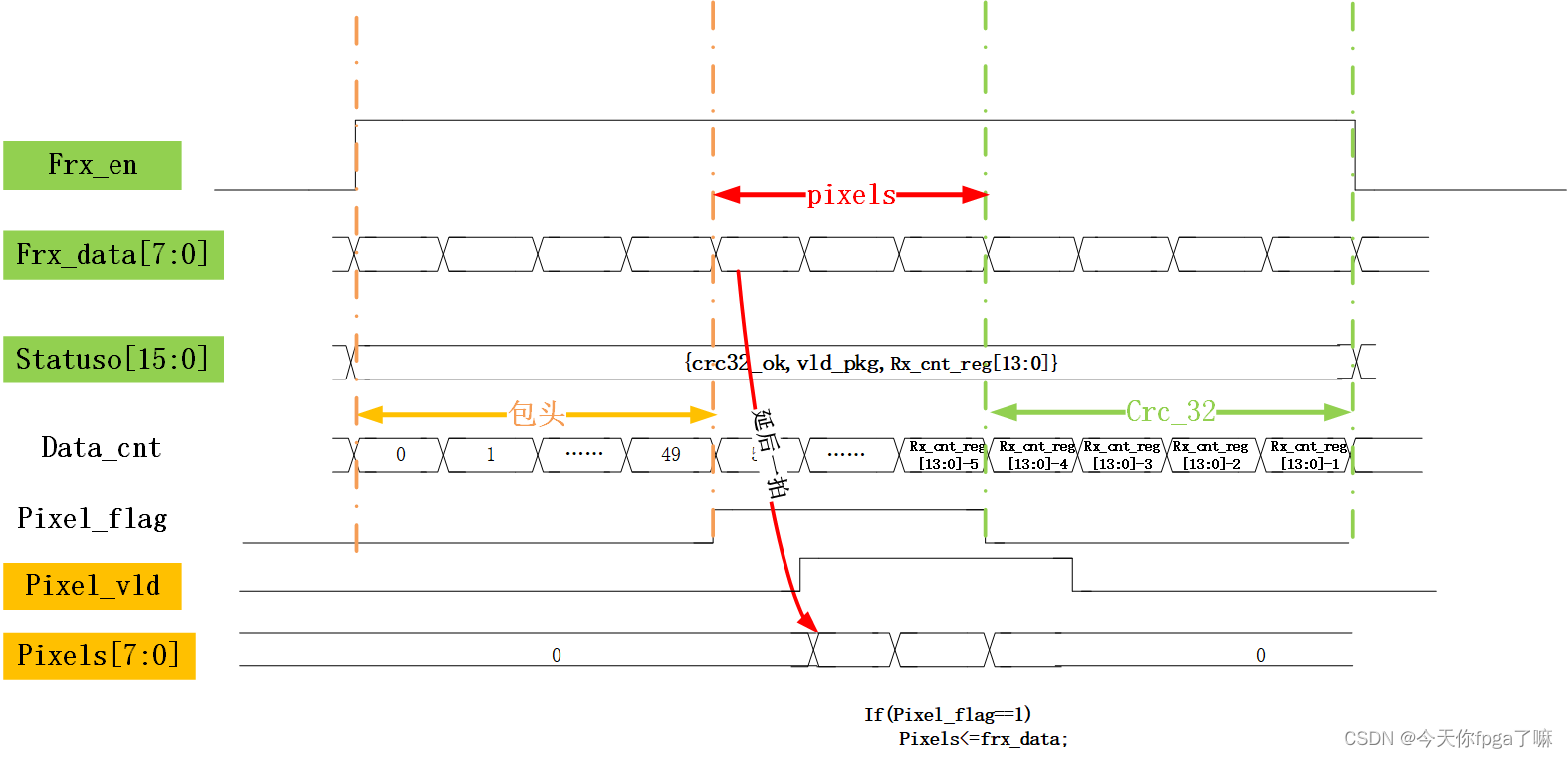

1.1波形设计:

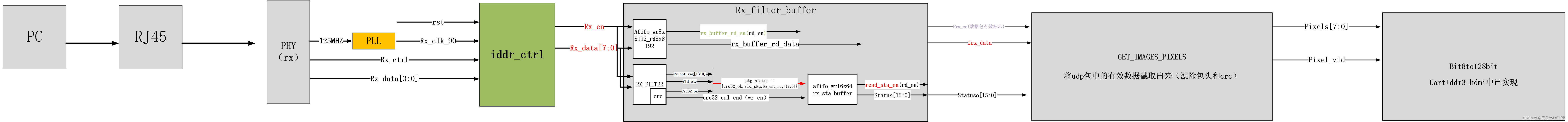

1.2 完整的千兆数据流输入示意图:

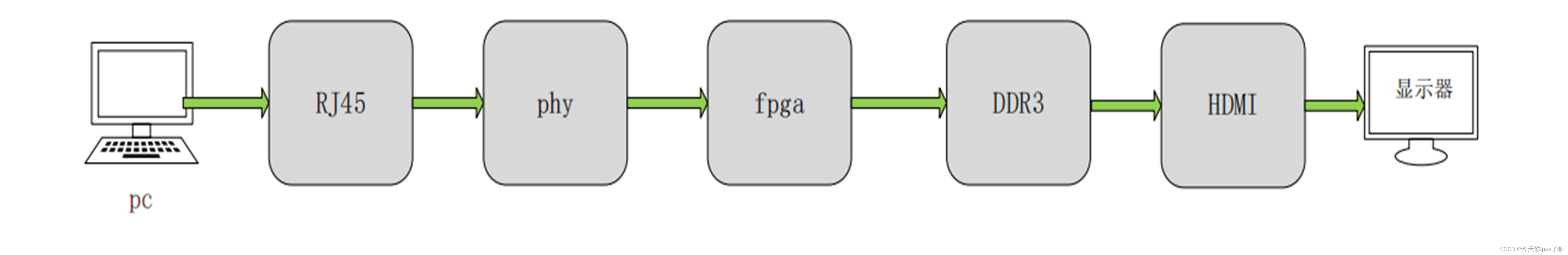

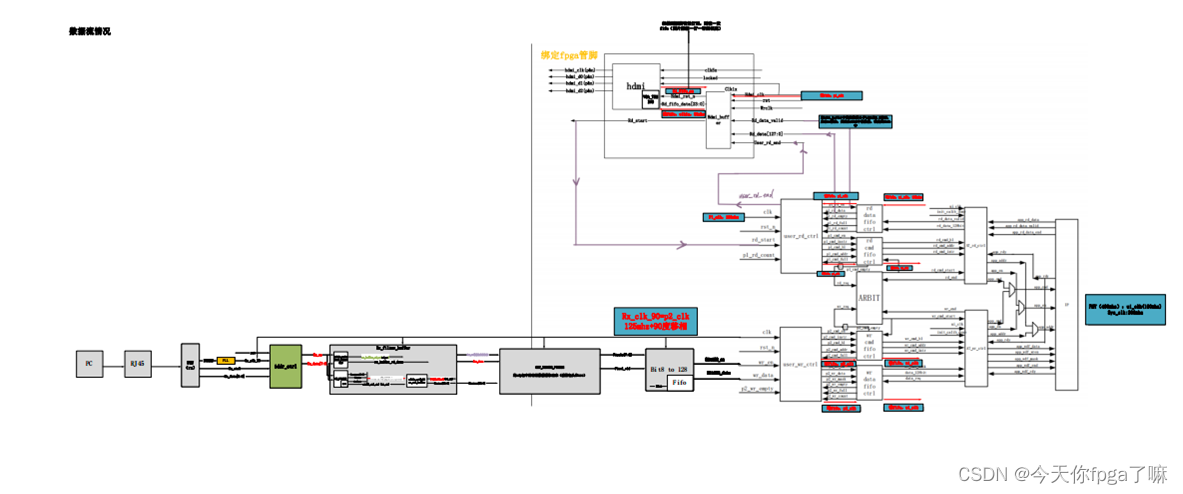

1.3完整的从pc机到hdmi模块设计总览:

pc机→hdmi通信链条打通:

二、数据源的处理与下发

2.1MATLAB实现原视频RGB24bit→RGB16bit转换操作

uart+ddr3+hdmi项目中,我们知道输入的图像应该是RGB16bit的,而原视频是RGB24bit,因此需要将原视频进行RGB24bit→RGB16bit转换操作。

clear all;

filename='test.mp4';

obj=VideoReader(filename);

numFrames = obj.NumberOfFrames;

bar=waitbar(0,'视频转换中,请稍后! ');

for f=1:numFrames

RGB = read(obj,f);

RGB

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6681

6681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?