spyglass检查是IC设计中的一个重要环节,其中的check rule是spyglass检查的重要依据。Spyglass check分为RDC (Reset Domain Crossing) check和CDC (Clock Domain Crossing) check,下面就详细介绍一下CDC (Clock Domain Crossing) check的一些规则。

1.spyglass的应用场景

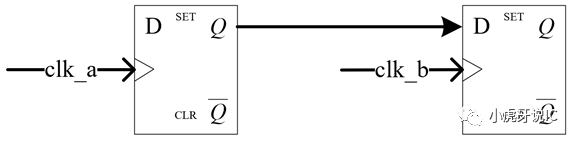

跨时钟域设计(异步界面设计)是IC设计中重要且容易出错的部分,普通的simulation很难发现跨时钟域设计的问题。为了能在设计的早期就发现跨时钟域设计中存在的问题,Spyglass应运而生。如下图所示,当clk_a=clk_b时,属于同步设计,需要检查setup time和hold time是否满足设计要求;当clk_a和clk_b是非同源时钟(异步时钟)时,属于异步界面设计,这时就需要用Spyglass工具做一些检查。

2.组合逻辑中的信号应属于同一个clock domain

为了保证IC能够安全稳定的工作,通常情况下组合逻辑电路中的各个信号应属于同一个clock domain。若有不属于同一个clock domain的信号,需要将该信号做同步后再参与组合逻辑运算。

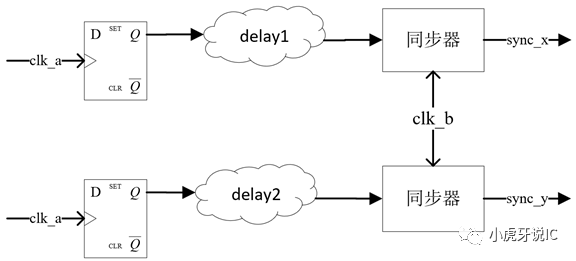

在data bus同步电路中,可以使用下图的同步结构。

3.避免出现re-convergence

如下图所示,当sync_x和sync_y同时使用时({sync_x, sync_y})就会出现re-convergence的情况。这时,需要在clk_a domain做处理后,同时同步到clk_b domain。

4.选择合理的同步级数

当clock频率较大时,可以考虑使用更多的同步级数。同步级数的问题在另一篇文章中有介绍,感兴趣的可以翻阅。

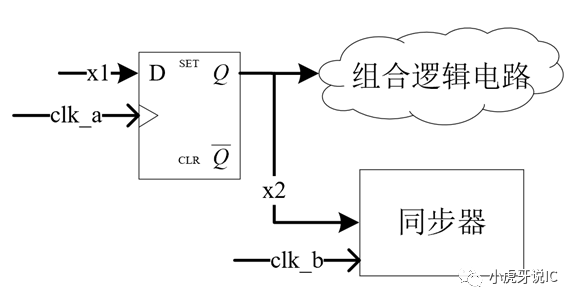

5.待同步信号不应参与其他组合逻辑运算

待同步的CDC信号(即同步器的输入,x2)不应参与到其他组合逻辑电路的运算中,否则fanout将很难保证。如下图所示,spyglass对于这类电路是会报错的,解决方法是专门为同步电路增加一颗DFF。

7445

7445

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?