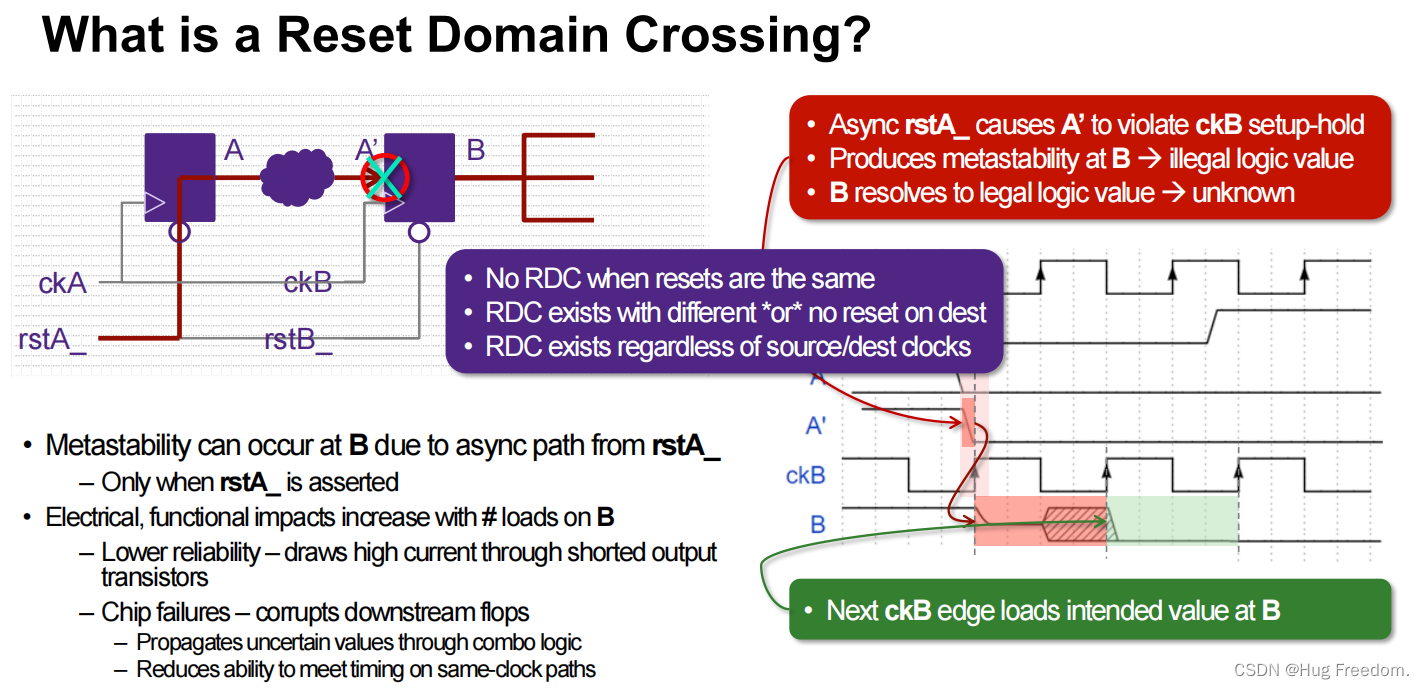

所有复位信号都是从异步复位同步释放电路处理过的,复位释放导致的亚稳态不存在, 主要是reset assertion时刻带来的亚稳态。每个模块的复位信号不一样,信号在跨异步复位域传输就会出现亚稳态的问题。

具体而言,对于有多个异步复位域的设计,如果某个异步复位在复位时,其复位信号正好落在接收域的建立和保持时间窗口内,就会造成亚稳态。需要不同异步复位域之间进行有效隔离或者同步,确保设计可以可靠复位。

1.当复位信号相同时,不存在RDC问题

2. 当dest dff没有复位信号或者与src dff的复位信号不同时,会产生RDC问题

3. 因为是异步复位,所以RDC问题与src/dst clk无关

异步复位的这个异步是RDC问题,同步释放(是否做了同步)是CDC问题。CDC PATH和RDC PATH可能重叠。

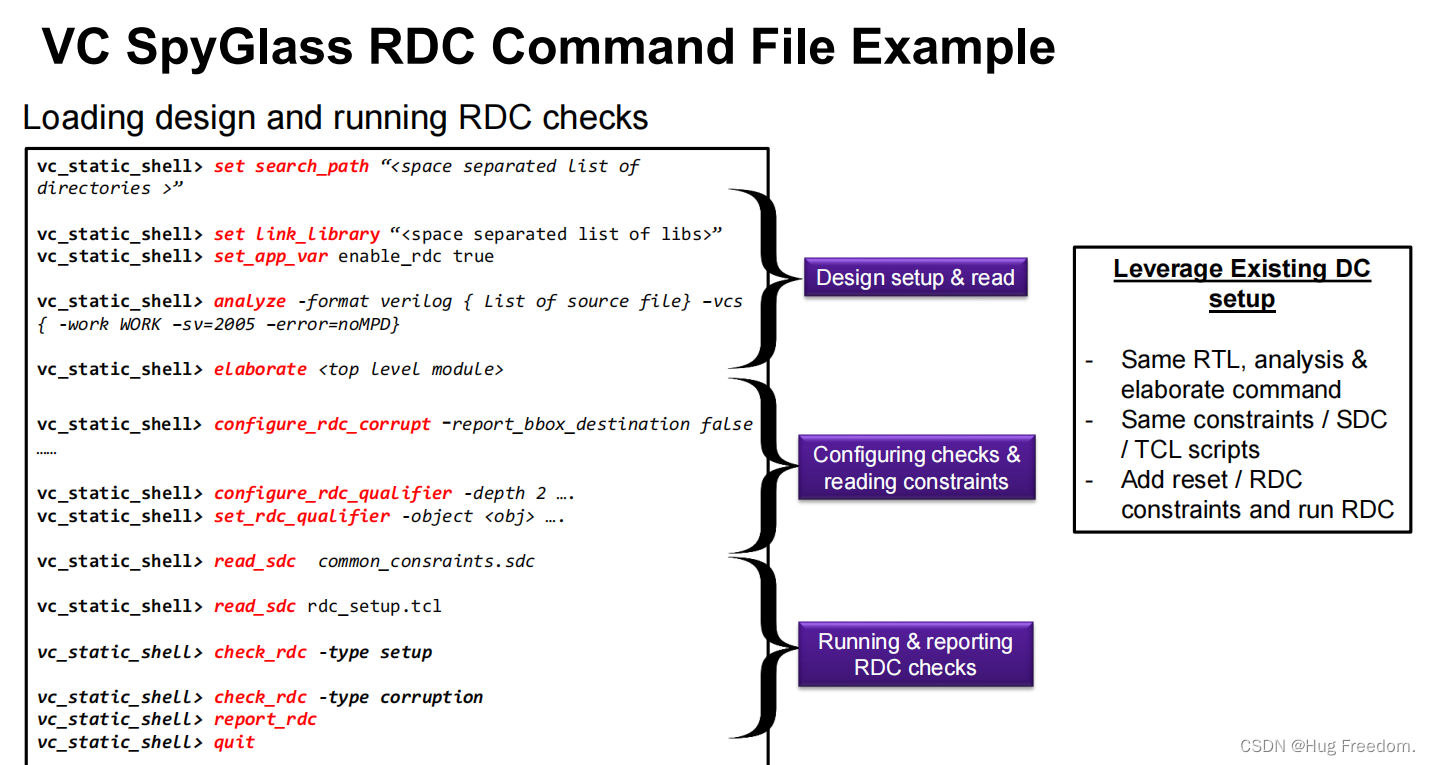

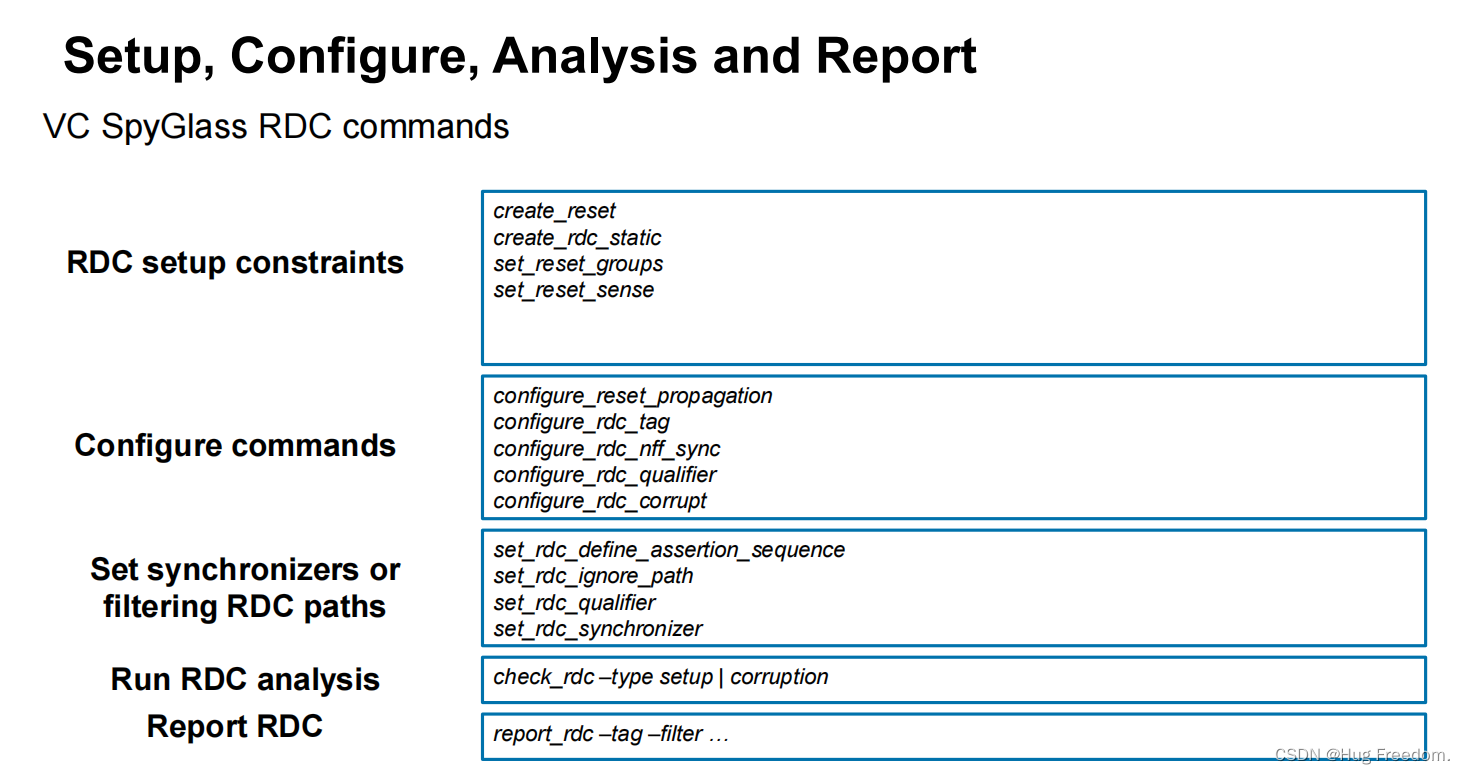

VC spg可以直接读取SDC,不需要转成sgdc

写进tcl里面。

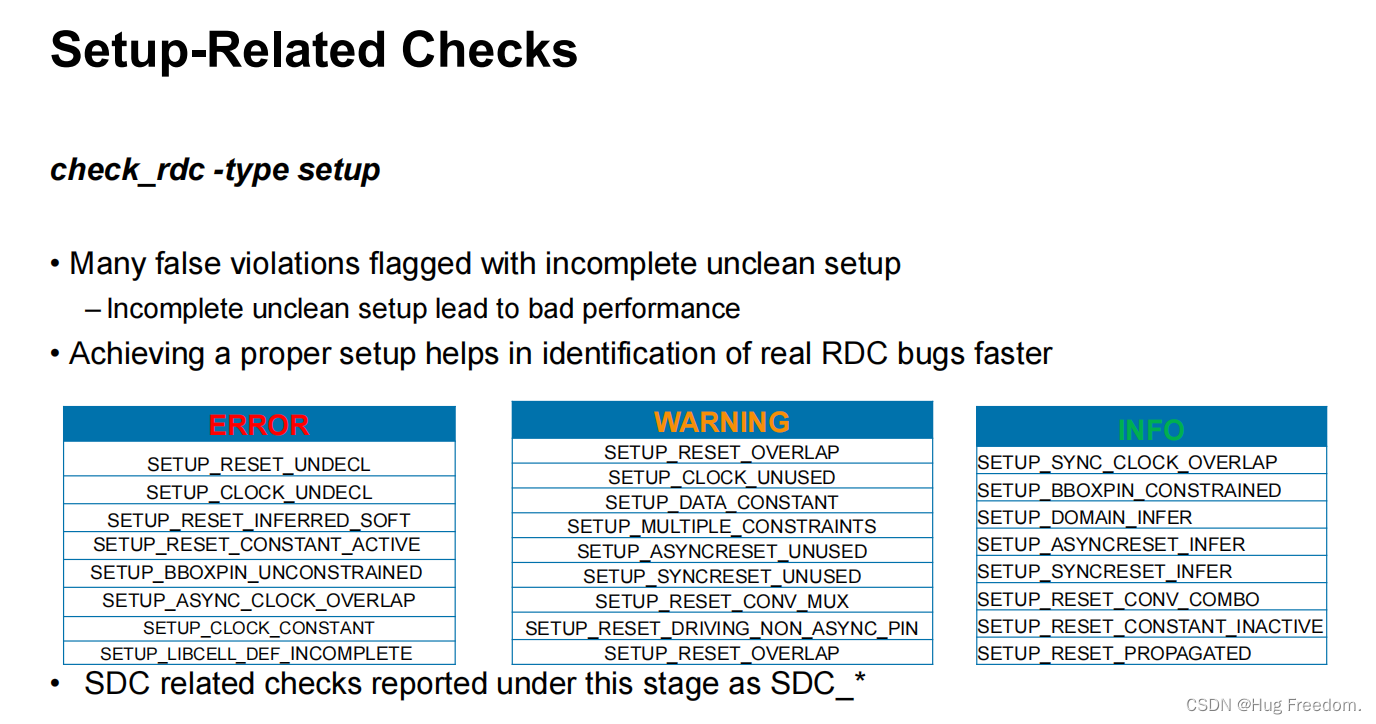

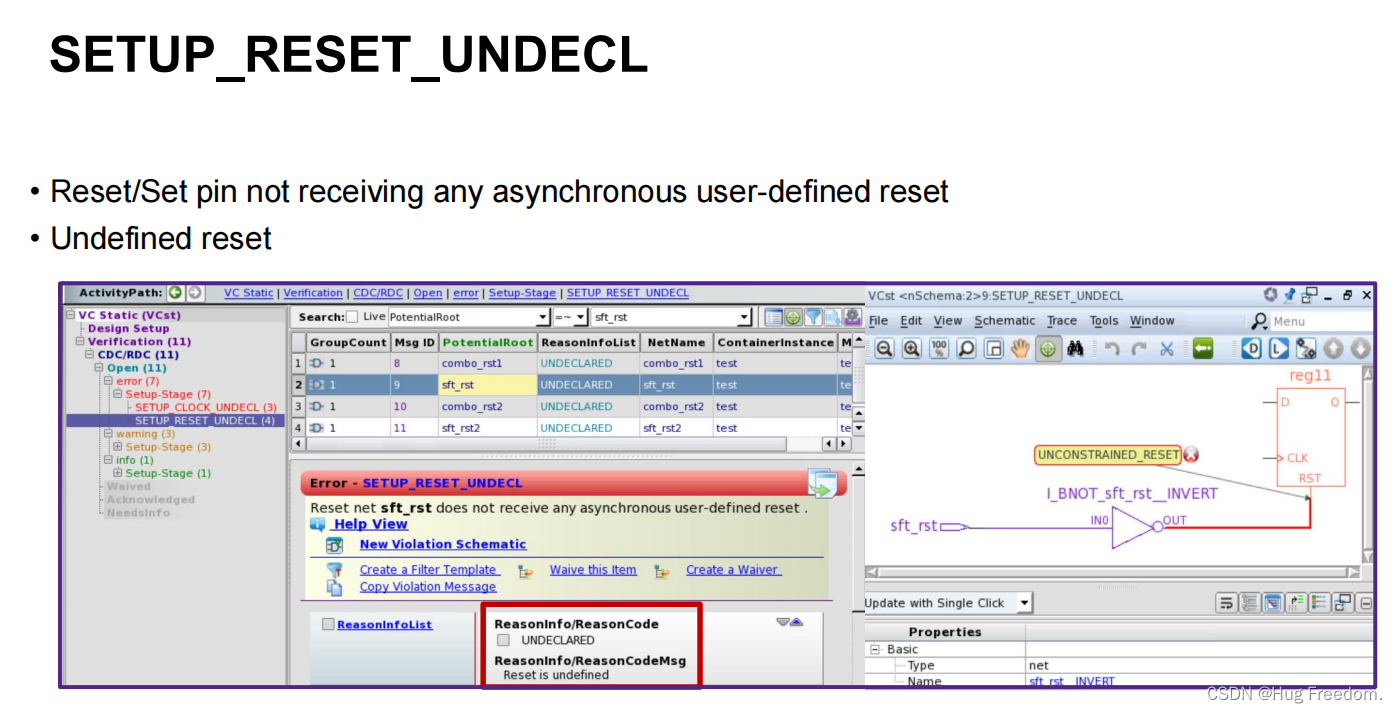

setup阶段的error尽可能清干净,典型的reset问题

1.reset未定义(creat_reset)

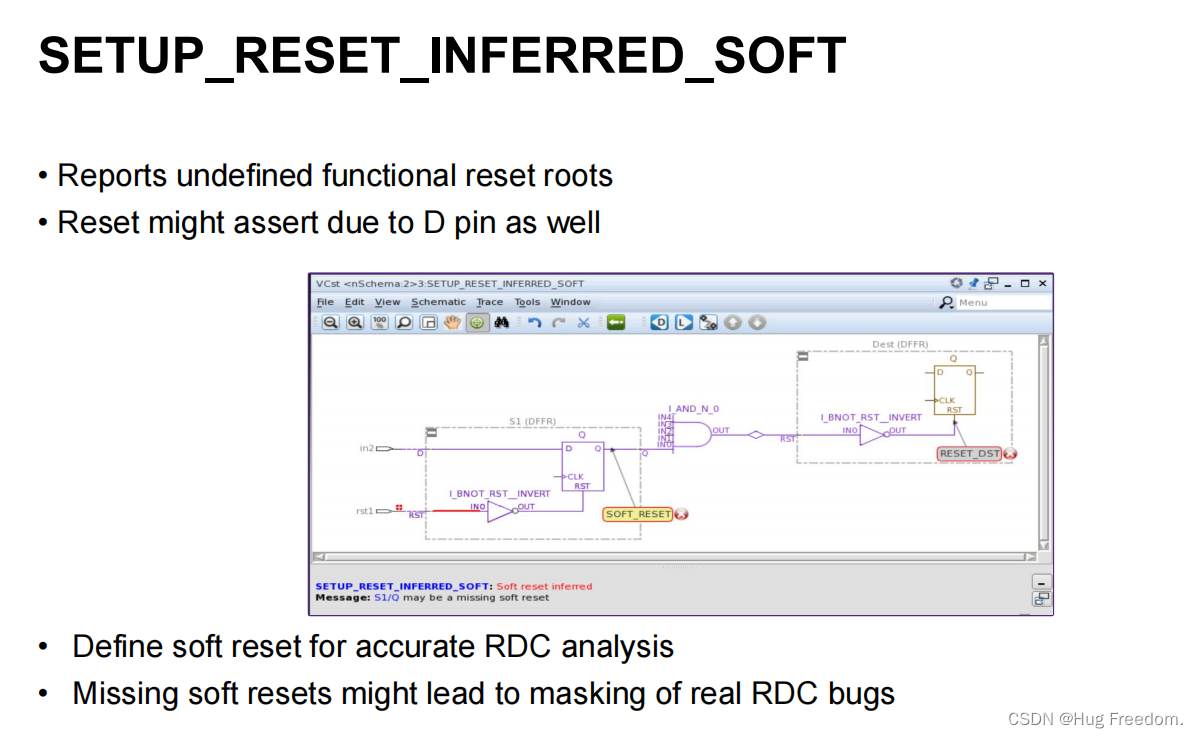

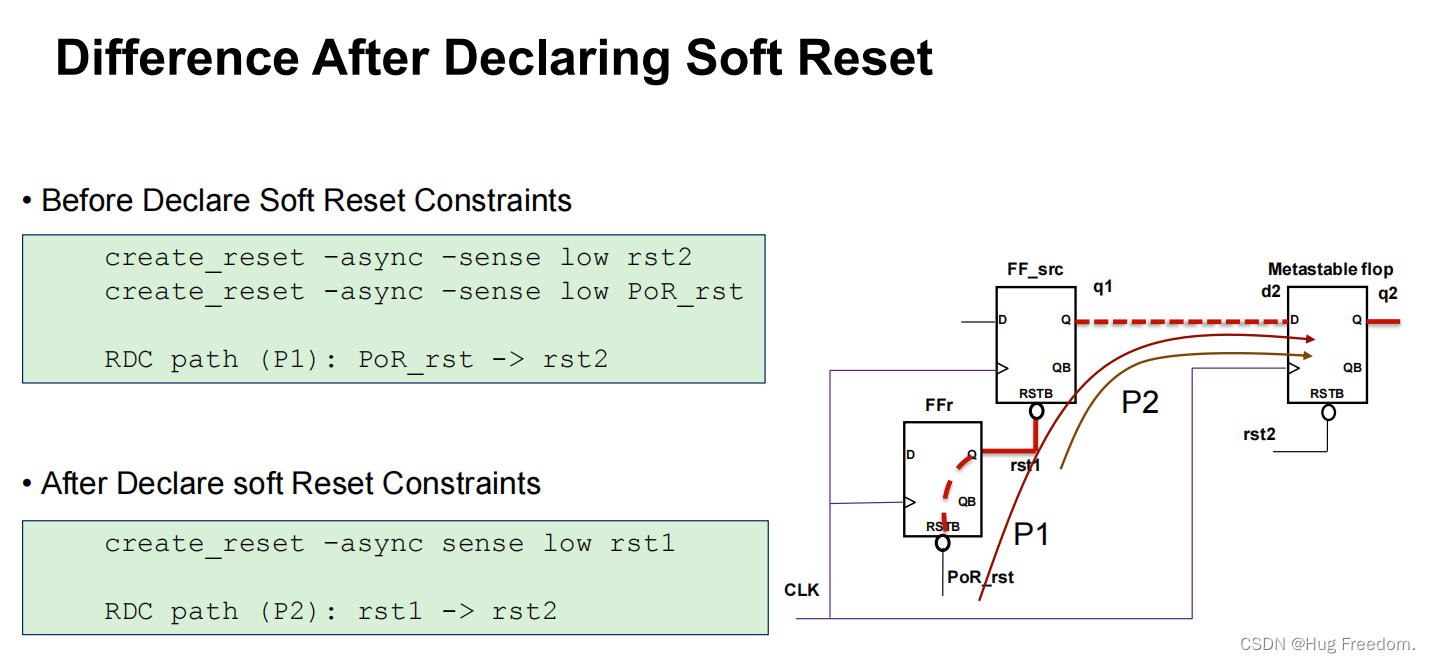

2. 没有声明的soft reset(由reset控制,由dff q输出,经过组合逻辑,输入给其他dff作为reset),建议soft reset 显示定义出来

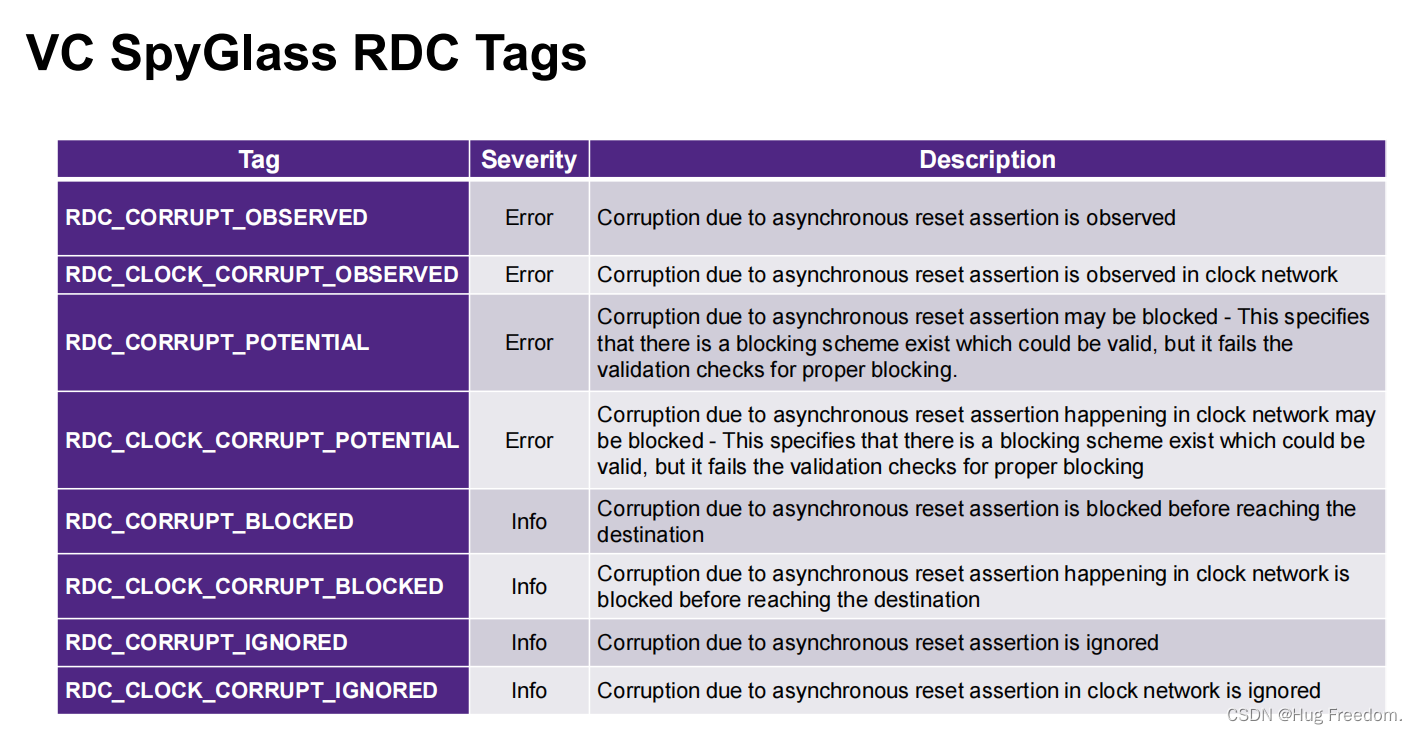

RDC TAGS

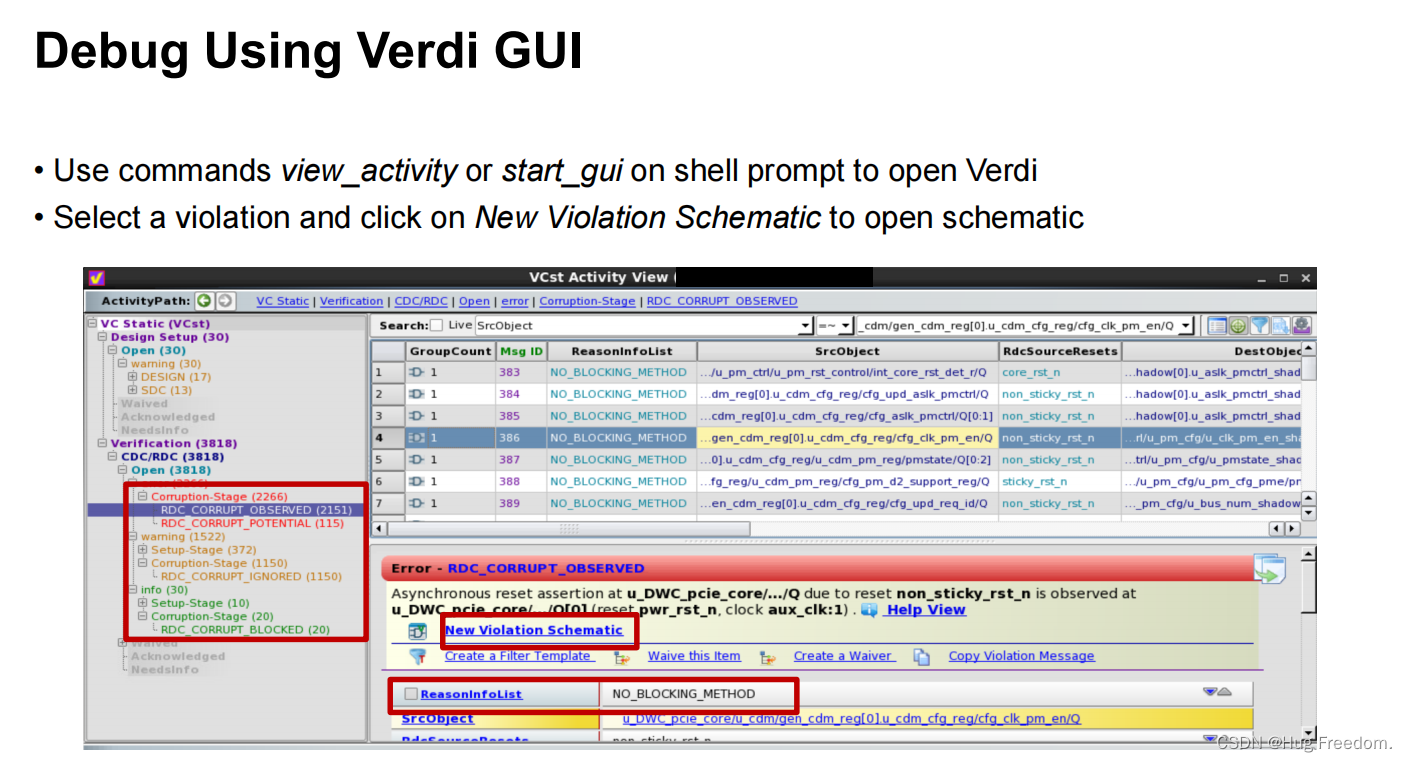

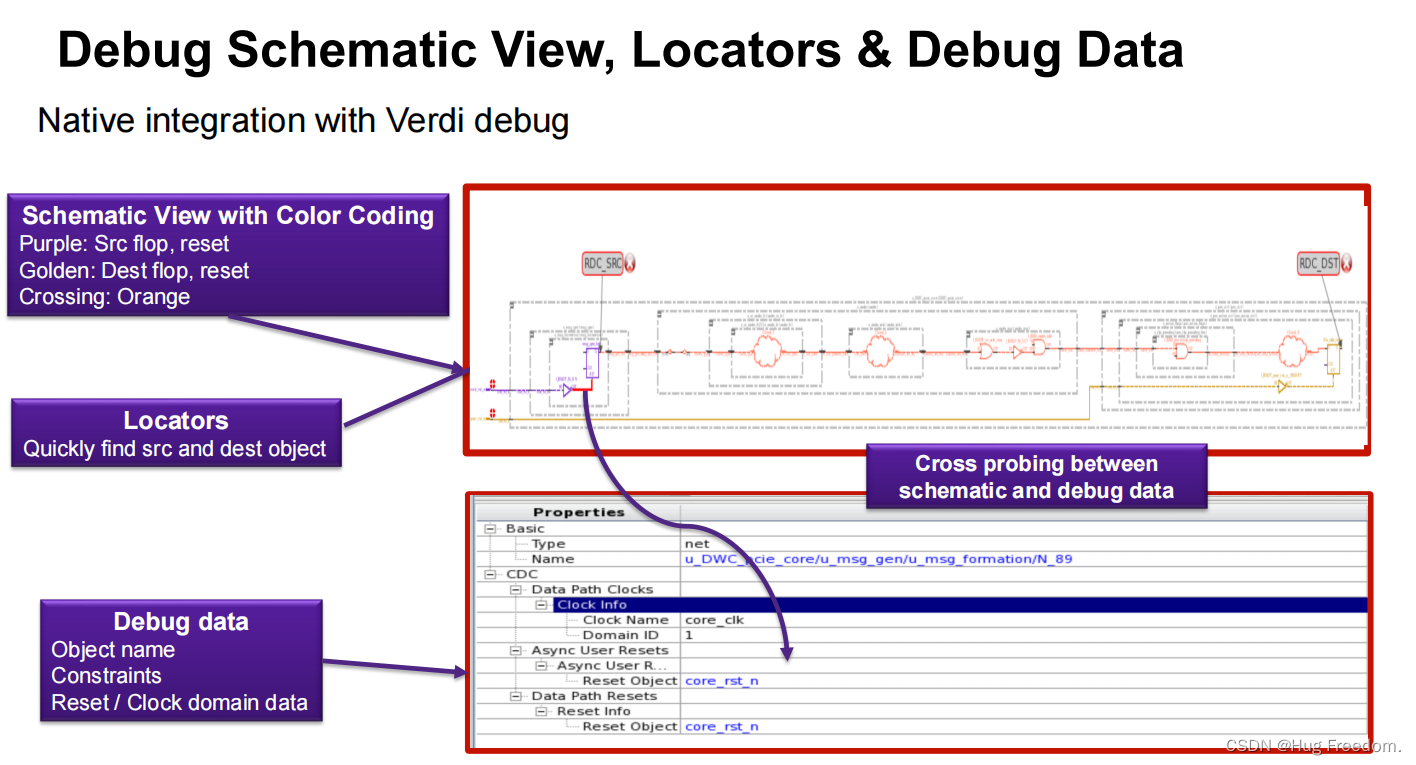

VC SPG GUI界面:

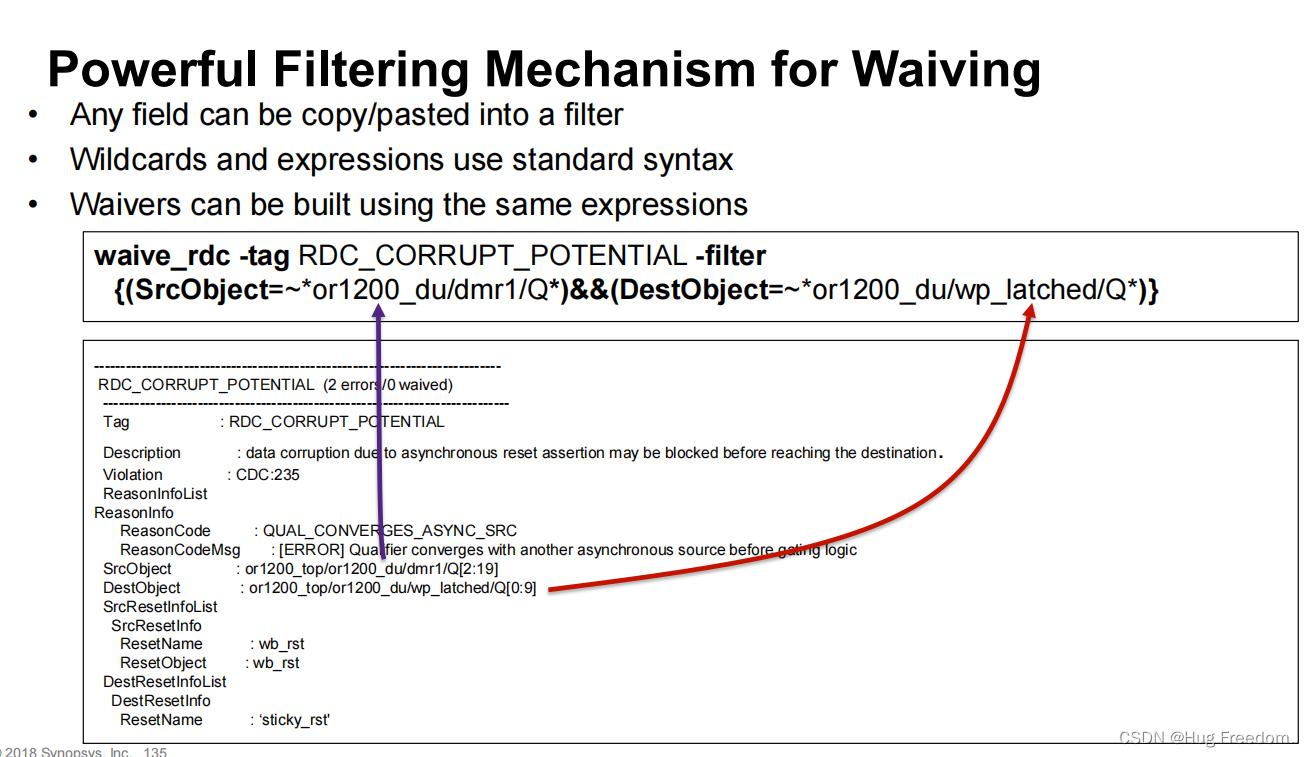

RDC的waiver语法:tcl格式的waiver file

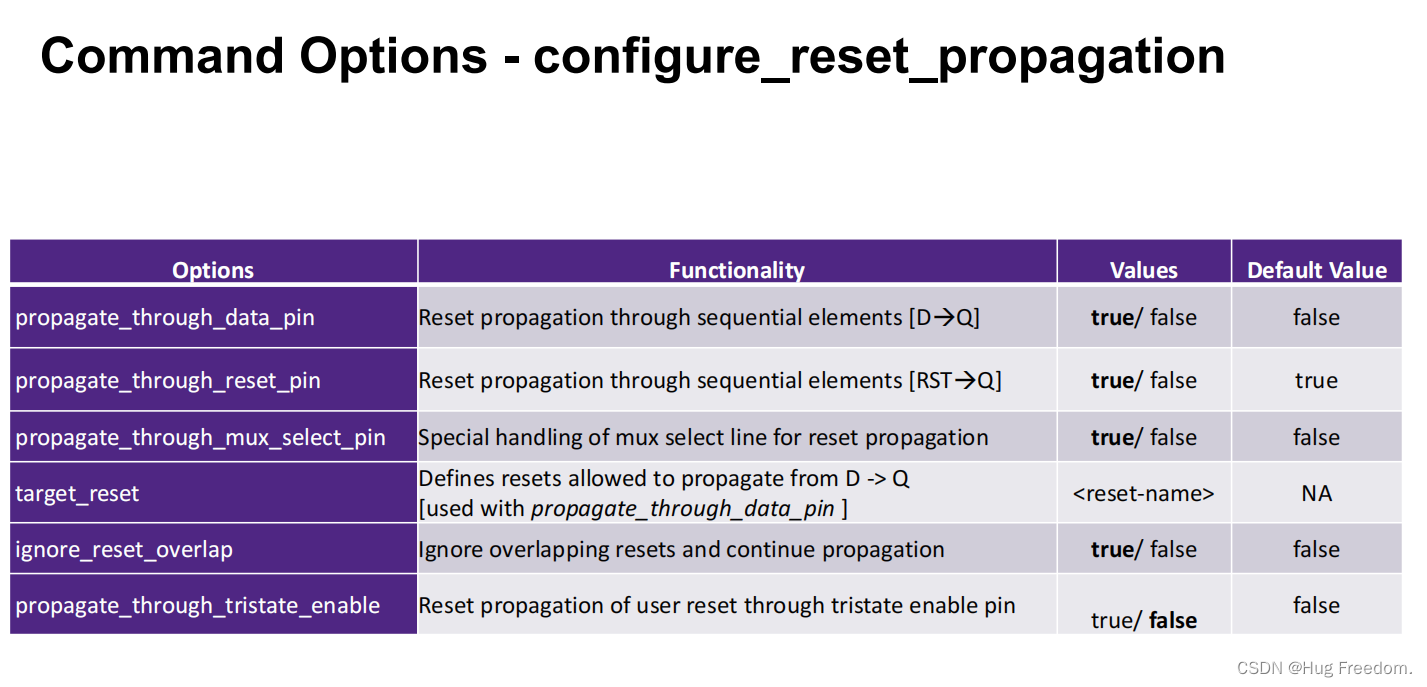

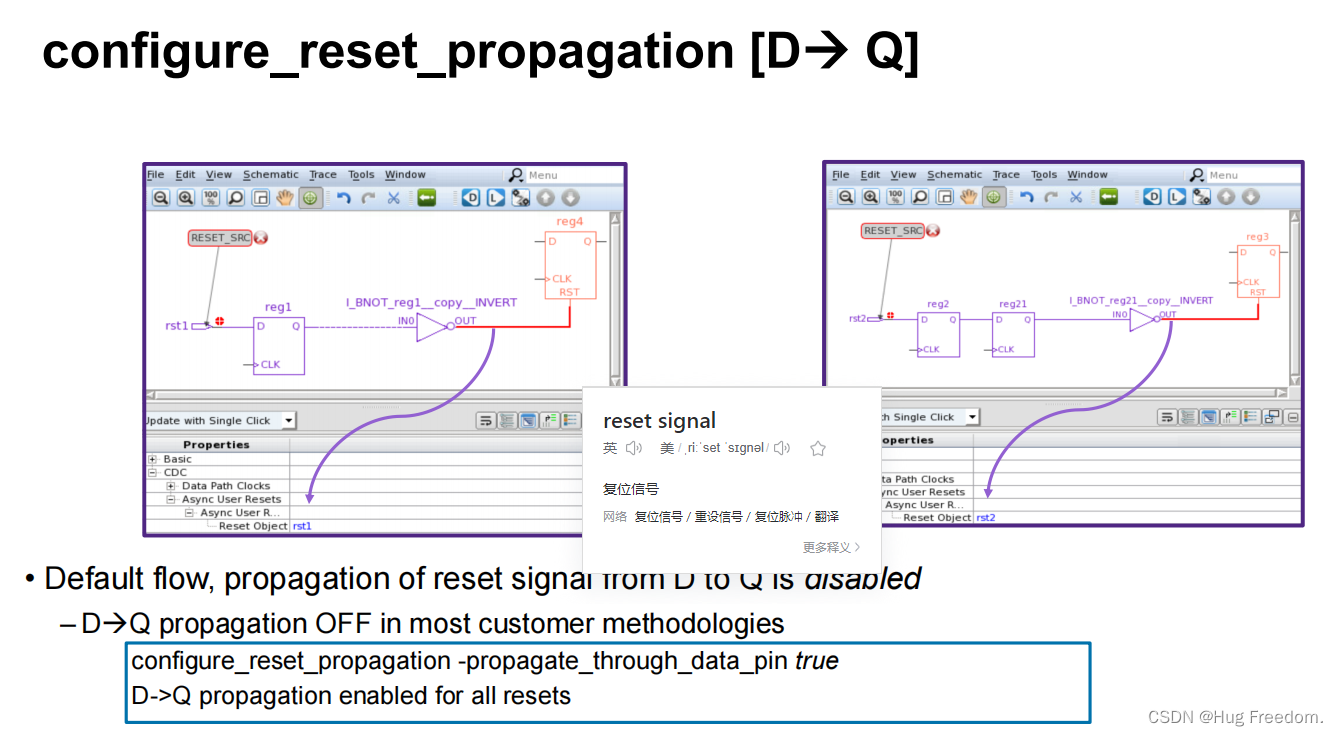

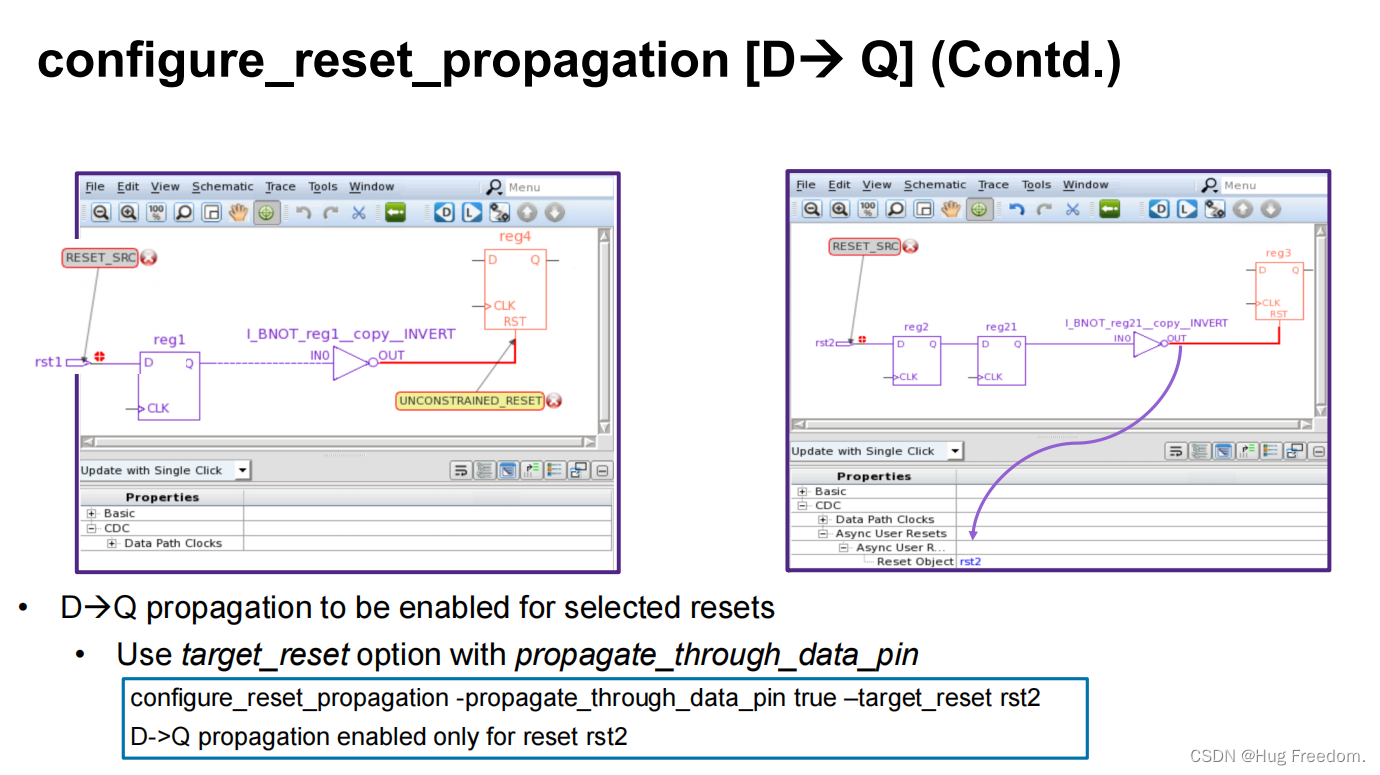

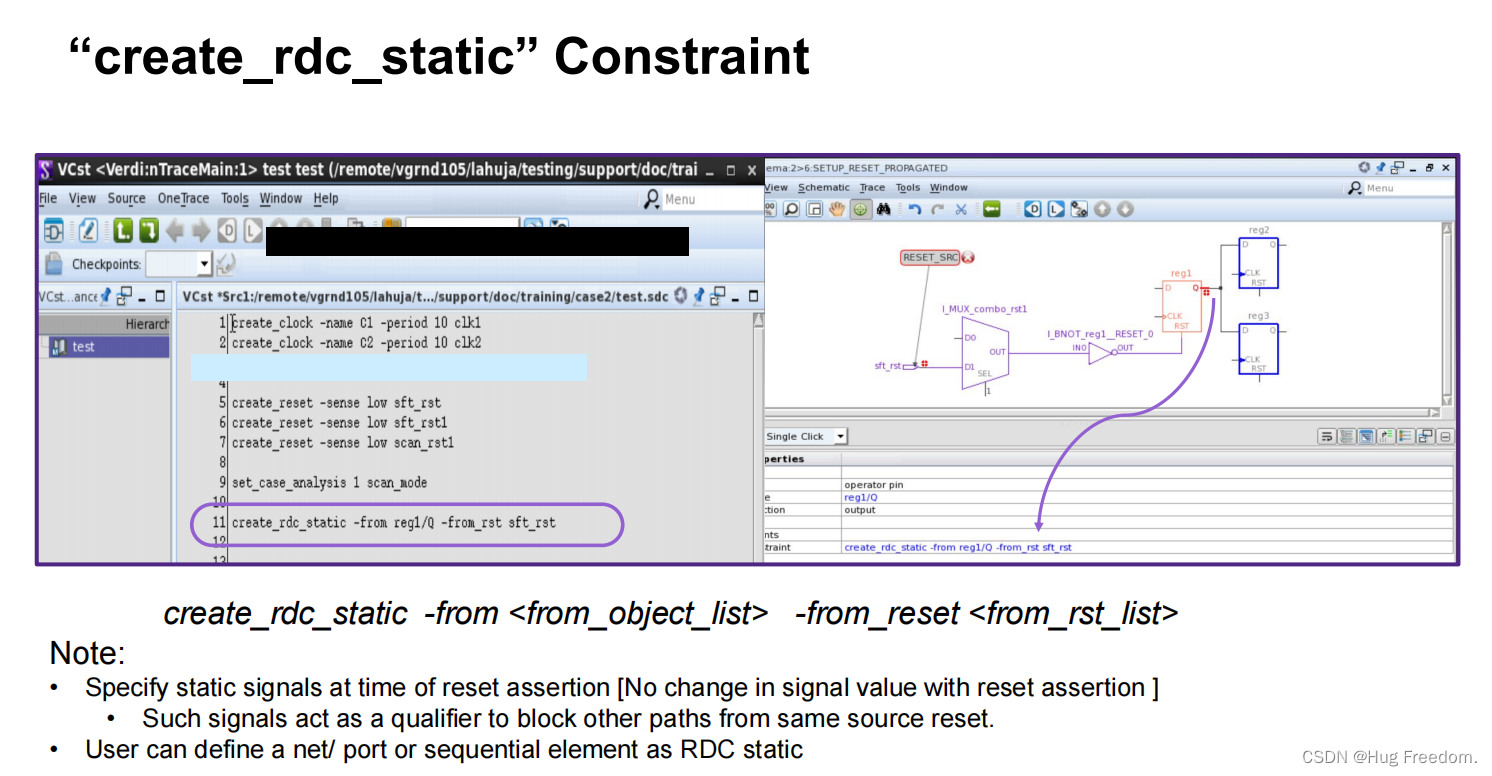

默认情况下,D-Q的reset传递是disable的,要设置才可以接收到原来的rst的,不设的话是没有reset传递的。

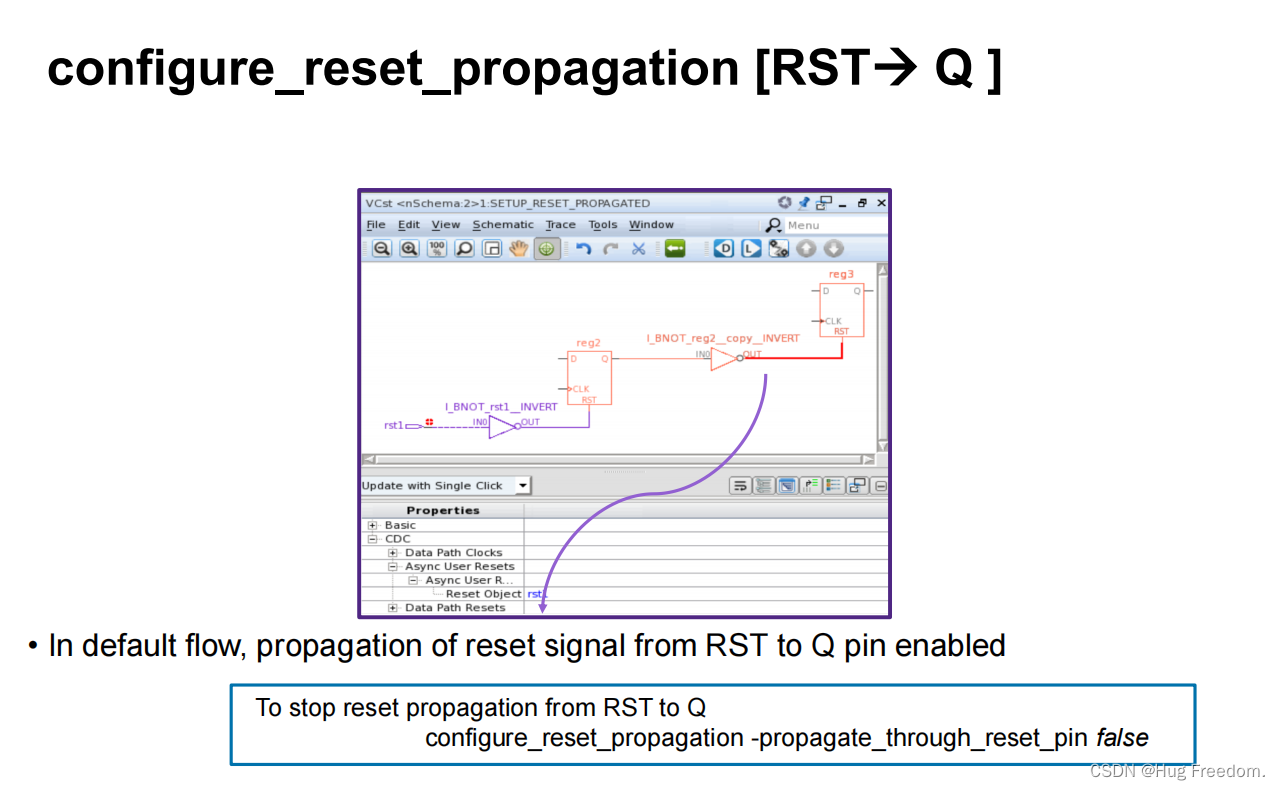

rst-q

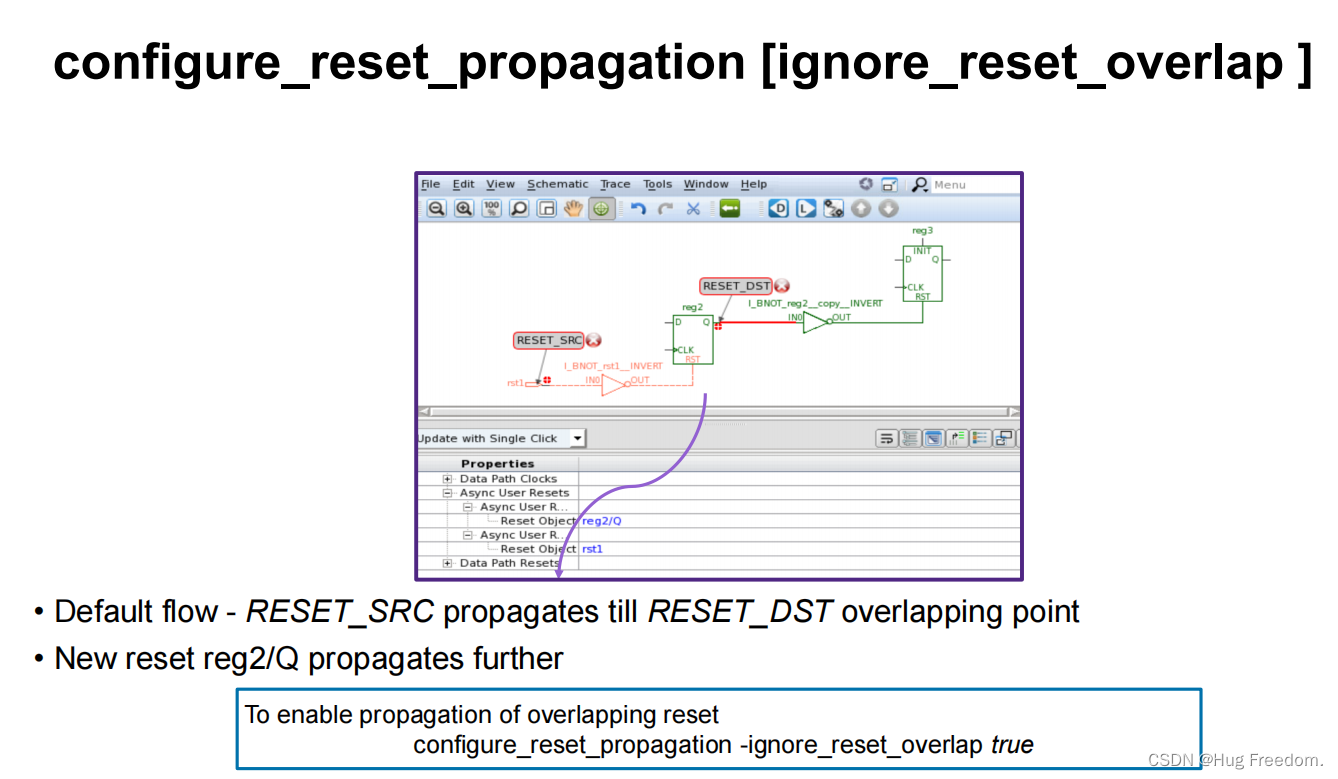

reset overlap(多个reset在一条path上同时传递)

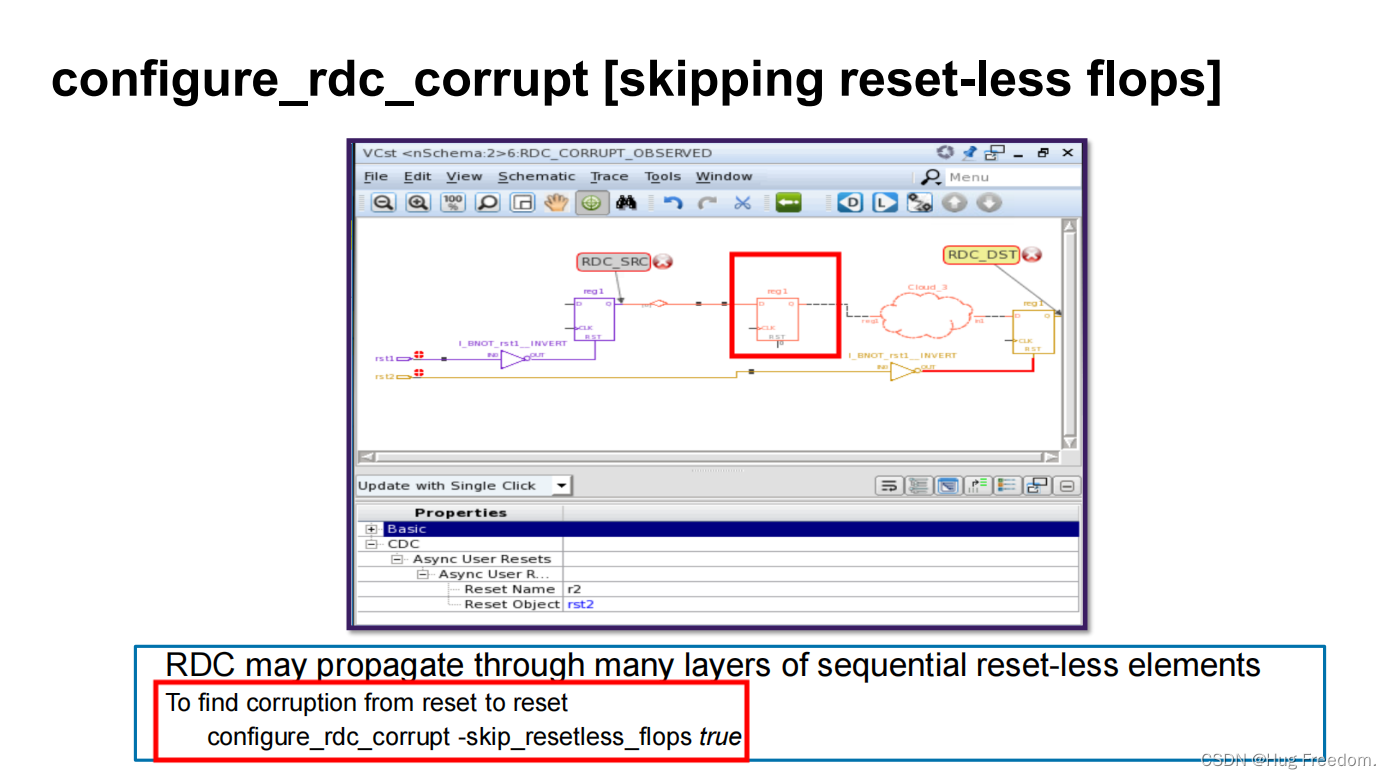

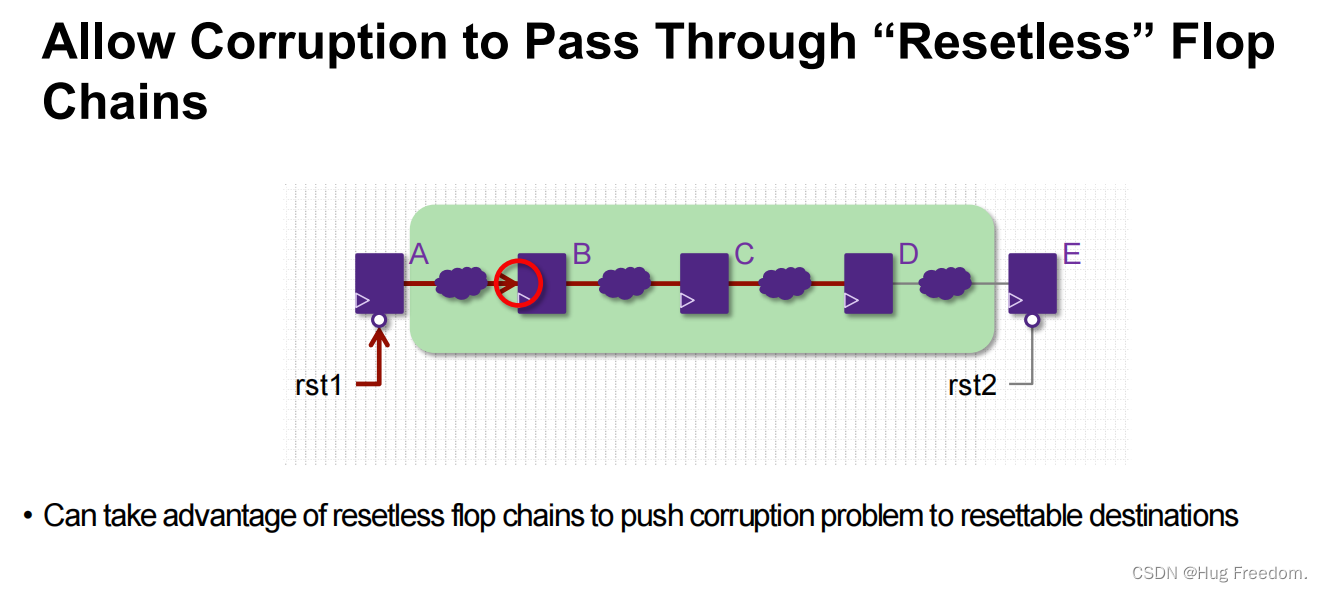

减少violation数量,跳过中间没有rst端的DFF,直接指向dstdff

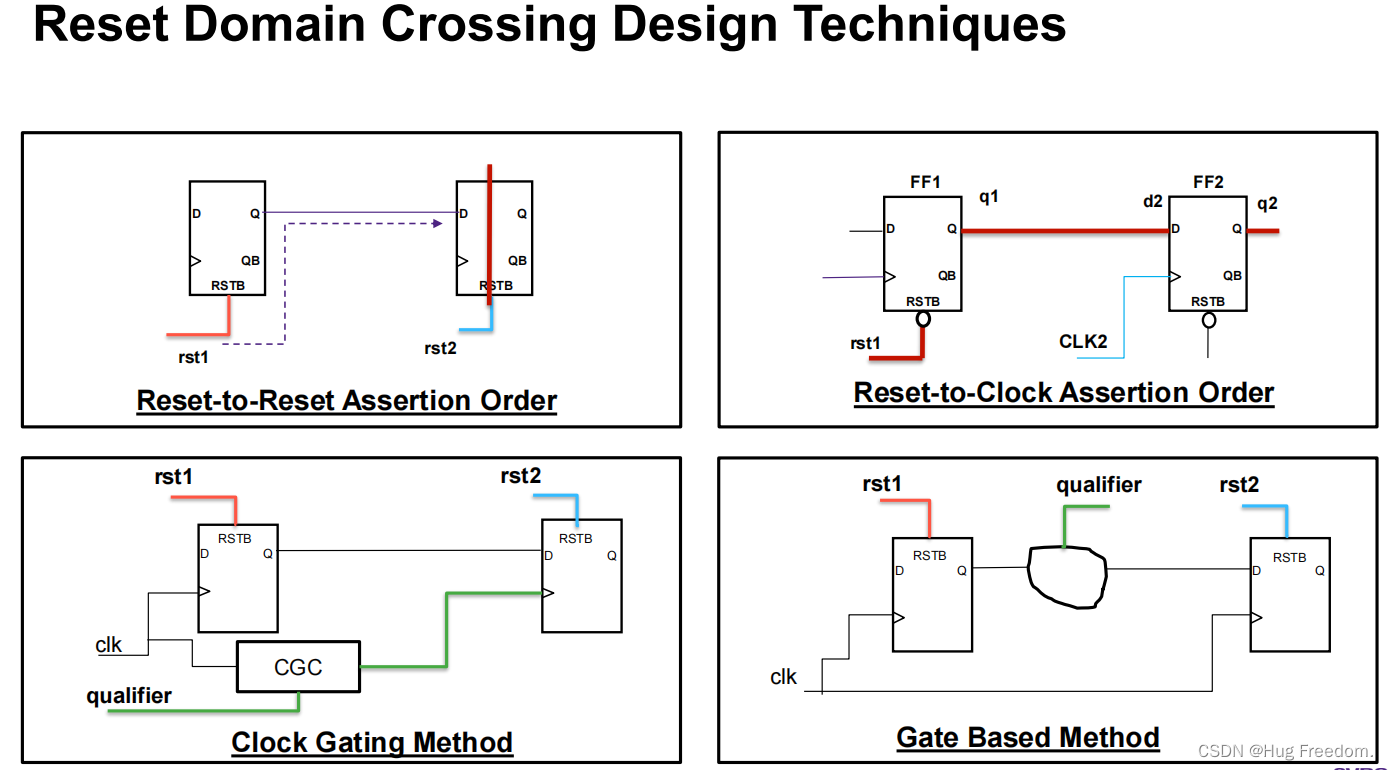

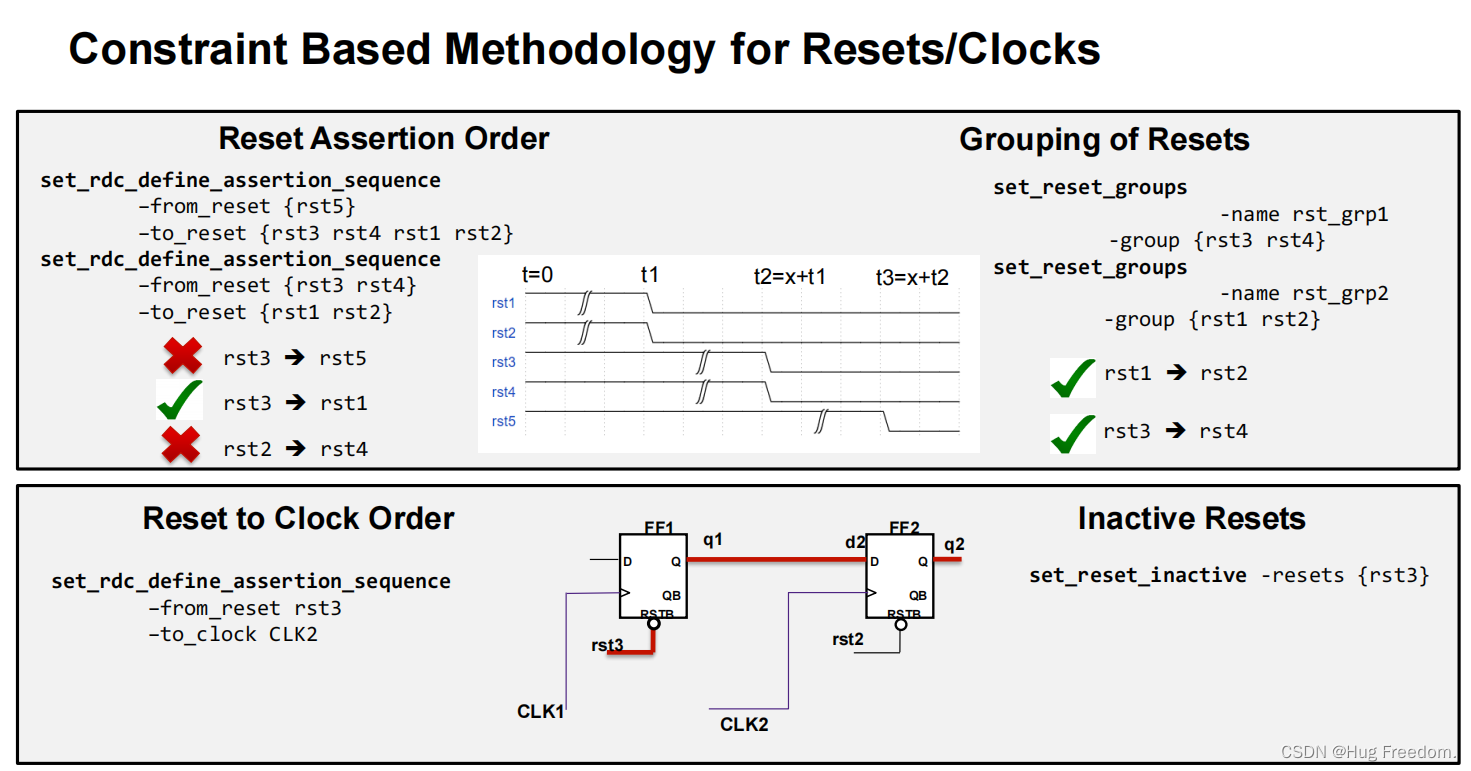

第一种情况:rst2一定先于rst1复位。

第二种情况:rst和clk之间的顺序,rst1一有效,clk2一定得关闭。

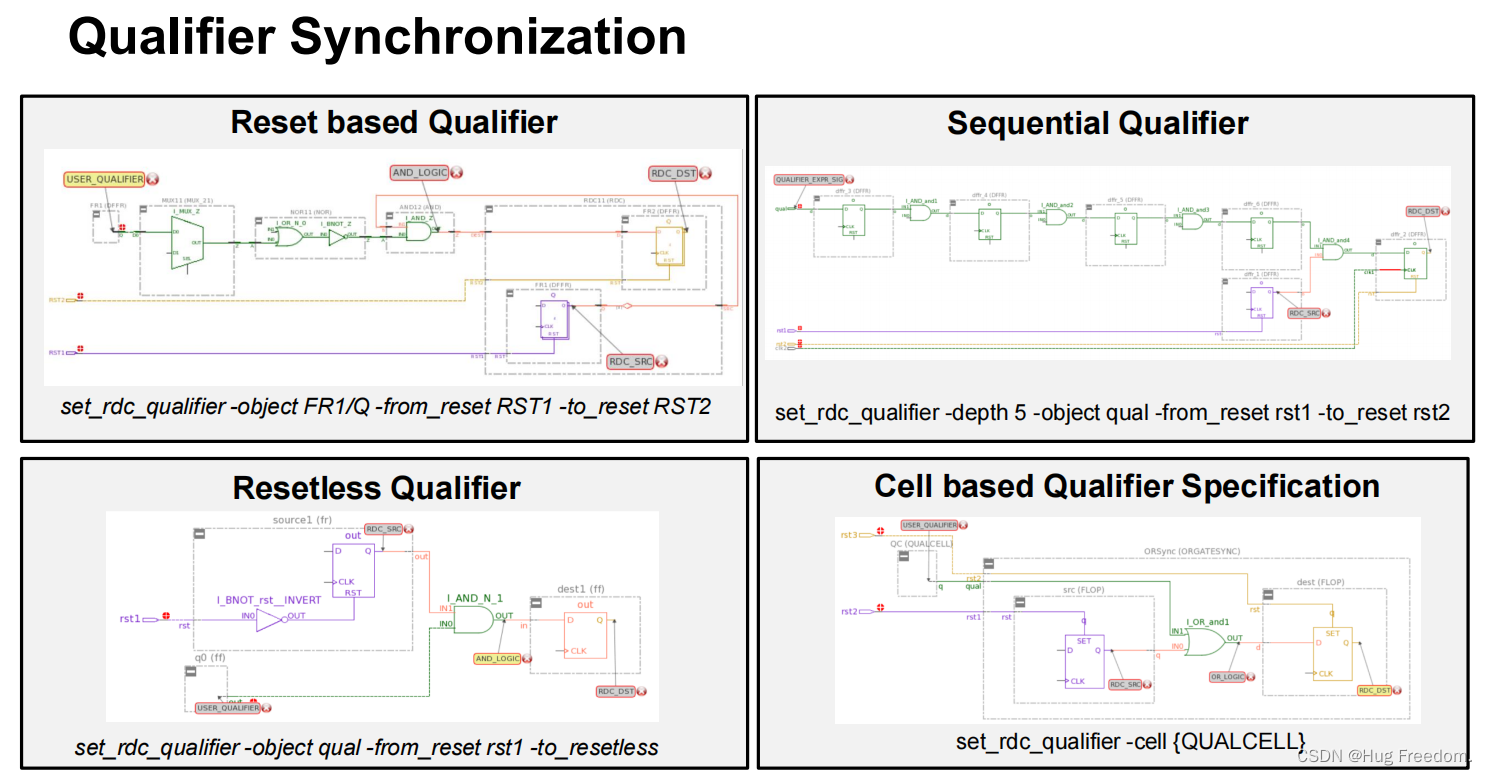

第三种情况:用qualifier的信号来控制一些结构,比如clock gating cell保证rst1有效时,已经利用qualifier把dst dff的clk关掉。

第四种情况:在data path中关闭dff1 的输出(用mux或者and),只有Q在得到qualifier允许之后才可以把它传递给dff2

本文讨论了在多异步复位域设计中如何避免亚稳态问题,特别是RDC(ResetDominanceCondition)和CDC(ClockDomainCrossing)。重点提到使用同步释放、隔离复位域、正确配置TCL脚本以及在设计中实施合理的时序控制来确保复位的可靠性和信号完整性。

本文讨论了在多异步复位域设计中如何避免亚稳态问题,特别是RDC(ResetDominanceCondition)和CDC(ClockDomainCrossing)。重点提到使用同步释放、隔离复位域、正确配置TCL脚本以及在设计中实施合理的时序控制来确保复位的可靠性和信号完整性。

4520

4520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?