一、实验内容

实现Cache(数据Cache)及其地址变换逻辑(也叫Cache控制器),采用直接相联地址变换,CPU从Cache读数据,若读不到,还必须考虑先从主存中读取数据,然后再将数据写到Cache中,之后,将数据送往CPU;其次,CPU还要向存储器写数据。

说明:CLK为系统时钟(用于计数器计数控制等操作),CLR为系统总清零信号(清区表存储器、计数器),WCT为写Cache区表存储器信号,AB31..AB0为CPU访问内存的地址(地址总线),32位数据为DB31..DB0(数据总线),RD(为0,读)为Cache的读信号,MWr(为1,写)为主存的写信号,MRd(为0,读)为主存的读信号,M(为1,有效,命中)为Cache有效位标志信号(区表存储器标志位),CA17..CA0为Cache地址,MD31..MD0为主存送Cache的数据,D31..D0为Cache送CPU数据,LA3…LA0为块内地址。

二、实验原理

本实验采用的地址变换是直接相联映象方式,这种变换方式简单而直接,硬件实现很简单,访问速度也比较快,但是块的冲突率比较高。其主要原则是:主存中一块只能映象到Cache的一个特定的块中。

假设主存的块号为B,Cache的块号为b,则它们之间的映象关系可以表示为:

b = B mod Cb

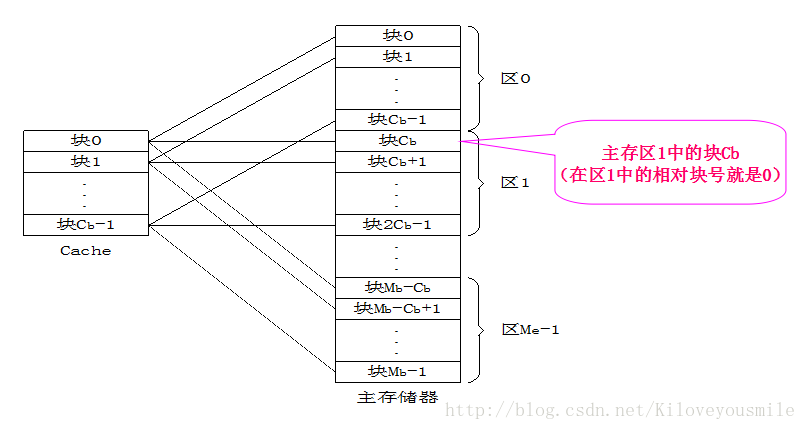

其中,Cb是Cache的块容量。设主存的块容量为Mb,区容量为Me,则直接映象方法的关系如图1所示。把主存按Cache的大小分成区,一般主存容量为Cache容量的整数倍,主存每一个分区内的块数与Cache的总块数相等。直接映象方式只能把主存各个区中相对块号相同的那些块映象到Cache中同一块号的那个特定块中。例如,主存的块0只能映象到Cache的块0中,主存的块1只能映象到Cache的块1中,同样,主存区1中的块Cb(在区1中的相对块号是0),也只能映象到Cache的块0中,看图1。根据上面给出的地址映象规则,整个Cache地址与主存地址的低位部分是完全同的。

|:图1 直接相连方式

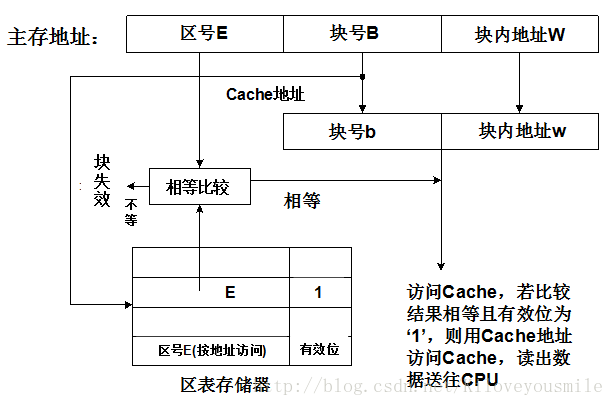

直接映象方式的地址变换过程如图2 所示,主存地址分为三个部分:区号E、块号B和块内地址W;Cache地址分为两部分:块号b和块内地址w。主存地址中的块号B与Cache地址中的块号b是完全相同的。同样,主存地址中的块内地址W与Cache地址中的块内地址w也是完全相同的,主存地址比Cache地址长出来的部分称为区号E。

|:图2 直接相联地址变换示意图

在程序执行过程中,当要访问Cache时,为了实现主存块号到Cache块号的变换,需要有一个存放主存区号的小容量存储器(称为区表存储器),这个存储器的容量与Cache的块数相等,字长为主存地址中区号E的长度,另外再加一个有效位(命中/失效)。

从主存地址到Cache地址的变换过程中,首先用主存地址中的块号B去访问区表存储器(用块号B作为区表存储器的地址,访问它),然后,将读出来的区号与主存地址中的区号E进行比较,比较结果相等,有效位为1,则Cache命中,表示要访问的那一块已经装入到Cache中了,可以直接用块号及块内地址组成的缓冲地址到缓存Cache中取数,把读出来的数据送往CPU;如果比较结果不相等,有效位为1,可以进行替换,如果有效位为0,可以直接调入所需块。至于比较不相等情况,不论有效位是1或0均为Cache没有命中,或称为Cache失效,表示要访问的那个块还没有装入到Cache中,这时,要用主存地址去访问主存储器,先把该地址所在的块读到Cache中,然后再读取Cache中该地址的数据送CPU。

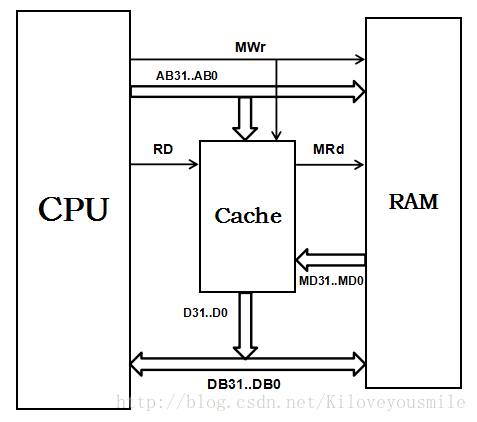

Cache和CPU以及存储器的关系如下图所示。

|:图3 Cache的基本框架图

如图3所示,32位主存地址为AB31..AB0(地址总线),32位数据为DB31..DB0(数据总线),RD(为0,读)为Cache的读信号,MWr(为1,写)为主存的写信号,MRd(为0,读)为主存的读信号,D31..D0为Cache送往CPU的数据信号(出口处经过一个三态缓冲器然后再输出),MD31..MD0为存储器RAM送往Cache的数据信号。

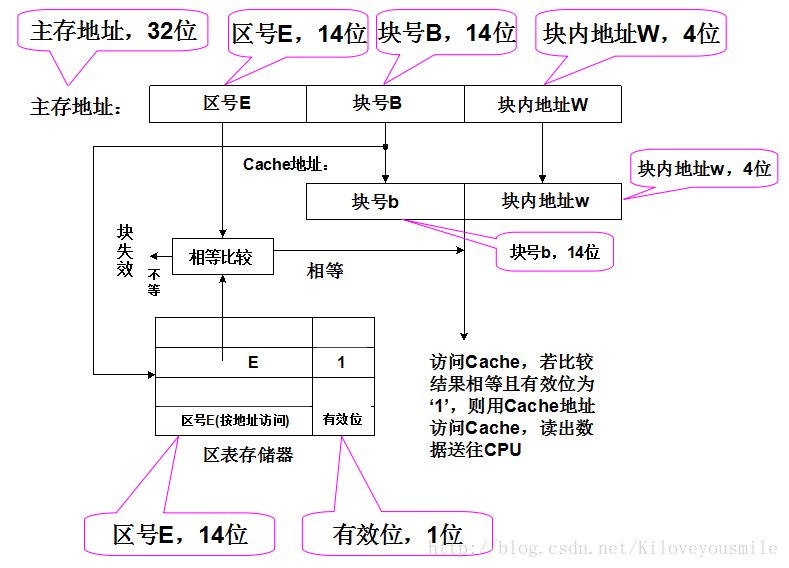

如图4所示,区号E取14位,块号B为14位,块内地址为4位,这样Cache地址就是18位了,其中Cache块号b为14位,块内地址w为4位,所以Cache容量为256KB(2^18)个单元,块号b取14位,那么Cache分为16KB(2^14)块,块内地址w取4位,则每块为16个单元(每个单元一个字节)。

|:图4 地址分段划分示意图

实现Cache的存储体的方法是先实现一个8位的存储单元,然后用这个8位的存储单元来构成一个256Kb X 8位的Cache(地址18位)。

再实现一个15位(14+1)的存储单元,然后,用这个15位的存储单元来构成一个16k X 15位的区表存储器(地址14位与块号B相同),用来存放区号(14位)和有效位M(1位)。在这个部分中,还要实现一个区号E比较器,也就是如果主存地址的区号E和区表存储器中按块号B为地址取出的相应单元中的区号E相等,有效位标志为M,且有效位M=1时,则Cache命中,否则Cache失效,M=0时表示Cache失效。

当Cache命中时,就将Cache存储体中相应单元的数据送往CPU,这个过程比较简单。当Cache失效时,就将主存中相应块中的数据读出写入Cache中,这样Cache控制器就要产生主存储器的读信号MRd(为0,读),由于每个Cache块占十六个单元,按32 位(4个字节)为访问存储器单位,那么需要连续访问4次主存,读取存储器中该块的数据,即16个字节,然后写入Cache相应块中,最后再修改区表存储器。至于访问主存的方法,要用到计数器。写数据时,如果Cache中有该地址数据,则修改,然后修改存储器该地址内容(MWr为1,写,为主存的写信号);如果Cache中无该地址数据,就直接修改存储器该地址单元内容。读/写存储器时,要注意互锁情况。

三、实验代码实现

主要需要实现两个模块,一个十RAM模块,一个是cache模块。这里,先实现RAM模块:

RAM.v

`timescale 1ns / 1ps

module RAM(

input wire CMWr,//cache 和 主存 的写信号

input wire MRd,//主存读信号

input wire[2:0] counterFromCache,//读取数据的计数器

input wire[31:0] Address,//地址

input wire[

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5773

5773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?