目录

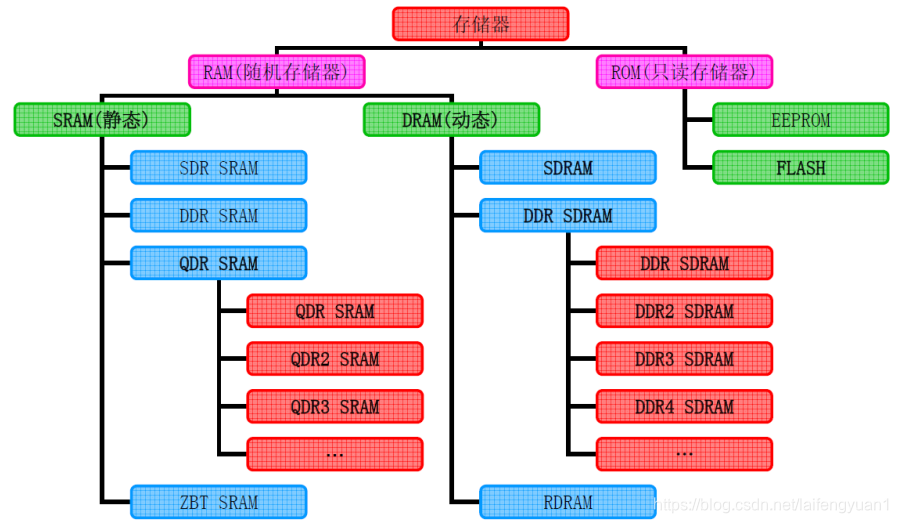

一、ROM与RAM介绍

ROM:只读存储器,非易失性

RAM:随机存取存储器,易失性

二、SDRAM的简介

1、SDRAM的发展简介

SDRAM 全称:同步动态随机访问存储器(Synchronous Dynamic Random Access Memory)

由第一代单数据率(Single Data Rate)SDR SDRAM,到后面的第二代双数据率(Double Data Rate)DDR SDRAM,以及后面更加先进的DDR2、DDR3、DDR4、DDR5、DDR6

SDR SDRAM 与 DDR SDRAM的主要区别

- SDR 只在时钟的上升沿传输数据

- DDR 在时钟的上升沿和下降沿都能传输数据,即一个周期内可以传输两次数据。因此可以提供两倍于SDR SDRAM的性能

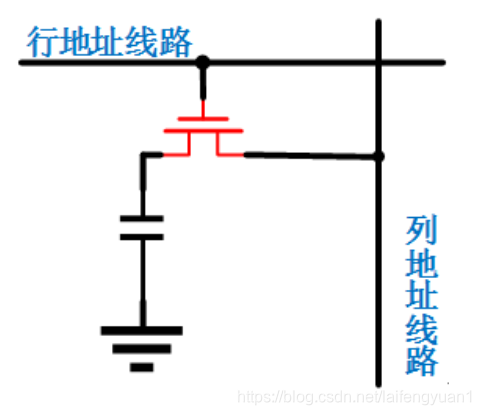

2、常见DRAM单元的基本单元介绍

(1)DRAM存储单元主要有四部分组成:

-

Storage Capacitor(存储电容):通过存储在其中电荷的多和少,或者说电容两端电压差的高低,来表示逻辑上的1和0

-

Access Transistor(访问晶体管):它的导通和截止,决定了允许或者禁止对存储电容所存储的信息进行读取和改写

-

Wordline(字线/行地址线路):它决定了访问晶体管的导通或者截止

-

Bitline(位线/列地址线路):它是外界访问存储电容的唯一通道,当访问晶体管导通时,外界可以通过Bitline来对存储电容进行读取或者写入操作

(2)基本读写原理:

-

读数据:读数据时候,Wordline(字线/行地址线路)需要先将Wordline设置为高电平,打开Access Transistor(访问晶体管),然后读取Bitline上的数据

-

写数据:写数据时候,先将要写入的电平状态设定到Bitline上,然后打开Access Transistor,通过Bitline来改变Storage Capacitor 所存储的信息

注:如按照以上流程对DRAM Storage Cell进行读写会遇到以下问题

-

外界的逻辑电平与Storage Capacitor的电平不匹配:Bitline电容值比Storage Capacitor要大很多,当Access Transistor 导通后,如果Storage Capacitor存储信息为1,Bitline电压变化很小。外界电路无法通过Bitline读取Storage Capacitor存储的信息

-

进行一次读取操作后,Storage Capacitor 存储的电荷会发生变化

-

由于Capacitor的物理特性,即使不进行读写操作,其所存储的电荷会慢慢减少

三、SDRAM的尺寸与管脚介绍

1、DDR的常见尺寸与Ball数

DDR的常见封装与球数:FBGA;78Ball与96Ball

其中96Ball的外形尺寸上,比起78Ball的要更长一点。因此通过一个DDR颗粒的外形尺寸,基本上可以判断一个颗粒的球数。

-

78Ball(mm):(长基本为11mm或以上)

8Gb:7.5x11、8x12、9x13、10x11

16Gb:9x11、10x11

-

96Ball(mm):(长基本为13mm或以上)

8Gb:7.5x13.5、7.5x13、8x14、9x14、

16Gb:9x13、10x13

2、DDR的管脚类型介绍

注:主要介绍DDR4相关颗粒的管脚类型

(1)引脚类型可以主要分为以下5种:(仅列举部分)

| 信号分组 | 信号 |

|---|---|

| 电源 | VDD、VDDQ、VPP、VREFCA、VSS、VSSQ |

| 时钟 | CK_t、CK_c |

| 地址/命令 | A[17:0]/A[14:0]、CAS_n、RAS_n、WE_n、BA[1:0]、BG[1:0]...... |

| 控制 | CKE、ODT、CS_n、Ten...... |

| 数据 | DQS_t、DQS_c、DQ[15:0]/DQ[7:0]、DM_n...... |

(2)引脚介绍

| 符号 | 定义 |

|---|---|

| A[17:0] | Address inputs:指令执行提供行地址、为读写指令提供列地址 |

| A10 / AP | Auto precharge:自动预充电 |

| A12 / BC_n | Burst chop:突发终止,用以向下兼容DDR的不同突发长度 |

| ACT_n | Command input:激活命令 ACT_n为低时,视为行地址输入的激活指令 ACT_n为高时,视为常规命令 |

| BA[1:0] | Bank address inputs:定义对哪个块可使用ACTIVATE,READ,WRITE,PRECHARGE等命令,同时还确定在MODE REGISTER SET 命令下要访问哪个模式寄存器 |

| BG[1:0] | Bank group address inputs:定义对哪个块组可使用REFRESH,ACTIVATE,READ,WRITE,PRECHARGE等命令。同时还确定在MODE REGISTER SET 命令下要访问哪个模式寄存。BG[1:0]被使用在x4,x8的配置中。在x16中没有用到BG1 |

| C0 / CKE1 C1 / CS1_n C2 / ODT1 | Stack address inputs:这些输入引脚仅在设备被堆叠时使用,在2/4/8层高的堆栈元件系统中,次信号用来选择每一个slice。对于其他堆叠配置时候,如4H、8H配置下,假定成单负载可被当成 chip id |

| CK_t CK_s | Clock:差分时钟输入,所有地址、命令、控制输入信号将在CK_t正边沿与CK_s负边沿的交叉处进行采样 |

| CKE | Clock enable:时钟使能。 当CKE为高电平时,启动内部时钟信号,设备输入缓冲以及输出驱动单元。 当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。 在上电以及初始化序列REFRESH过程中,VPREFCA与VREF将变得稳定,并且在后续的操作过程中度需要保持稳定,包括SELF-REFRESH。 CKE必须在读写操作中保持稳定高电平。 在POWER DOWN过程中,除了CK_t、CK_c、ODT、RESET_n、CKE都将被禁用输入缓冲。在SELF-REFRESH过程中,除了RESET_n、CKE都将被禁用输入缓存 |

| CS_n | Chip select:片选信号。 当CS_n被锁存为高电平时候,将忽略所有命令。在多rank的系统中,CS_n可以用来选择外部rank,并且此信号还可以作为命令编码的一部分 |

| DM_n UDM_n LDM_n | Input data mask:DM_n是写入数据的输入掩码信号。 当DM_n为低电平时,写命令的输入数据对应的位将被丢弃。 DM_n在DQS的两个边沿都采样。 DM不支持x4配置 UDM_n和LDM_n在x16设备中使用。UDM_n与DQ[15:8],LDM_n与DQ[7:0]相关联 DM、DBI、TDQS功能将由模式寄存器来进行设置 |

| ODT | On-die Termination:片上终结电阻。 ODT为高电平时候,开启DDR4 SDRAM内部的终结电阻。 x4和x8设备中,ODT仅对每个DQ、DQS_t、DQS_c、DM_n/DBI_n/TDQS_t、TDQS信号有用。x16设备中,ODT仅对DQ、DQSU_t、DQSU_c、DQSL_t、DQSL_c,、UDM_n、LDM_n信号有用。 |

| PAR | Parity for command and address:命令与地址总线奇偶校验输入,可以通过模式寄存器来进行关闭或者启用。 当启用奇偶校验时,奇偶校验的信号包含所有命令和地址输入,包括ACT_n、RAS_n/A16、CAS_n/A15、WE_n/A14, A[17:0]、A10/AP、A12/BC_n、BA[1:0]、BG[1:0] 以上所有输入的奇偶性都应该在 CK_t的上升沿 与 CS_n 为低电平时保持住 |

| RAS_n / A16 CAS_n / A15 WE_n / A14 | Command inputs:此组命令与CS_n可构成当前命令的输入编码,有多重含义。 当ACT命令时(即ACT_n为低电平时),三个信号作为地址线来使用 当非ACT命令时,这三个信号作为命令编码使用,如:读、写等其他命令操作都可以通过这三个信号实现 |

| RESET_n | Active Low asynchronous reset:低电平有效的异步复位。 此信号为低电平时,设备复位。 在正常操作时,此信号必须为高电平。此信号为轨到轨的CMOS类型的信号,DC高低电平分别为VDD的80%和20% |

| TEN | Connectivity test mode:连通测试使能。 此信号高电平时开启,低电平时关闭。 在正常操作时,此信号必须为低电平。此信号为轨到轨的CMOS类型的信号,DC高低电平分别为VDD的80%和20%。 |

| DQ | Data input/output:数据输入、输出,双向数据总线。 DQ在x4、x8、x16设备中分别表示成DQ[3:0]、DQ[7:0]、DQ[15:0]。 如果通过模式寄存器使能写CRC,CRC将在数据burst结束时就会附加。若MR4中的A4为高电平,则测试中DQ0-3的任何一根DQ信号都可以代表VREF的电平。 |

| DBI_n UDBI_n LDBI_n | DBI input/output:数据总线倒置。 DBI_n是应用在x8设备中的数据总线反转的输入/输出信号 UDBI_n 和 LDBI_n用于x16配置中,其中UDBI_n与DQ[15:8]相关、LDBI_n与DQ[7:0]相关。 x4设备不支持DBI特性。DBI特性可以通过模式寄存器来配置读或者写。DM、DBI和TDQS功能都可以通过模式寄存器来进行配置 |

| DQS_t DQS_c DQSU_t DQSU_c DQSL_t DQSL_c | Data strobe:数据选通信号。 输入时与写数据同时有效,输出时与读数据同时有效。与读数据时边沿对齐,写数据时跳变沿位于写数据的中心。 在x16设备中,DQSL对应DQ[7:0],DQSU对应DQ[15:8]上的数据。 对应x4、x8设备DQS分别对应DQ[3:0]、DQ[7:0]上的数据。 对于DDR4 SDRAM仅支持选通信号为差分信号,不支持单根信号的数据选通信号 |

| ALERT_n | Alert output:警示信号。 此信号可代表DRAM中产生的多种错误,如:CRC校验错误、命令与地址的奇偶校验错误等。可以通过模式寄存器进行开启 |

| TDQS_t TDQS_c | Termination data strobe:终端数据选通。 TDQS_t、TDQS_c仅在x8系统中使用。当通过模式寄存器启用时DRAM将启用类似终止电阻的功能,TQDS_t、TDQS_c将会应用于DQS_t、DQS_c。 当通过模式寄存器禁用TDQS功能时,DM / TQDS_t 将会提供DATA MASK功能,TQDS_c未被使用。 在x4、x16设备中的模式寄存器必须关闭TDQS功能。 |

| VDD | Power supply:内核供电电源 1.2V ± 0.060V |

| VDDQ | DQ power supply:DQ供电1.2V ±0.060V |

| VPP | DRAM activating power supply:DRAM激活供电:2.5V –0.125V/+0.250V |

| VPREFCA | 用于命令、控制、寻址的参考电压 |

| VSS | 地线 |

| VSSQ | DQ地线 |

| ZQ | Reference ball for ZQ calibration:用于ZQ校准的参考引脚,外部绑定240Ω电阻 |

1521

1521

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?