wire型,意为连线型,一般用于组合逻辑(CL)之中。verilog HDL模块中的输入输出信号类型默认时自动定义为wire型。

reg型,意为寄存器型,既可以用组合逻辑实现,亦可用于时序逻辑中,即用触发器(filp-flop)实现。

wire型和reg型在verilog HDL语法中的区别在于,wire型数据通常用assign语句赋值,reg型数据必须被放在过程语句中(如initial、always)中,通过过程赋值语句赋值。

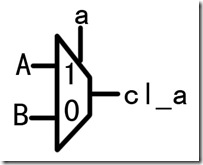

同样一个组合电路,不光可以用wire型数据来写,实际上也可以用reg型数据写:

(1) wire写法

wire cl_a;

assign cl_a = a ?A : B;

(2) reg写法

本文介绍了Verilog HDL中wire型和reg型的电路应用区别。wire型常用于组合逻辑,而reg型则既适用于组合逻辑也适用于时序逻辑。wire型数据通过assign语句赋值,reg型数据则需在过程语句如initial或always中通过过程赋值。reg型在用于组合逻辑时,always块参数为组合逻辑参数,而在实现时序逻辑(如触发器)时,参数通常为时钟边沿,并使用非阻塞赋值。

本文介绍了Verilog HDL中wire型和reg型的电路应用区别。wire型常用于组合逻辑,而reg型则既适用于组合逻辑也适用于时序逻辑。wire型数据通过assign语句赋值,reg型数据则需在过程语句如initial或always中通过过程赋值。reg型在用于组合逻辑时,always块参数为组合逻辑参数,而在实现时序逻辑(如触发器)时,参数通常为时钟边沿,并使用非阻塞赋值。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?