过程赋值语句多用于对reg型变量进行复制,过程赋值有阻塞复制和非阻塞赋值两种。

非阻塞赋值的符号为:<=

阻塞赋值符号为:=

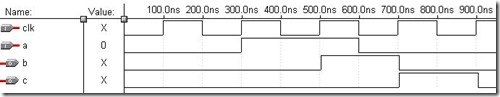

(1)非阻塞赋值的例子:

reg c,b;

always@(posedge clk)

begin

b <= a;

c <= b;

end

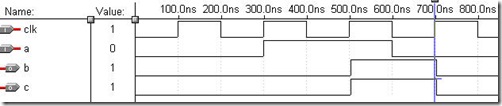

(2)阻塞赋值的例子:

reg c,b;

always @ (posedge clk)

begin

b = a;

c = b;

end

上述例子中,使用非阻塞赋值方法,其中的每个<=都可以理解为一个寄存器。而在同一

个时钟下面采用的非阻塞赋值方法,模块内所有寄存器都同时随时钟跳变。这是硬件处理

的精髓,也是时序电路中大量使用非阻塞赋值的原因。

在实际书写verilog HDL代码的过程中,对于always中reg型变量,如果不是处理组合逻

辑,尽量不使用阻塞赋值的方法。这主要是基于代码的可综合性考虑的,因为在verilog

HDL代码编译的时候,对于有些从后编译的编译器,阻塞赋值会找成时序上与预想的不

一致。对于以上阻塞赋值的例子,采用非阻塞方法应该写为

reg c,b;

always @ (posedge clk)

begin

b <= a;

c <= a;

end

实现电路和原方法一样。

而在always用于组合逻辑中,采用阻塞赋值表明未使用寄存器。

如

reg a,A,B,f_a;

always @ (a or A or B)

begin

f_a = a ?A : B;

end

以下是使用阻塞和非阻塞赋值应遵循的一些基本原则,这些原则有利于防止竞态(race condition)的发生。

(1)当用always块来描述组合逻辑(combinational logic)时,应当使用阻塞赋值。

(2)对于时序逻辑(sequential logic)的描述和建模,应当使用非阻塞赋值。

(3)在同一个always模块中,最好不要混合使用阻塞赋值和非阻塞赋值,对同一变量

既进行阻塞赋值,又进行非阻塞赋值,在综合时会出错。所以always中要么全部使用非

阻塞赋值,要么把阻塞赋值和非阻塞赋值分在不同的always中书写。

(4)尽量不要再在多个不同的always块中对同一变量赋值。

(5)使用$strobe显示使用非阻塞赋值的变量。

参考文献:

【1】Nonblocking Assignments in Verilog Synthesis, Coding

Styles That Kill! Clifford E. Cummings

【2】数字系统设计与Verilog HDL 王金明

本文详细解析了Verilog HDL中的过程赋值语句,包括阻塞赋值和非阻塞赋值的区别及应用场景。介绍了这两种赋值方式在时序逻辑和组合逻辑中的正确使用方法,并给出了具体的代码示例。

本文详细解析了Verilog HDL中的过程赋值语句,包括阻塞赋值和非阻塞赋值的区别及应用场景。介绍了这两种赋值方式在时序逻辑和组合逻辑中的正确使用方法,并给出了具体的代码示例。

5115

5115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?