UCIE PHY LSM链路训练

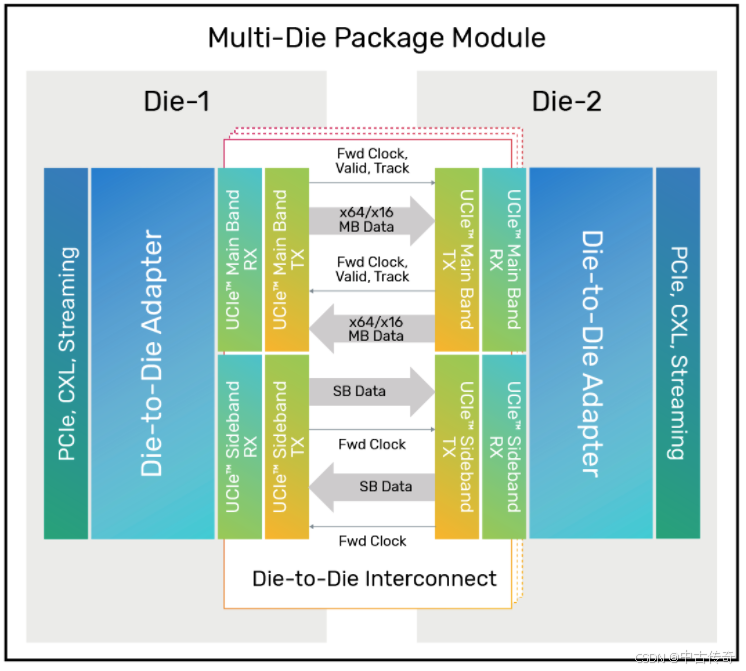

UCIe™ 物理层包括链路初始化、训练、电源管理状态、通道映射、通道反转和加扰。 UCIe™ 控制器包括芯片间适配器层和协议层。适配器层通过链路状态管理以及协议和flit格式的参数协商来确保可靠传输。 UCIe™架构支持多种标准协议,例如PCIe、CXL和Streaming。

今天继续介绍UCIE PHY LSM各状态;

1 UCIE PHY LSM

1.1 RESET

RESET:该状态是起始状态,等待相关PLL Lock稳定后,即进入下一状态;主要有:

- SideBand Clock固定800 MHz稳定;

- MainBand及D2D Adapter的clock稳定;

- MainBand时钟为最低IO速率(2GHz,即对应4 GT/s);

- 触发链路训练条件之一被触发:1.UCIE Link Control寄存器Link Trainning位被置1;2.Adapter触发RDI链路训练;3.Sideband 接口上连续接收到两笔 SBINIT Pattern (64 UI Clock + 32 UI Low);

1.2 SBINT

SBINT状态期间,其中TX侧Module会在SB Clock 和 Data Lane上同时发送clock pattern, RX在检测到连续2个clock pattern后即表示成功。此后,其 Tx 继续发送 4 个 Clock Pattern,然后停止发送 Clock Pattern。继续发送{SBINT Out of Reset} 的massage以及{SBINT done req}和{SBINT done resp}的message;然后即会进入下一状态。

1.3 MBINT

MBINT该状态又具体分为6个子状态,如下图所示,依次执行。在 MBINIT 期间,主要是进行 Mainband 初始化、修复或减宽。Mainband Lane 的检测跟 Sideband 稍有不同,Sideband 是在 Clock、Data Lane (Normal & Redundant for Advanced) 上同时发生 Test Pattern,而 Mainband 是按照 Clock、Track、Valid、Data 依次测试。

1.3.1 MBINT.PARAM

在该状态期间,链路两端的 UCIe Module 进行参数交换,以协商链路速度、链路宽度及其他 PHY 相关参数。协商交换的具体参数有:Voltage Swing、Maximum Data Rate、Clock Mode、Clock Phase、Module ID。这具体参数会直接在SideBand Message上来传输{MBINIT.PARAM Configuration Req}、{MBINIT.PARAM Configuration Resp};

1.3.2 MBINIT.CAL

MBINIT.CAL 进行一些 Calibration 相关操作,比如 Tx 占空比校正、Rx 偏移及 Rx 参考电压 Vref 校正。涉及到的 SB Msg:{MBINIT.CAL Done Req}、{MBINIT.CAL Done Resp};

1.3.3 MBINIT.REPAIRCLK

对于先进封装,该状态下检测 Clock 及 Track 功能,存在问题时进行 Clock 及 Track Lane 修复–即替换redundant lane;对于标准封装,仅检测 Clock 及 Track Lane 的功能。每一根 Clock 或 Track Lane 先后独立进行检测,检测其是否存在短路或断路。这几条 Lane 的检测顺序为:TCKP_L -> TCKN_L -> TRDCK_L -> TTRK_L。

检测过程如下:

1.检测之前,先通过 {MBINIT.REPAIRCLK init req}、{MBINIT.REPAIRCLK init resp} 进行握手。

2.检测的时候,在 Clock 或 Track Lane 上发送 128 次特定格式的 Clock Repair Pattern (16 cycle pattern + 8 cycle low)。Tx 发送完 Clock Repair Pattern 后,发送 {MBINIT.REPAIRCLK result req} 给对方,请求对方反馈检测结果。

3.Rx 该条 Lane 上连续收到 16 次即可认为该 Lane 完好。如若该 Lane 没有检测到,表明该 Lane 发生了断路;若该 Lane 及之外的 Lane 同时检测到了,表明发生了短路。检测完后将检测结果记录在相关寄存器中。

4.Rx 在收到 {MBINIT.REPAIRCLK result req} 后通过 {MBINIT.REPAIRCLK result resp} 反馈结果给对方。

经过以上步骤会得到以下情况:1.Lane功能都正常;2.需要修复且可以修复:如果需要 Lane Repair 且可修复,则进行 Lane Repair 相关操作。Tx 发送 {MBINIT.REPAIRCLK apply req} 给对端,收到对端发来的 {MBINIT.REPAIRCLK apply resp} 后即可在 Tx 进行 Clock Lane Repair。Tx 修复完成后,需要检测下是否修复成功。检测时不检测 Redundant Lane 了,已经被占用了;3.需要修复但无法修复。 考虑到只有一条 Redundant Lane,如果有 2 条及以上的 Clock Lane 有问题,那就不可修复了,则 Rx 进行相关握手跳至 TRAINERROR 状态。

如果无需进行 Clock Lane Repair 或已经修复完毕且检测成功,发送 {MBINIT.REPAIRCLK done req},收到对端反馈的 {MBINIT.REPAIRCLK done resp} 后,状态机进入 MBINIT.REPAIRVAL 修复 Valid Lane。

1.3.4 MBINIT.REPAIRVAL

该过程检测 Mainband Data Valid Lane,若存在短路或短路,则进行修复。检测及修复过程跟 Clock/Track Lane 的过程类似,只是检测的 Lane、Pattern 及 Msg 稍有区别:1.检测的 Lane 有 TVLD_P 及 TRDVLD_P,先后依次检测。2.测试 Pattern 为 4 UI High + 4 UI Low。3.Msg 跟 Clock Repair Msg 类似,所有的 Msg 名称由 REPAIR 换成了 REPAIRVAL。

1.3.5 MBINIT.REVERSALMB

只有在 Mainband 的 Clock 及 Valid Lane 能够正常工作的前提下,MBINIT.REVERSALMB 状态才有效,否则 Lane Reversal 是没有意义的。如有需要,该状态时进行 Lane 序重排。

1.3.6 MBINIT.REPAIRMB

MBINIT.REPAIRMB 状态下,对 Mainband Data Lane 的功能进行检测。若先进封装的 UCIe 出现坏 Lane,在修复能力之内时进行坏 Lane 修复,在修复能力之外时进入 TRAINERROR 状态。若标准封装的 UCIe 出现了坏 Lane,进行减宽操作,比如:即将 X16 减宽为 X8。

1.4 MBTRAIN

MBTRAIN 状态下对 Mainband 进行训练,将 UCIe 链路速度提升到双方协商好的最高速率,并调整 Clock 边沿到最佳采样时刻。UCIe 链路两端的两个 UCIe Module 通过 Sideband 上的 Msg 进行握手来进入和退出各个子状态,如果进入某个子状态后不需要相关操作,可以退出去,但这个子状态还是要进来的。

若在链路训练连续失败次数达到指定上限之后,LSM 回退到 RESET 状态,等待再次触发链路训练。若软件或 RDI 触发的链路训练失败,或 Link Up 转为 Link Down,物理层需要上报 RDI 的 Fatal Error。

1.5 LINKINIT

LINKINIT 是 LSM 进入 ACTIVE 之前的最后一个状态,用以 D2D Adapter 完成初始链路管理。该状态时,进行 RDI Bring Up。RDI Bring Up 成功之后,UCIe Link Control Register 中的 Start UCIe Link Training 字段清零,LFSR 复位。

1.6 ACTIVE

PHY LSM 进入 ACTIVE 状态,表示物理层已经完成了初始化,RDI 已经 Active,上层可以在 UCIe Link 上交换数据了。此时传输的数据是经过 LFSR 加扰的。RDI burig up之后就进入FDI bring up。

1.7 L1/L2

L1 及 L2 是 UCIe 的低功耗状态,其比 ACTIVE 状态下的 Dynamic Clock Gating 功耗更低。本端 Adapter 及对端均可以请求退出低功耗状态。L1 退出后是 MBTRAIN.SPEEDIDLE,L2 则是直接退出到 RESET 状态。

1.8 PHY.RETRAIN

Local Die 的 Adapter、PHY 及 Remote Die 都可以触发 PHY 进入 Retrain。 进入 PHYRETRAIN 状态后,变量 PHY_IN_RETRAIN 置一。

- Local Adapter 发起 Retrain

- Local PHY 发起 Retrain

- Remote Die 发起 Retrain

1.9 TRAIN.ERROR

UCIe 初始化期间发生错误或者需要 LSM 回退到的 RESET 时,LSM 先进入 TRAINERROR 状态。若 Sideband 已经 Active 了(SBINIT 之后的状态),此时 UCIe 链路一端的 UCIe Module 需要进入 TRAINERROR,应跟链路对端进行握手,双双进入该状态。若 Sideband 还没 Active,则不必告诉对端,其自行进入 TRAINERROR 即可。对端长时间得不到相关响应也会自己进入 TRAINERROR。

涉及到的 Sideband Message 握手信号:{TRAINERROR Entry Req}和{TRAINERROR Entry Resp};

如果 Req 发出后 8ms 未等到 Resp,则直接进入 TRAINERROR。

这块是十分偏数模混合,涉及电气参数、时钟等,对于数字工程师来说,更多的还是controller,在这里还只是简单给大家介绍一下;

【REF】

1.https://www.cnblogs.com/wujianming-110117/p/16793479.html

853

853

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?