4.0 Logical Physical Layer

逻辑PHY包括以下功能:

• 链路初始化、训练和电源管理状态

• 字节到Lane的映射,用于通过Lane传输数据

• 互连冗余重映射(在需要时)

• 发送和接收侧带消息

• 扰码和训练模式生成

• Lane反转

• 宽度降级(如果应用)

4.1 Data and Sideband Transmission Flow

该规范定义了在物理Lane上发送和接收数据所使用的时钟、有效信号和数据。传输的数据由有效信号进行帧同步。

4.1.1 Byte to Lane Mapping

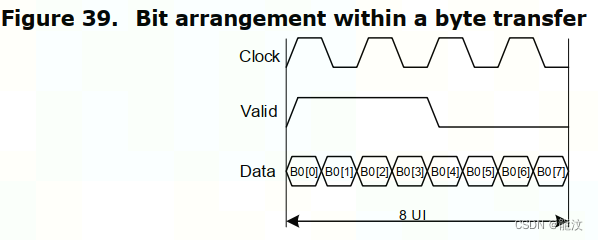

数据包以字节形式进行传输。在每个字节中,首先传输的是第0位(bit[0])。图39展示了在Lane0上进行一字节传输时的位排列示例。

每个字节都在单独的Lane上进行传输。字节0(B0)在Lane 0上传输,字节1在Lane 1上传输,以此类推。

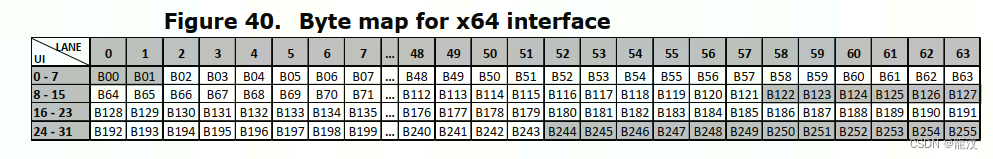

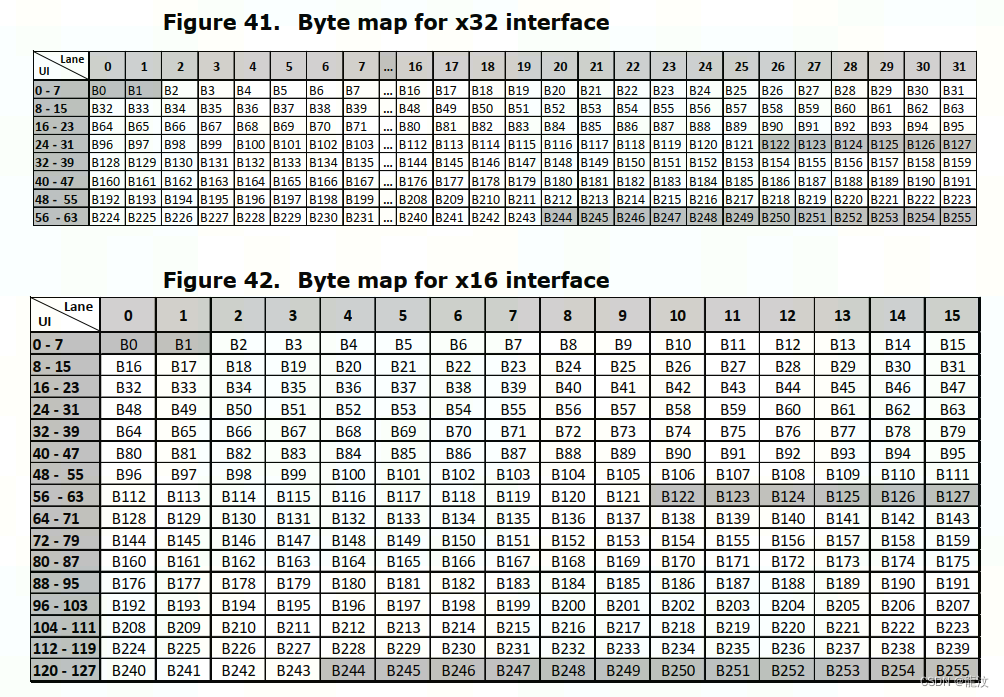

图40展示了通过x64接口(一个高级封装模块或四个标准封装模块)传输的CXL延迟优化Flit的示例。如果IO宽度变为x32或x16接口(标准封装),每个Lane上一字节的传输将保持不变,如图41和图42所示。

4.1.2 Valid Framing

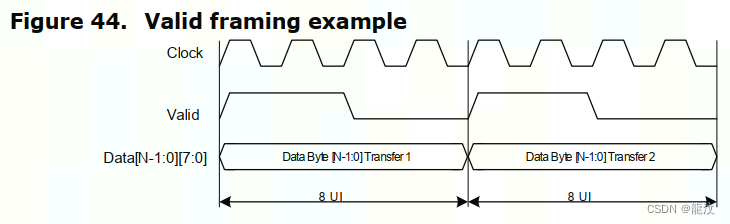

有效信号(valid)用于对传输的数据进行帧同步。对于每个8位的数据包,有效信号在前4个UI(单位间隔)期间被置位,然后在接下来的4个UI期间被取消置位。这将允许在原始模式或第3.0章中描述的各种Flit模式下进行数据传输,使用一个或多个有效帧。图44展示了一个示例,其中Transfer 1和Transfer 2可以来自同一个Flit或不同的Flit。

4.1.2.1 Valid Framing for Retimers

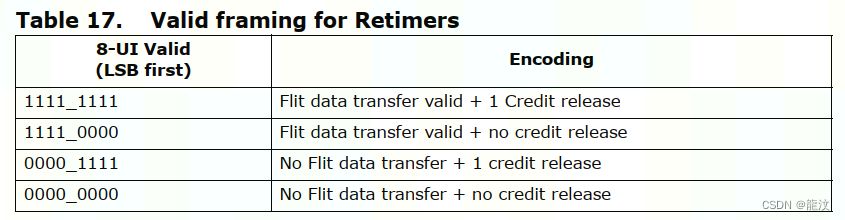

UCIe Retimer通过使用Valid信号向其本地的UCIe芯片释放信用,如下所述的编码方式。每个信用跟踪256字节的数据(包括任何FEC、CRC等)。Valid Framing编码确保了三重位翻转检测的保证。注意:必须注意的是,8UI块由发射器强制执行,并由本地UCIe芯片中的接收器进行跟踪。

4.1.3 Clock Gating

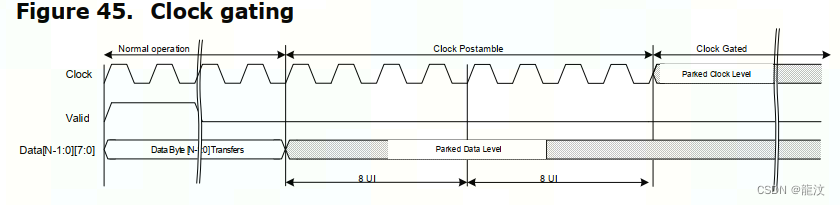

当Valid信号在提供了固定的16UI(8个周期)的后导时钟后变为低电平时,必须对时钟进行门控,除非已经协商了自由运行时钟模式。数据和时钟信号的停车电平在第5.11节中有描述。

4.1.4 Free Running Clock Mode

自由运行时钟模式被定义为在Valid保持低电平且接口上没有数据传输时,转发的时钟仍保持切换的模式。为了允许禁用正常操作或调试的动态时钟门控,必须支持此模式。在主通道链路训练之前,必须通过参数交换来协商此模式。

4.1.5 Sideband transmission

每个模块都支持一个带有串行数据和时钟引脚对的旁路接口。旁路数据包的格式和编码在第6.0章中展示,电气特性在第5.13节中展示。

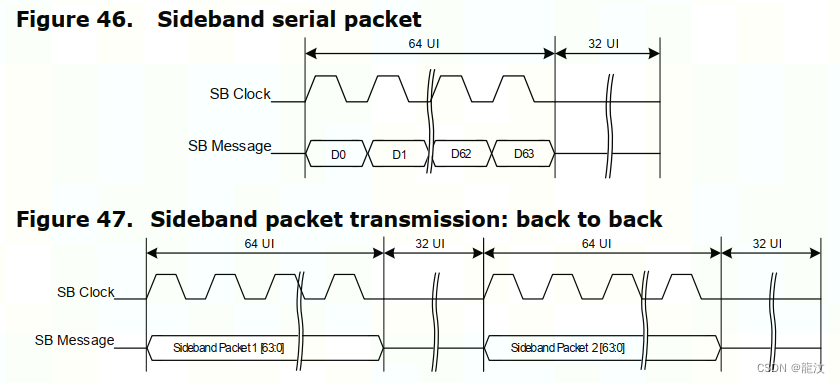

如第6.1.2节所示,旁路消息的格式定义为带有32位或64位数据的64位头部。在IO接口到远端芯片的位置上定义了一个64位的串行数据包,如图47所示。即使是32位数据,也会使用64位的串行数据包发送,其中高位使用0填充。在IO接口上,两个连续的旁路数据包之间由32位低电平分隔,如图46所示。

4.2 Lane Reversal

在第4.2节、第4.3节和第4.5节中使用了以下命名约定:

• TD_P:数据发送器的物理通道

• RD_P:数据接收器的物理通道

• TRD_P:冗余数据发送器的物理通道

• RRD_P:冗余数据接收器的物理通道

• TD_L:数据发送的逻辑通道

• RD_L:数据接收的逻辑通道

• TCKP_P、TCKN_P和TTRK_P:时钟和跟踪发送器的物理通道

• TCKP_L、TCKN_L和TTRK_L:时钟和跟踪发送器的逻辑通道

• RCKP_P、RCKN_P和RTRK_P:时钟和跟踪接收器的物理通道

• RCKP_L、RCKN_L和RTRK_L:时钟和跟踪接收器的逻辑通道

• TRDCK_P:冗余时钟/跟踪发送器的物理通道

• RRDCK_P:冗余时钟/跟踪接收器的物理通道

• TRDCK_L:冗余时钟/跟踪发送器的逻辑通道

• RRDCK_L:冗余时钟/跟踪接收器的逻辑通道

• TVLD_P、RVLD_P:有效发送器和接收器的物理通道

• TRDVLD_P、RRDVLD_P:冗余有效发送器和接收器的物理通道

• TVLD_L、RVLD_L:有效发送器和接收器的逻辑通道

• TRDVLD_L、RRDVLD_L:冗余有效发送器和接收器的逻辑通道

设备必须支持模块内的通道反转。通道反转的一个示例是,当本地芯片上的物理数据通道0连接到远端芯片上的物理数据通道(N-1)(物理数据通道1连接到物理数据通道N-2,依此类推),其中N为标准封装时为16,高级封装时为64。在高级封装中,冗余通道也会被反转。通道反转必须仅在发送器上实现。发送器会反转数据和冗余通道上的逻辑通道顺序。

跟踪、有效、时钟和旁路信号不能被反转。

通道反转在初始化和训练过程中被发现和应用(第4.5.3.3.5节)。

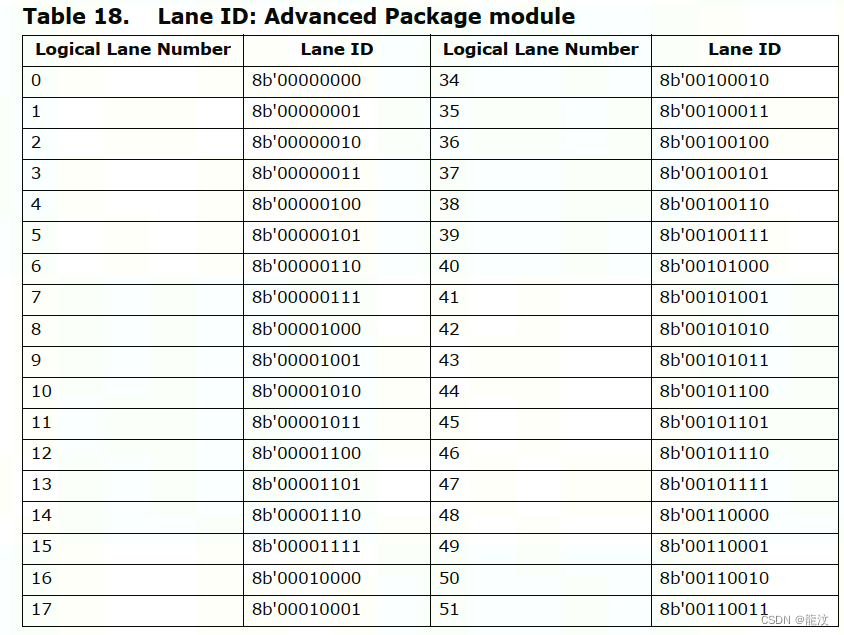

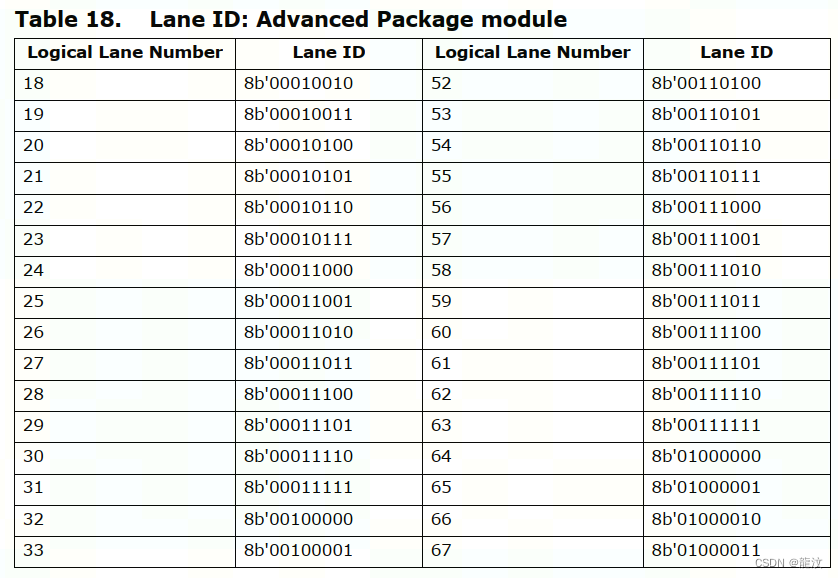

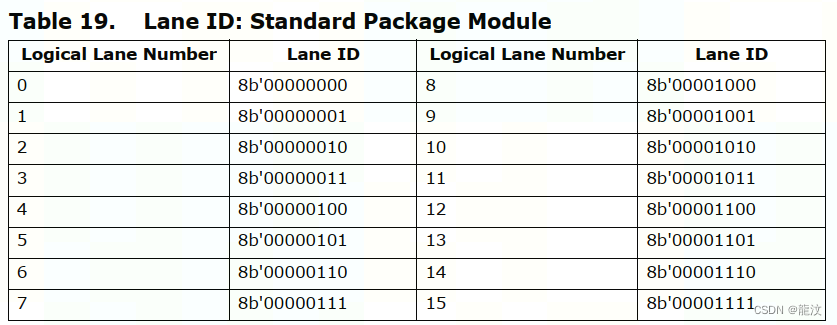

4.2.1 Lane ID

为了实现通道反转的发现,每个模块内的逻辑数据通道和冗余通道被分配了唯一的通道ID。分配的通道ID在表18和表19中分别显示为高级和标准封装模块。请注意,表18和表19中的逻辑通道号表示逻辑发送器和接收器通道。例如,逻辑通道号为0表示TD_L[0]/RD_L[0],依此类推。

在表18中,对于高级封装模块,逻辑通道号64、65、66和67分别表示逻辑冗余通道TRD_L[0]/RRD_L[0]、TRD_L[1]/RRD_L[1]、TRD_L[2]/RRD_L[2]、TRD_L[3]/RRD_L[3]。

4.3 Interconnect redundancy remapping

如第5.9节所讨论的,高级封装模块需要进行冗余重映射以从故障通道中恢复。本节提供了重映射的详细信息。

4.3.1 Data Lane repair

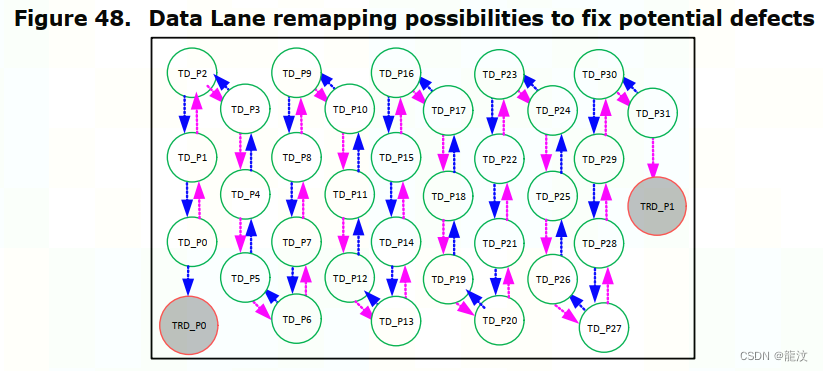

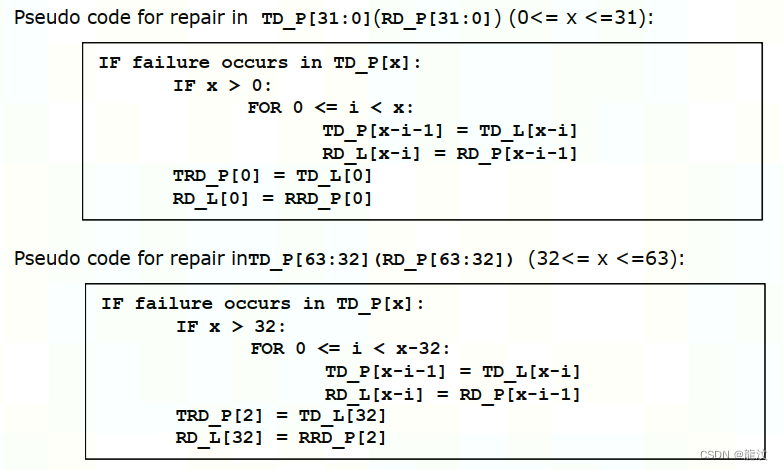

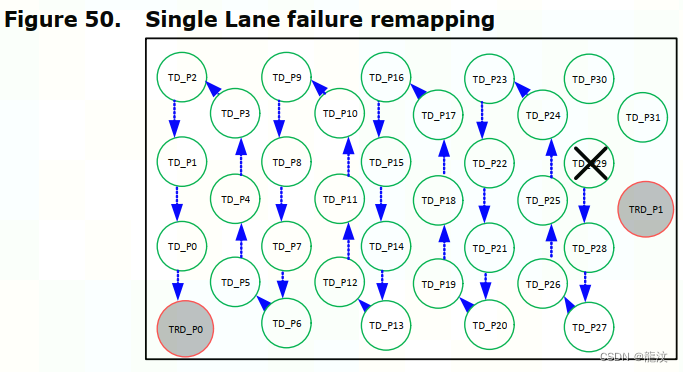

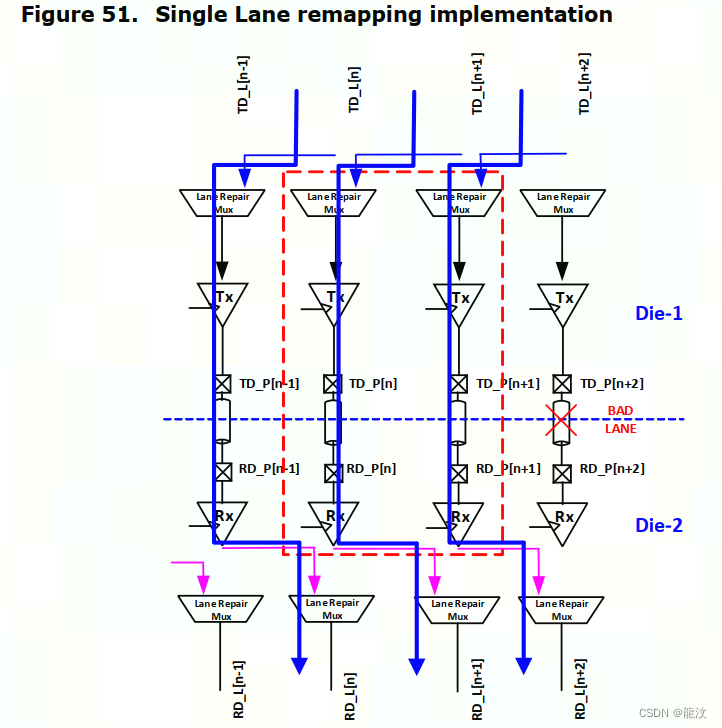

根据规范,每组32个数据通道支持最多对两个数据通道进行重映射(修复)。TD_P[31:0](RD_P[31:0])和TD_P[63:32](RD_P[63:32])被视为两个独立的32个通道组,可以分别使用冗余通道TRD_P[1:0](RRD_P[1:0])和TRD_P[3:2](RRD_P[3:2])进行修复。

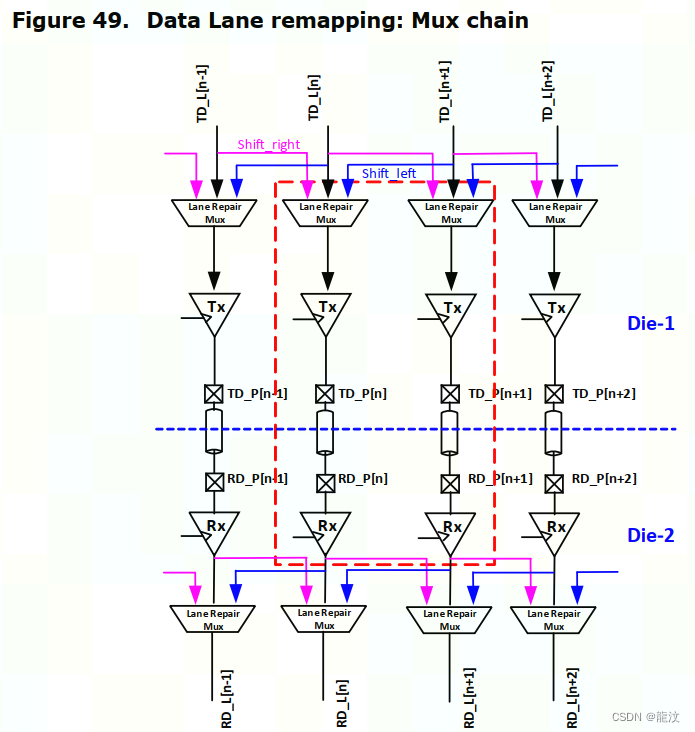

通道重映射通过"左移"或"右移"操作实现。"左移"是指将逻辑通道TD_L[n]上的数据流量复用到TD_P[n-1]上。"右移"是指将数据流量TD_L[n]复用到TD_P[n+1]上。

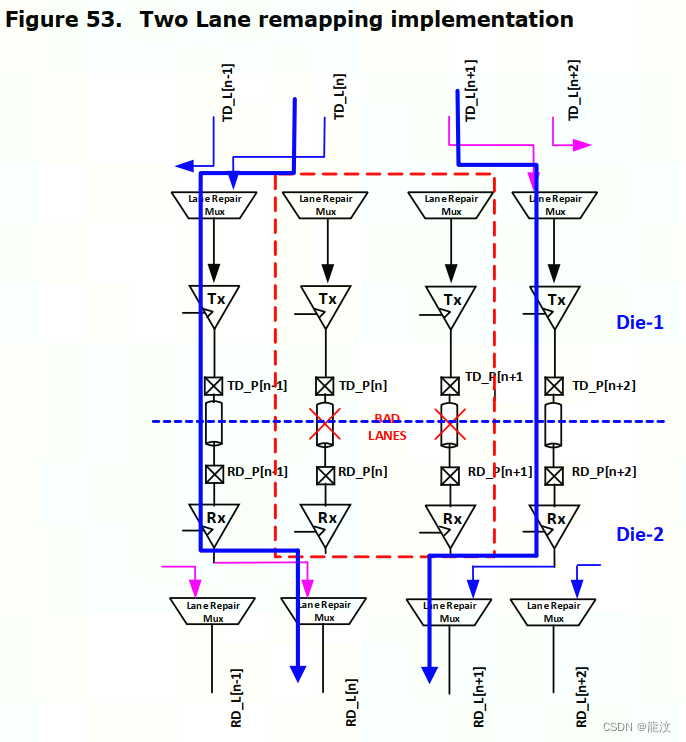

在进行数据通道重映射后,与故障物理通道相关联的发送器将处于三态状态,接收器将被禁用。用于修复的冗余通道的发送器和接收器将被启用。

图48显示了对前32个通道组进行数据通道重映射的发送端修复。为了在该组内最佳地修复任意两个通道,需要同时进行"左移"和"右移"的重映射。图49显示了用于数据通道修复的多路复用器结构的详细信息。

注意:为了清晰起见,示例修复实现仅显示了TD_P[31:0]。需要注意的是,相同的方案也适用于TD_P[63:32]。

4.3.2 Data Lane repair with Lane reversal

如果通道被反转,发送器的物理通道0(TD_P[0])将连接到接收器的物理通道N-1(RD_P[N-1])。对于高级封装模块,N为64,对于标准封装模块,N为16。

当需要进行通道反转时,通道修复映射会发生变化。换句话说,修复的通道会相应地进行调整以适应通道反转的情况。

4.3.3 Data Lane repair implementation

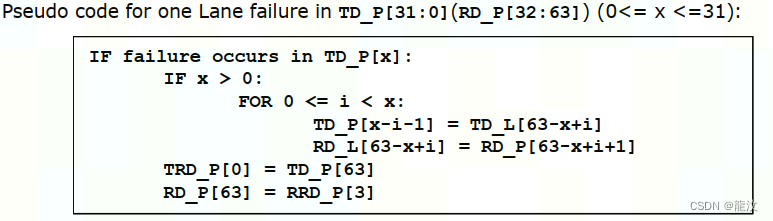

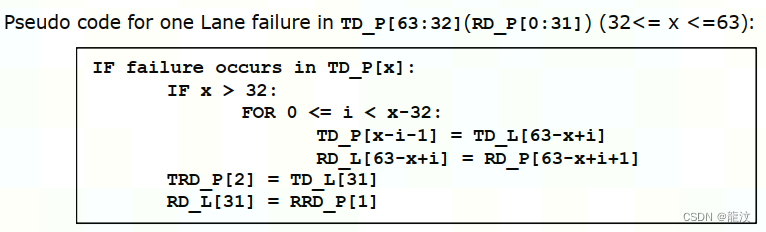

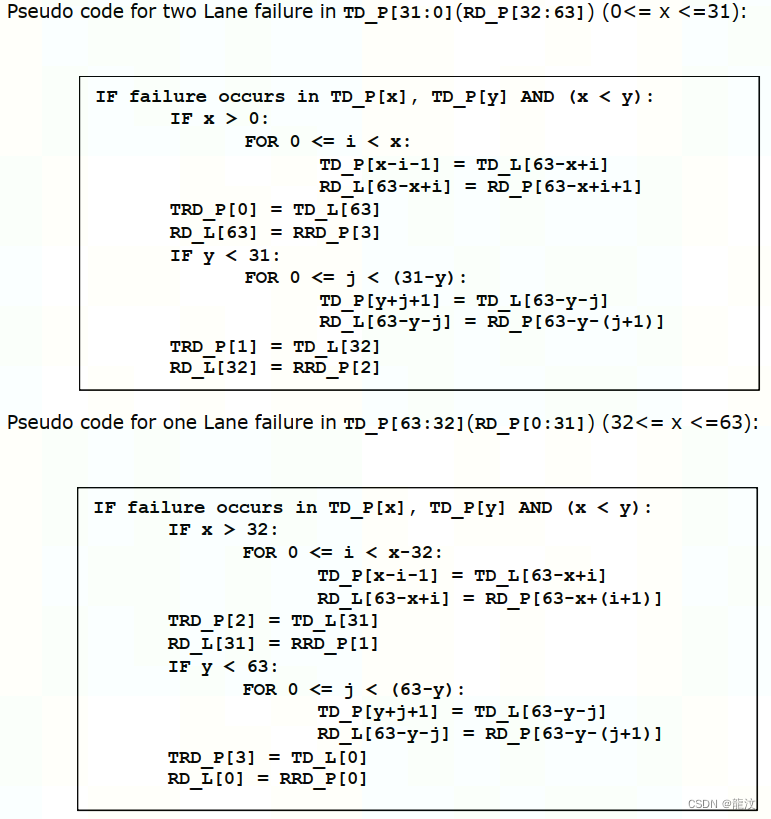

4.3.3.1 Single Lane repair

对于TD_P[31:0](RD_P[31:0]),必须使用TRD_P[0](RRD_P[0])作为冗余通道来重映射任何单个物理通道故障。

对于TD_P[63:32](RD_P[63:32]),必须使用TRD_P[2](RRD_P[2])作为冗余通道来重映射任何单个通道故障。

根据您提到的图示中的Figure 50,TD_P[29]被重映射为使用TRD_P[0]作为修复资源的方向。这意味着当TD_P[29]发生故障时,它将使用TRD_P[0]来修复。

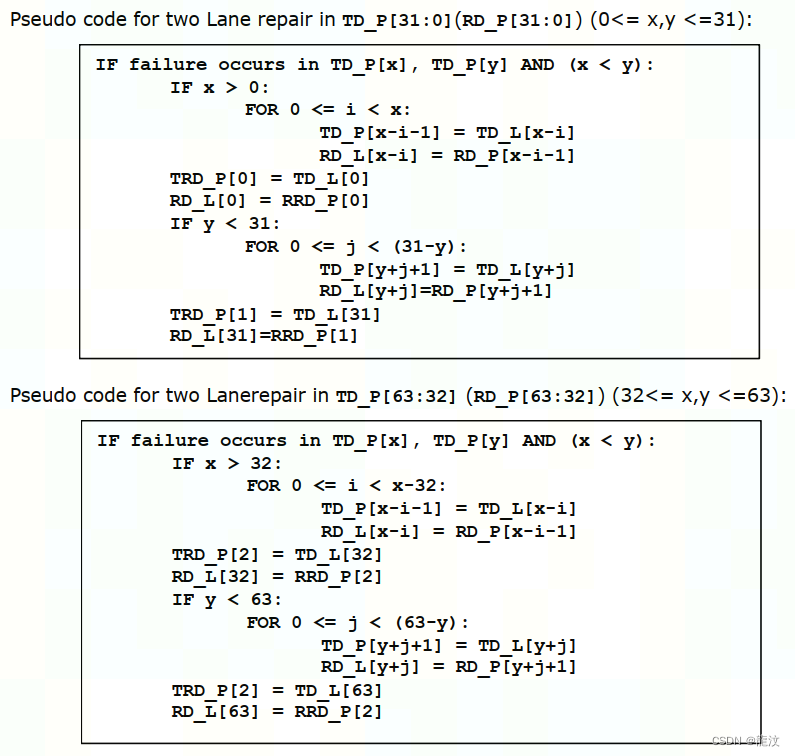

4.3.3.2 Two Lane repair

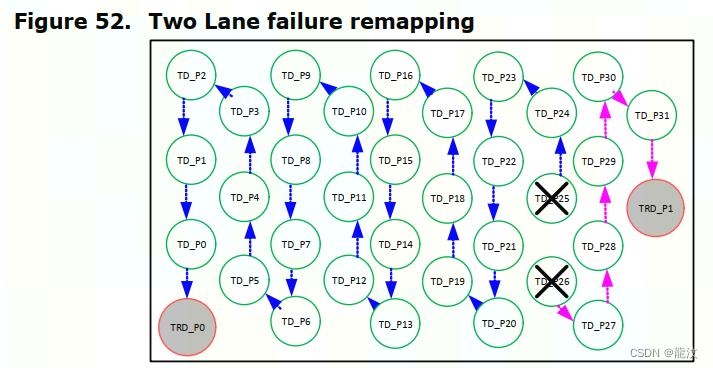

在32个通道的任意两个通道中,可以使用两个冗余通道进行修复。对于TD_P[31:0](RD_P[31:0])中的任意两个物理通道故障,较低的通道必须重映射到TRD_P[0](RRD_P[0]),而较高的通道重映射到TRD_P[1](RRD_P[1])。对于TD_P[63:32](RD_P[63:31])中的任意两个物理通道故障,较低的通道必须重映射到TRD_P[2](RRD_P[2]),而较高的通道重映射到TRD_P[3](RRD_P[3])。换句话说,每组32个通道中的任意两个通道故障都可以通过使用两个冗余通道来修复。

根据您提到的Figure 52,这是两个通道(物理通道25和26)的通道重映射的示例。而Figure 53展示了电路的实现。发送器和接收器都必须应用所需的通道重映射。

4.3.3.3 Single Lane repair with Lane reversal

为了进行修复并实现链路反转(第4.3.2节),发送端的重映射被反转以保留接收端重映射的移位顺序

4.3.3.4 Two Lane repair with Lane reversal

为了进行链路反转的修复(第4.3.2节),发送端的重映射被反转,以保持接收端重映射的移位顺序。

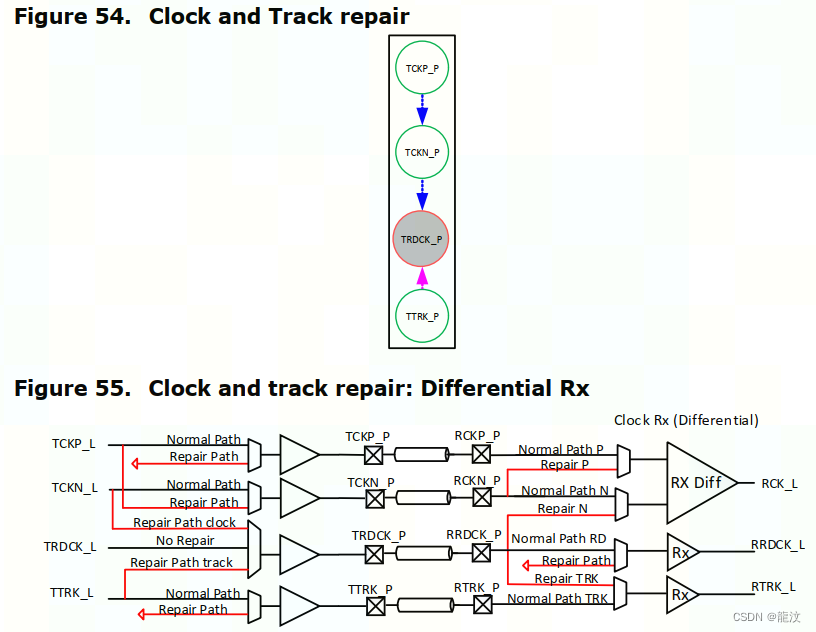

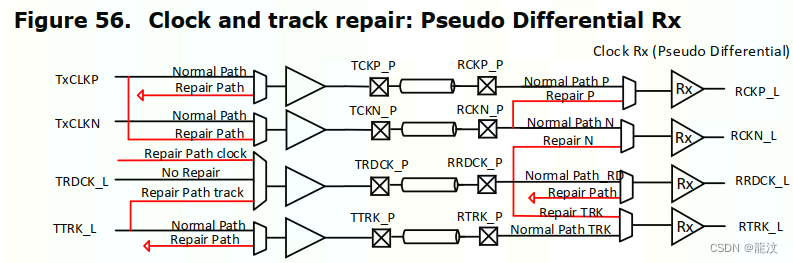

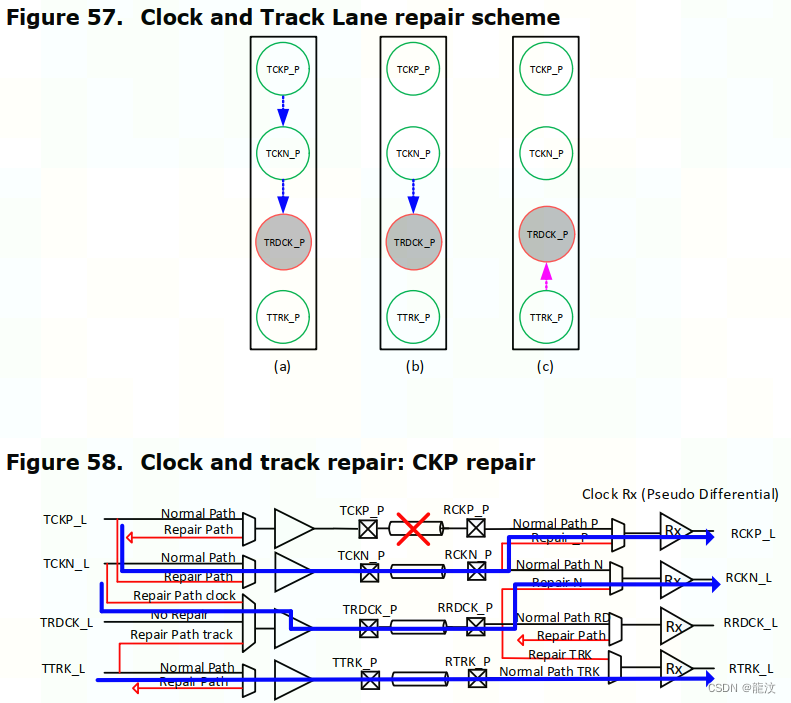

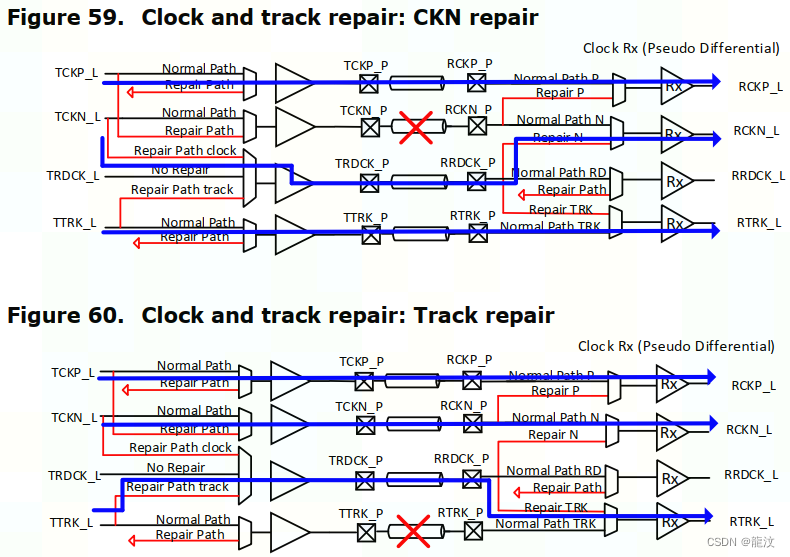

4.3.4 Clock and Track Lane remapping

该规范支持对TCKP_P/RCKP_P、TCKN_P/RCKN_P和TTRK_P/RTRK_P物理通道进行重映射以修复其中一个损坏的通道。修复方案如图54所示。时钟通道重映射允许修复时钟接收器的差分和伪差分实现中的单个通道故障。差分和伪差分时钟接收器的电路细节分别如图55和图56所示。

在通道重映射后,发送端处于三态状态。物理冗余(RRDCK_P)通道的接收端被禁用。

4.3.5 Clock and Track Lane repair implementation

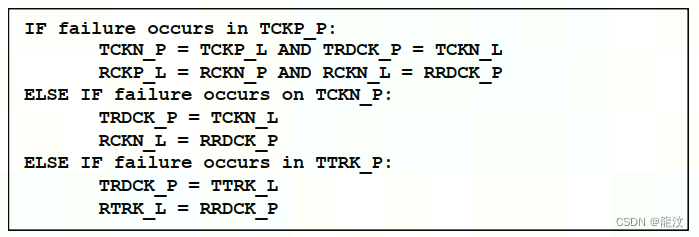

Clock和Track信号修复的伪代码。

时钟和跟踪通道重映射的实现分别如图57(a)、图57(b)和图57(c)所示。重映射实现的电路级细节如图58、图59和图60所示。

请注意,在检测阶段,CKRD通道上的发送端和接收端都是必需的,如果不用于修复,则可以处于三态状态并关闭。

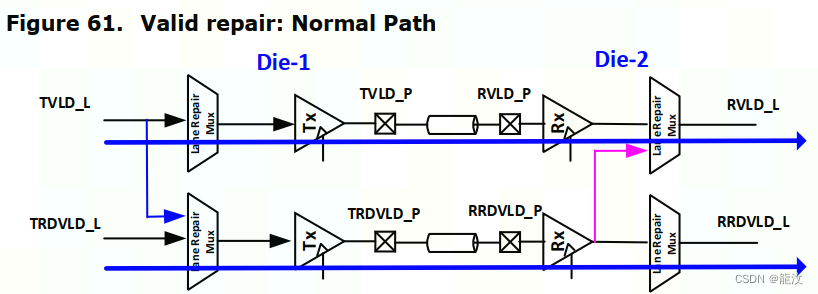

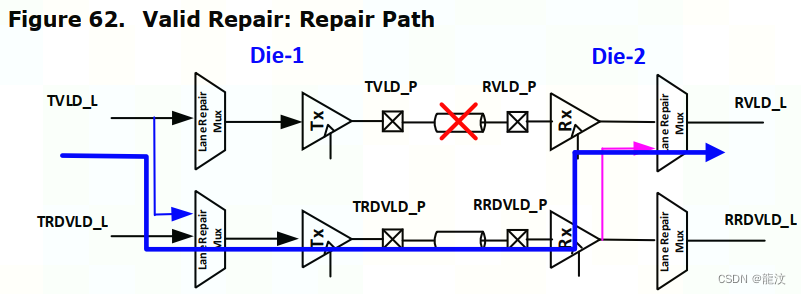

4.3.6 Valid Repair and implementation

valid信号拥有一个专用的冗余通道。如果在valid物理通道上检测到故障,将使用冗余的valid物理通道发送有效信号。valid信号的故障检测和修复是在链路初始化和训练(第4.5.3.3.4节)期间进行的。

图61显示了valid和冗余valid通道的正常路径。图62显示了valid通道故障的修复路径。

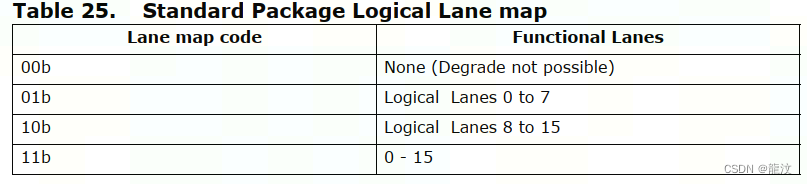

4.3.7 Width Degrade in Standard Package Interfaces

对于标准封装的x16模块,不支持通道修复,但可以通过将链路配置为x8宽度(逻辑通道0到7或逻辑通道8到15,排除故障通道)来提供对故障通道的容错能力。例如,如果逻辑通道0到7中有一个或多个故障通道,则使用逻辑通道8到15将链路配置为x8宽度。配置是在链路初始化或重新训练期间进行的,禁用通道的发送器进入高阻态,接收器被禁用。

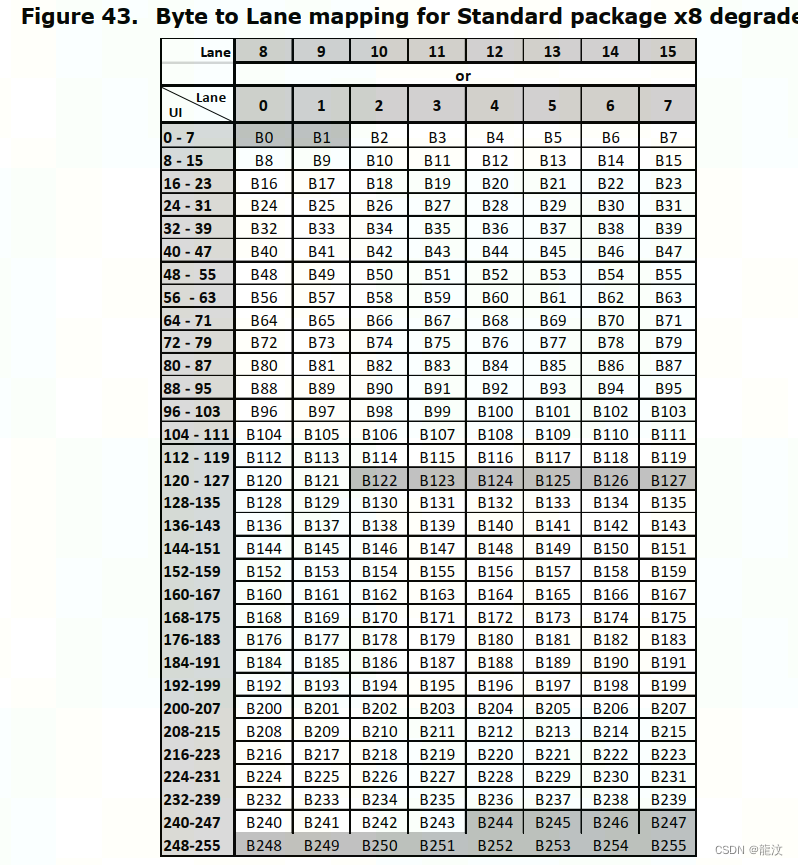

图43显示了宽度降级为x8接口的字节到通道的映射。

4.4 Data to Clock Training and Test Modes

注:辅助命令将被标识为{SB命令}。

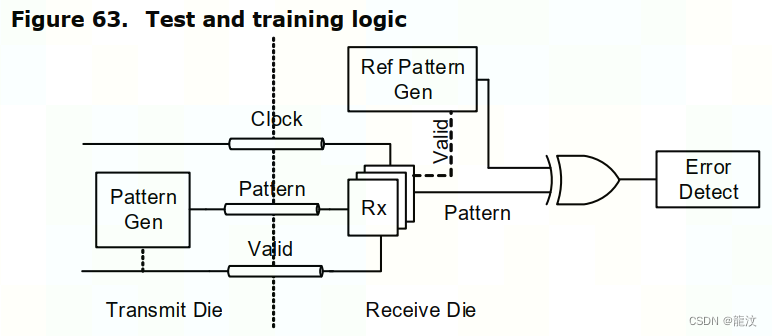

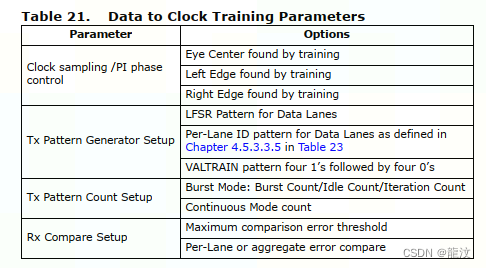

图63显示了接口训练和测试的基础设施。发送器芯片和接收器芯片实现了与第4.4.1节中描述的相同的线性反馈移位寄存器(LFSR)。从发送器发送的模式以及转发的时钟和有效信号与本地生成的参考模式进行比较。发送和接收模式生成器必须同步启动和推进。比较电路在每个单元间隔(UI)检查匹配的数据。接收到的模式与本地模式生成器预测的模式之间的任何不匹配都被检测为错误。

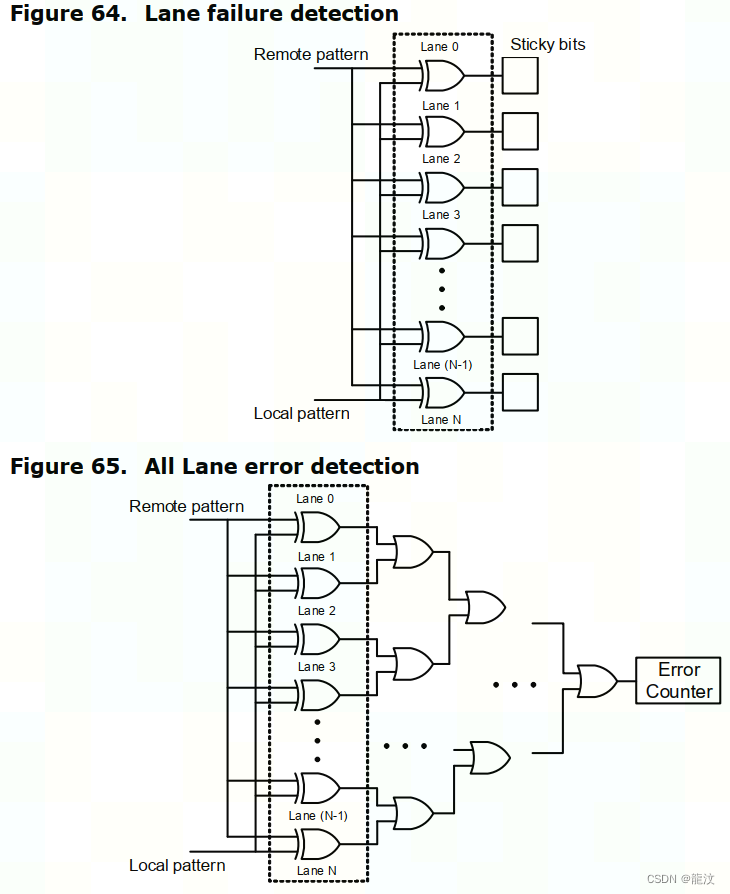

接收芯片必须实现两种类型的比较方案:

• 逐通道比较:逐通道比较用于在两个芯片之间识别故障通道。每个通道上接收到的模式与每个通道上的预期模式之间的任何超过设定阈值的不匹配都会为每个通道设置一个粘性寄存器位。一旦发现了特定通道上的模式不匹配,粘性寄存器位将在测试的剩余部分中被设置。图64说明了逐通道比较模式。该模式将指示模块内每个通道的错误(对于高级和标准封装模块分别为N = 68(64 + 4 RD)和16个通道)。可以通过辅助通道读取逐通道比较结果。

• 聚合比较:在这种模式下,模块中任何通道上每个单元间隔(UI)的模式不匹配都会累积到一个16位错误计数器中。通道错误被进行逻辑或运算,生成模块级别的错误,并按照图65所示进行计数。该方案可用于模块级别的余量和误码率(BER)测试。错误计数器可以通过辅助通道读取。

4.4.1 Scrambling and training pattern generation

线性反馈移位寄存器(LFSR)用于数据混淆和测试模式生成。

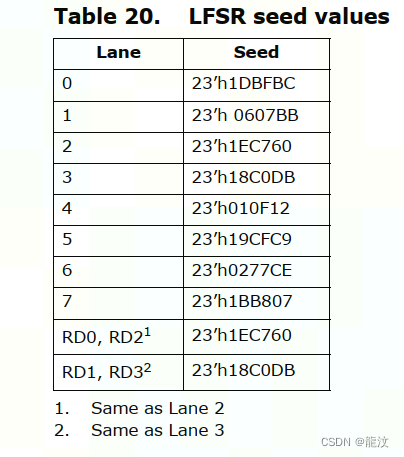

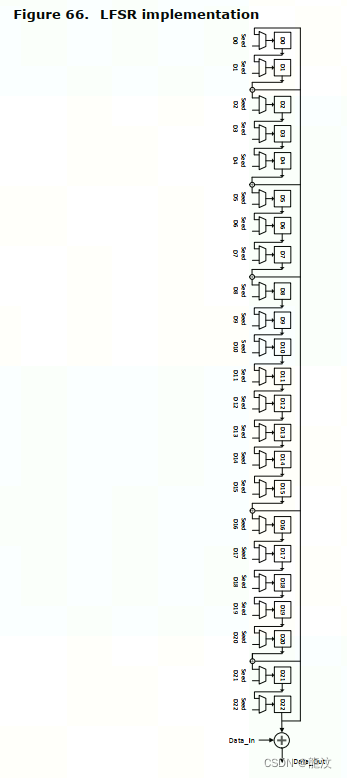

LFSR使用与PCIe相同的多项式:G(X)=X23 + X21 + X16 + X8 + X5 + X2 + 1。每个发送器可以实现一个单独的LFSR用于混淆和模式生成。每个接收器可以实现一个单独的LFSR用于解混淆和模式比较。实现如图66所示。LFSR的种子与通道相关,通道号的种子值对8取模,如表20所示。

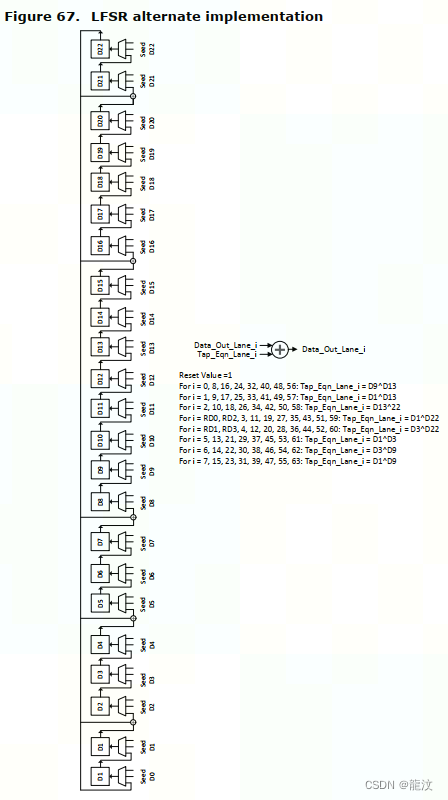

或者,实现可以选择使用不同的触发点为多个通道实现一个LFSR,如图67所示。这相当于每个通道使用不同种子的单独LFSR。

4.5 Link Initialization and Training

链路初始化和训练是在模块级别上进行描述的。本节中使用的术语定义如下:

• UCIe模块伙伴:UCIe模块伙伴是远程UCIe芯片上对应的UCIe模块,与UCIe模块相连接。例如,如果两个UCIe芯片A和B通过一个2模块的UCIe链路连接,模块0和1;UCIe芯片A的模块0(UCIe模块A0)连接到UCIe芯片B的模块1(UCIe模块B1);那么A0是B1的UCIe模块伙伴,反之亦然。

• 相位插值器(PI)在本规范中用于指代生成和选择采样时钟相位的任何方法。

• 超时:链路训练状态机中除RESET和TRAINERROR状态外的每个状态都有一个8毫秒的超时时间。对于具有子状态的状态,超时时间是每个子状态独立计算的;即,如果物理层在该状态下超过8毫秒,则它会转换到TRAINERROR状态,最终转换到RESET状态。物理层侧边通信的RDI状态转换与远程链路伙伴的握手也在8毫秒后超时。如果收到带有“Stall”编码的侧边消息,则必须重置超时计数器。

• 电气空闲在第5.12节中有描述。

在链路启动期间进行训练(即物理层从RESET状态转换出来),硬件可以尝试多次进行训练。触发链路训练的条件包括:

• 软件向UCIe链路控制中的Start UCIe Link Training位写入1b。

• 适配器在RDI上触发链路训练(RDI状态为Reset,并且状态请求中有从NOP到Active的转换)。

• 在任何侧边接收器时钟/数据对上观察到SBINIT模式(连续两个迭代的64 UI时钟模式和32 UI低电平)。

一旦硬件在实施特定次数的尝试后无法完成训练,必须将其转换为RESET状态,并等待后续的链路训练触发。如果软件触发或RDI触发的链路训练失败,或由于物理层超时而导致链路从上升到下降的转换,物理层必须在RDI上升时升级为致命错误。

4.5.1 Link Training basic operations

本节中定义了链路训练中的一些基本操作。这些操作将用于main band初始化、训练和调整。

4.5.1.1 Transmitter initiated Data to Clock point test

在此模式下,发射器在模块的所有通道上以单个PI相位启动数据到时钟的训练。对于UCIe链路的每个UCIe模块,此测试的步骤序列如下:

-

UCIe模块设置发射器参数(在表21中显示),向其UCIe模块伙伴发送侧边消息{Start Tx Init D to C point test req}并等待响应。该消息的数据字段包括所需的参数,如表21所示。UCIe模块伙伴上的接收器必须启用模式比较电路,将传入的主频带数据与本地生成的预期模式进行比较。一旦设置好接收器的数据到时钟训练参数,UCIe模块伙伴将以{Start Tx Init D to C point test resp}的形式响应。

-

UCIe模块重置其主频带发射器上的LFSR(扰码器),并发送侧边消息{LFSR clear error req}。UCIe模块伙伴重置其主频带接收器上的LFSR,并清除任何先前的比较结果,并以{LFSR clear error resp}侧边消息进行响应。

-

UCIe模块在其主频带发射器上发送选定的模式(通过“Tx Pattern Generator Setup”选择)进行指定数量的周期(通过“Pattern Count Setup”设置)。

-

UCIe模块伙伴根据“Rx compare setup”在每个UI期间对其接收器进行模式传输的比较,并记录结果。

-

UCIe模块通过发送{D to C results Req}侧边消息向其UCIe模块伙伴请求步骤4中记录的结果。UCIe模块伙伴停止其主频带接收器上的比较,并以记录的结果{D to C results log}侧边消息进行响应。

-

UCIe模块停止在其发射器上发送模式,并发送{End Tx Init D to C point test req}侧边消息,UCIe模块伙伴以{End Tx Init D to C point test resp}形式响应。当一个UCIe模块发送并接收到{End Tx Init D to C point test resp}时,它进入电气空闲状态。

4.5.1.2 Transmitter initiated Data to Clock eye width sweep

在此模式下,发射器在模块的所有通道上启动数据到时钟的训练,并扫描采样PI相位。此模式还可用于检查系统的边际。此测试的步骤序列如下:

-

UCIe模块设置发射器参数(在表21中显示),向其UCIe模块伙伴发送侧边消息{Start Tx Init D to C eye sweep req}并等待响应。该消息的数据字段包括所需的参数,如表21所示。UCIe模块伙伴上的接收器必须启用模式比较电路,将传入的主频带数据与本地生成的预期模式进行比较。一旦设置好接收器的数据到时钟训练参数,UCIe模块伙伴将以侧边消息{Start Tx Init D to C eye sweep resp}的形式响应。

-

UCIe模块重置其主频带发射器上的LFSR(扰码器),并发送侧边消息{LFSR clear error req}。UCIe模块伙伴重置其主频带接收器上的LFSR,并清除任何先前的比较结果,并以{LFSR clear error resp}侧边消息进行响应。

-

UCIe模块在其主频带发射器上发送选定的模式(通过“Tx Pattern Generator Setup”选择)进行指定数量的周期(通过“Pattern Count Setup”设置)。

-

UCIe模块伙伴根据“Rx compare setup”在每个UI期间对其接收器进行模式传输的比较,并记录结果。

-

UCIe模块通过发送{D to C results Req}侧边消息向其UCIe模块伙伴请求步骤4中记录的结果。UCIe模块伙伴停止其主频带接收器上的比较,并以记录的结果{D to C results log}侧边消息进行响应。

-

UCIe模块在其转发时钟发射器上扫描PI相位,每次重复步骤2到步骤5,以找到通过的PI相位范围。扫描步骤和范围是特定实现的。

-

UCIe模块停止在其发射器上发送模式,并发送{End Tx Init D to C eye sweep req}侧边消息,UCIe模块伙伴以{End Tx Init D to C eye sweep resp}形式响应。当一个UCIe模块发送并接收到{End Tx Init D to C point eye sweep resp}时,它进入电气空闲状态。

4.5.1.3 Receiver initiated Data to Clock point training

在此模式下,接收器在模块的所有通道上以相位插值器(PI)的单个相位启动数据到时钟的训练。此测试的步骤序列如下:

-

UCIe模块启用模式比较电路,将传入的主频带数据与本地生成的预期模式进行比较,设置接收器参数(在表21中显示),向其UCIe模块伙伴发送侧边消息{Start Rx Init D to C point test req}并等待响应。该消息的数据字段包括所需的参数,如表21所示。UCIe模块伙伴上的发射器必须处于空闲状态。一旦设置好发射器的数据到时钟训练参数,UCIe模块伙伴将以侧边消息{Start Rx Init D to C point test resp}的形式响应。

-

UCIe模块伙伴重置其主频带发射器上的LFSR(扰码器),并发送侧边消息{LFSR clear error req}。UCIe模块重置其主频带接收器上的LFSR,并清除任何先前的比较结果,并以{LFSR clear error resp}侧边消息进行响应。

-

UCIe模块伙伴在其主频带发射器上发送选定的模式(通过“Tx Pattern Generator Setup”选择)进行指定数量的周期(通过“Pattern Count Setup”设置)。

-

UCIe模块在其主频带接收器上根据“Rx compare setup”在每个UI期间对模式传输进行比较,并记录结果。

-

UCIe模块伙伴在模式计数完成后发送侧边消息{Rx Init D to C Tx count done req}。UCIe模块停止比较并以侧边消息{Rx Init D to C Tx count done resp}进行响应。UCIe模块现在可以使用记录的数据进行其接收器通道的训练。

-

UCIe模块发送{End Rx Init D to C point test req}侧边消息,UCIe模块伙伴以{End Rx init D to C point test resp}侧边消息进行响应。然后,UCIe模块上的发射器和接收器进入空闲状态。

4.5.1.4 Receiver initiated Data to Clock Eye Width sweep training

在此模式下,接收器在模块的所有通道上以相位插值器(PI)的单个相位启动数据到时钟的训练。此测试的步骤序列如下:

-

UCIe模块启用模式比较电路,将传入的主频带数据与本地生成的预期模式进行比较,设置接收器参数(在表21中显示),向其UCIe模块伙伴发送侧边消息{Start Rx Init D to C eye sweep req}并等待响应。该消息的数据字段包括所需的参数,如表21所示。UCIe模块伙伴上的发射器必须处于空闲状态。一旦设置好发射器的数据到时钟训练参数,UCIe模块伙伴将以侧边消息{Start Rx Init D to C eye sweep resp}的形式响应。

-

UCIe模块伙伴重置其主频带发射器上的LFSR(扰码器),并发送侧边消息{LFSR clear error req}。UCIe模块重置其主频带接收器上的LFSR,并清除任何先前的比较结果,并以{LFSR clear error resp}侧边消息进行响应。

-

UCIe模块伙伴在其主频带发射器上按照“Tx Pattern Generator Setup”选择的模式进行指定数量的周期(通过“Pattern Count Setup”设置)。

-

UCIe模块在其主频带接收器上根据“Rx compare setup”在每个UI期间对模式传输进行比较,并记录结果。

-

UCIe模块伙伴通过发送{Rx Init D to C results Req}侧边消息请求UCIe模块记录的数据到时钟测试结果。UCIe模块以侧边消息{Rx Init D to C results log}的形式响应,提供其主频带接收器的记录结果。UCIe模块伙伴可以根据结果记录确定PI相位的模式比较是否通过或失败。

-

UCIe模块伙伴在其转发时钟上扫描PI相位,每次重复步骤2到步骤5,以找到通过的PI相位范围。扫描模式和范围是特定实现的。

-

UCIe模块伙伴发送带有其主频带发射器结果的{Rx Init D to C sweep done with results}侧边消息。UCIe模块可以使用扫描结果来进行其主频带接收器的操作。

-

UCIe模块发送{End Rx Init D to C eye sweep req}侧边消息,UCIe模块伙伴以{End Rx init D to C eye sweep resp}侧边消息进行响应。然后,UCIe模块上的发射器和接收器进入空闲状态。

4.5.2 Link Training with Retimer

根据图68所示的初始化流程与UCIe Retimer的说明如下:外部连接和UCIe连接(UCIe芯片到UCIe Retimer)可以独立地建立连接。当UCIe连接训练到本地数据速率和数据宽度时,会通过外部连接请求远程UCIe信息。如果存在数据速率和数据宽度的差异,允许每个UCIe连接重新进行训练以实现速率(数据速率)和宽度匹配(如果UCIe Retimer需要这样做以进行操作,则必须从LinkSpeed状态启动重新训练)。在初始连接建立或重新训练期间,这可能会发生多次。一旦UCIe Retimer确定UCIe连接配置适合与远程Retimer伙伴成功运行,UCIe连接通过协议级的连接初始化(LINKINIT)进入ACTIVE状态。

4.5.3 Link Training State Machine

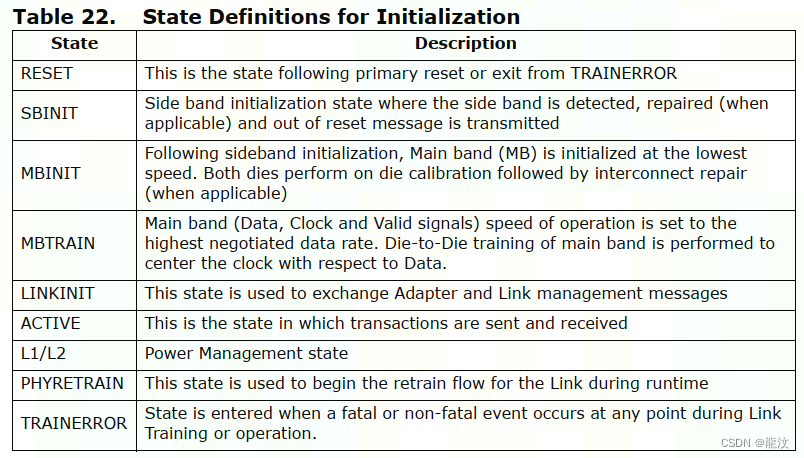

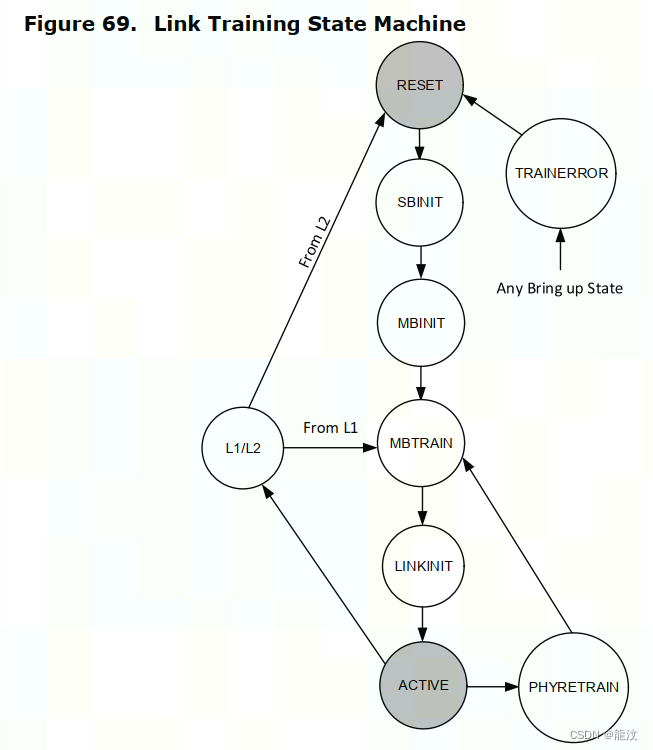

Figure 69显示了一个高级的初始化流程。表22中显示了每个状态的高级描述。每个状态中执行的详细操作在后续章节中进行描述。

4.5.3.1 RESET

在每次进入RESET状态时,物理层必须至少保持RESET状态4毫秒,以使PLL等稳定下来。退出RESET状态的最低条件包括:

• 电源稳定

• 边带时钟可用且运行在800 MHz

• 主带和Die to Die适配器时钟稳定且可用

• 主带时钟设置为最慢的IO数据速率(对于4 GT/s,为2 GHz)

• 本地SoC/固件不会将物理层保持在RESET状态

• 触发链路训练。这些触发条件在第4.5节的开头进行了定义。

4.5.3.2 Sideband Initialization (SBINIT)

在这个状态下,边带(SB)接口被初始化和修复(如果适用)。UCIe模块的主带(MB)发射器被三态化,MB接收器被允许禁用。SB初始化过程以800 MT/s和800 MHz边带时钟进行。高级封装接口具有冗余的SB时钟和SB数据通道(DATASBRD、CKSBRD),除了DATASB和CKSB。高级封装接口的SBINIT序列,其中可能需要进行互连修复,如下所示:

- UCIe模块必须开始并继续发送64 UI时钟模式和32 UI低电平的迭代,同时在两个边带数据发射器(TXDATASB和TXDATASBRD)上发送脉冲。UCIe模块在进行数据传输时必须在TXCKSB和TXCKSBRD上发送脉冲,否则将进行门控。

- UCIe模块的合作方必须使用两个边带时钟对其边带接收器上的每个传入数据模式进行采样(这形成了四个接收器/时钟组合)。

- 如果在第1步中的两个连续迭代中检测到边带数据时钟接收器组合,则认为侦测成功。

- 如果UCIe模块的合作方在其边带数据时钟接收器组合中至少成功检测到一次该模式,则在发送四个更多的64 UI时钟模式和32 UI低电平迭代后,必须停止在其边带发射器上发送数据和时钟。这将允许UCIe模块和UCIe模块合作方在RESET状态后的任何时间差异。现在,UCIe模块上的边带发射器和接收器必须被启用以发送和接收边带消息。

- 如果在其边带接收器上没有检测到该模式,则UCIe模块必须继续在其边带发射器上发送该模式1毫秒,并在8毫秒内空闲1毫秒。UCIe模块的边带接收器在此期间必须保持启用状态。8毫秒后超时,UCIe模块进入TRAINERROR状态。

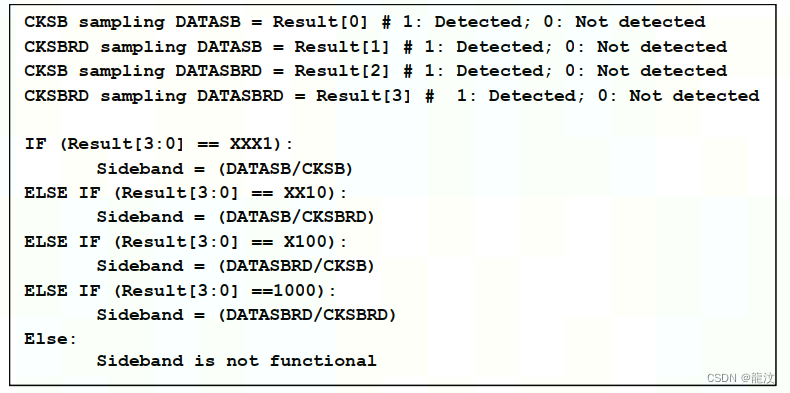

- 如果在多个边带数据/时钟组合上检测成功,则设备可以根据优先顺序选择一个组合。边带分配的伪代码如下所示:

- 如果UCIe模块启用了边带以发送和接收边带消息(第4步),UCIe模块必须开始并继续在TXDATASB和TXDATASBRD上发送{SBINIT Out of Reset}边带消息,同时在发送TXCKSB和TXCKSBRD时发送脉冲,直到在其边带接收器上检测到相同的消息或超时时间达到8毫秒。

- 如果在其边带接收器上成功检测到{SBINIT Out of Reset}边带消息,则UCIe模块停止发送边带消息。在发送任何进一步的边带消息之前,UCIe模块和UCIe模块合作方必须根据{SBINIT Out of Reset}边带消息中包含的信息应用边带数据/时钟分配(称为功能边带)。

- 任何进一步的边带消息必须在功能边带上发送和接收。现在可以执行任何边带消息交换。

- UCIe模块发送边带消息{SBINIT done req}并等待响应。如果成功接收到该消息,UCIe模块合作方将以{SBINIT done resp}作为响应。当UCIe模块发送并接收到{SBINIT done resp}时,必须退出到MBINIT状态。

下一个状态是主带初始化(MBINIT),如果边带消息交换成功。

对于不支持互连通道冗余和修复的标准封装接口的SBINIT序列如下所示:

- UCIe模块必须开始并继续在其边带发射器(TXDATASB)上发送64 UI时钟模式和32 UI低电平的迭代。UCIe模块在进行数据传输时必须在其边带时钟(TXCKSB)上发送脉冲,否则将进行门控。

- UCIe模块合作方必须使用传入的时钟对传入的数据模式进行采样。

- 如果在第1步中的两个连续迭代中检测到边带模式,则认为边带模式检测成功。

- 如果UCIe模块成功检测到该模式,则在发送四个更多的第1步中的模式迭代后,停止在其边带发射器上发送数据和时钟。这将允许UCIe模块之间的任何时间差异。现在,UCIe模块的边带发射器和接收器必须被启用以发送和接收边带消息。

- 如果在其边带接收器上没有检测到该模式,则UCIe模块必须继续在其发射器上发送该模式1毫秒,并在8毫秒内空闲1毫秒。在此期间,边带接收器必须保持启用状态。8毫秒后超时,UCIe模块必须退出到TRAINERROR状态。如果在任何时候成功检测到模式(如第3步所述),UCIe模块将启用边带消息传输(如第4步所述)并开始发送边带消息(第6步)。

- 一旦边带检测成功(第5步),UCIe模块必须开始并继续在TXDATASB上发送{SBINIT Out of Reset}边带消息,同时发送TXCKSB,直到在其边带接收器上检测到相同的消息或超时发生。

- 如果成功检测到{SBINIT Out of Reset}边带消息,则UCIe模块必须停止发送该消息。现在可以执行任何物理层边带消息交换。

- UCIe模块必须发送边带消息{SBINIT done req}。如果成功接收到该消息,每个UCIe模块合作方都将以{SBINIT done resp}作为响应。当UCIe模块发送并接收到{SBINIT done resp}时,必须退出到MBINIT状态。

下一个状态是主带初始化(MBINIT),如果边带消息交换成功。

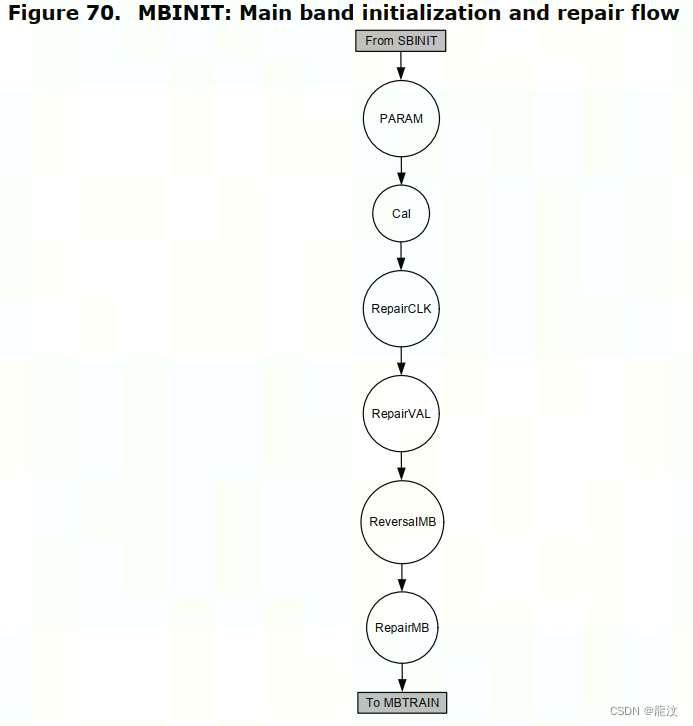

4.5.3.3 MBINIT

在这个状态下,主带(MB)接口被初始化,并进行修复或降级(如果适用)。主带上的数据速率设置为最低支持的数据速率(4 GT/s)。

对于高级封装接口,可能需要进行互连修复。MBINIT的子状态允许检测和修复数据、时钟、跟踪和有效通道。对于标准封装接口,不需要通道修复。子状态用于在最低数据速率和宽度下检查功能,并在需要时进行降级。

4.5.3.3.1 MBINIT.PARAM

在这个状态下,用于执行设置最大协商速度和其他物理层设置所需的参数交换。以下参数与UCIe模块合作方进行交换:

- "电压摆幅":这个五位值表示向UCIe模块合作方发送的发射器电压摆幅。UCIe模块合作方必须使用该值和其接收器终端信息来设置其接收器的参考电压(Vref)。在{MBINIT.PARAM configuration resp}中的相应位被保留。

- "最大数据速率":这个四位值表示向UCIe模块合作方发送的最大支持的数据速率。该值必须考虑到数据速率的所有要求特性(误码率、CRC/重试、正交时钟相位支持等)。UCIe模块合作方必须将此值与其支持的最大数据速率进行比较,并在{MBINIT.PARAM configuration resp}中以最大公共数据速率编码进行响应。例如,如果一个UCIe模块支持8 GT/s,而UCIe模块合作方宣传16 GT/s,UCIe模块必须选择8 GT/s并将其作为响应发送回去。

- "时钟模式":这个一位值表示UCIe模块对UCIe模块合作方请求脉冲时钟或连续时钟。UCIe模块合作方必须使用此信息来设置其时钟发射器的时钟模式。{MBINIT.PARAM configuration resp}必须反映相同的值。

- "时钟相位":这个一位值表示UCIe模块对UCIe模块合作方在UCIe模块的转发时钟上请求时钟相位支持。只有在所宣传的最大数据速率允许时才应设置为1b(参考表35)。如果请求了此项且操作数据速率允许,则{MBINIT.PARAM configuration resp}中的相应位必须设置为1b。

- "模块ID":UCIe模块发送其"模块ID"。如果处于多模块配置中,UCIe模块合作方可以使用此信息进行字节映射、模块启用/禁用等。在{MBINIT.PARAM configuration resp}中的相应位被保留。

以下是参数交换的顺序: - UCIe模块发送边带消息{MBINIT.PARAM configuration req}以与UCIe模块合作方交换参数。

- 一旦接收到{MBINIT.PARAM configuration req},UCIe模块合作方解析并以{MBINIT.PARAM configuration resp}边带消息进行响应。

4.5.3.3.2 MBINIT. CAL

这个状态用于执行任何需要的校准(例如:发射器占空比校正、接收器偏移和Vref校准)。这个状态对于高级封装接口和标准封装接口都是通用的。

- UCIe模块在这个状态下必须将其所有发射器引脚设置为三态,并可以执行任何所需的发射器和接收器校准。

- UCIe模块必须发送侧带消息{MBINIT.CAL Done req}并等待响应。如果成功接收到该消息,UCIe模块合作方将以{MBINIT.CAL Done resp}的形式作出响应。一旦UCIe模块发送并接收到{MBINIT.CAL Done resp},它必须退出到MBINIT.REPAIRCLK状态。

4.5.3.3.3 MBINIT.REPAIRCLK

该子状态用于检测和修复(如有必要)用于高级封装接口的时钟和轨道通道,并用于标准封装接口的时钟和轨道通道的功能检查。以下是高级封装接口的顺序:

时钟修复映射在第4.3节中描述。每个时钟、轨道和时钟冗余物理通道(TCKP_P/RCKP_P、TCKN_P/RCKN_P、TTRK_P/RTRK_P和TCKRD_P/RCKRD_P)都会独立检查,以检测可能的电气断路或电气短路。需要使用单端时钟接收器或独立的检测机制来确保时钟修复。UCIe模块必须启用时钟、轨道和冗余时钟通道上的发射器和接收器。其他所有发射器可以保持三态。

- UCIe模块发送侧带消息{MBINIT.REPAIRCLK init req}并等待响应。当UCIe模块的合作伙伴准备好在RCKP_L、RCKN_L、RTRK_L、RCKRD_L上接收模式时,会以{MBINIT.REPAIRCLK init resp}进行响应。

- UCIe模块现在必须在其TCKP_P上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。(TCKN_P、TTRK_L和TCKRD_L处于三态)。时钟修复模式不能被打乱。

- UCIe模块的合作伙伴检测到RCKP_L、RCKN_L、RTRK_L和RCKRD_L上的该模式。如果至少连续检测到16个时钟修复模式的迭代,则认为检测成功。UCIe模块的合作伙伴记录了RCKP_L、RCKN_L、RTRK_L和RCKRD_L的检测结果。

- UCIe模块在完成模式传输后,发送{MBINIT.REPAIRCLK result req}侧带消息以获取记录的结果,并等待响应。

- UCIe模块的合作伙伴通过侧带消息{MBINIT.REPAIRCLK result resp}以RCKP_L、RCKN_L、RTRK_L和RCKRD_L的日志结果进行响应。如果仅在RCKP_L上检测成功,而在RCKN_L、RTRK_L和RCKRD_L上没有成功检测到,则不需要修复。如果在RCKP_L、RCKN_L、RTRK_L和RCKRD_L中的任意两个通道上检测成功,则暗示存在电气短路。如果在RCKP_L、RCKN_L、RTRK_L和RCKRD_L的所有通道上都没有成功检测到,则需要对物理通道TCKP_P/RCKP_P进行修复。

- 在接收到{MBINIT.REPAIRCLK result resp}侧带消息后,UCIe模块发送侧带消息{MBINIT.REPAIRCLK init req}并等待响应。当UCIe模块的合作伙伴准备好在RCKP_L、RCKN_L、RTRK_L和RCKRD_L上接收模式时,会以{MBINIT.REPAIRCLK init resp}进行响应。

- 在接收到{MBINIT.REPAIRCLK init resp}侧带消息后,UCIe模块必须仅在其TCKN_L上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。(TCKP_L、TTRK_L和TRDCK_L处于三态状态)

- UCIe模块的合作伙伴在所有RCKP_L、RCKN_L、RTRK_L和RRDCK_L上检测到该模式。如果至少连续检测到16个时钟修复模式周期,则认为检测成功。UCIe模块的合作伙伴记录了RCKP_L、RCKN_L、RTRK_L和RRDCK_L的检测结果。

- UCIe模块在完成模式传输后,发送{MBINIT.REPAIRCLK result req}侧带消息以获取记录的结果。

- 在接收到该消息后,UCIe模块的合作伙伴通过{MBINIT.REPAIRCLK result resp}侧带消息响应,并附带RCKP_L、RCKN_L、RTRK_L和RRDCK_L的记录结果。如果仅在RCKN_L上检测成功,而在RCKP_L、RTRK_L和RRDCK_L上没有成功检测到,则不需要修复。如果在RCKN_L、RCKP_L、RTRK_L和RRDCK_L中的任意两个通道上检测成功,则暗示存在电气短路。如果在RCKP_L、RCKN_L、RTRK_L和RRDCK_L的任何通道上都没有成功检测到,则需要对物理通道TCKN_P/RCKN_P进行修复。

- 在接收到{MBINIT.REPAIRCLK result resp}侧带消息后,UCIe模块发送侧带消息{MBINIT.REPAIRCLK init req}。当UCIe模块的合作伙伴准备好在RCKP_L、RCKN_L、RTRK_L和RRDCK_L上接收模式时,会以{MBINIT.REPAIRCLK init resp}进行响应。

- 在接收到{MBINIT.REPAIRCLK init resp}侧带消息后,UCIe模块仅在TRDCK_L上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。 (TCKP_L、TTRK_L和TCKN_L处于三态状态)

- UCIe模块的合作伙伴在所有RCKP_L、RCKN_L、RTRK_L和RRDCK_L上检测到该模式。如果至少连续检测到16个时钟修复模式周期,则认为检测成功。UCIe模块的合作伙伴记录了RCKP_L、RCKN_L、RTRK_L和RRDCK_L的检测结果。

- UCIe模块在完成模式传输后,发送{MBINIT.REPAIRCLK result req}侧带消息以获取记录的结果。

- 在接收到该消息后,UCIe模块的合作伙伴通过{MBINIT.REPAIRCLK result resp}侧带消息响应,并附带RCKP_L、RCKN_L、RTRK_L和RRDCK_L的记录结果。如果仅在RRDCK_L上检测成功,而在RCKP_L、RTRK_L和RCKN_L上没有成功检测到,则不需要修复。如果在RCKN_L、RCKP_L、RTRK_L和RRDCK_L中的任意两个通道上检测成功,则暗示存在电气短路。如果在RCKP_L、RCKN_L、RTRK_L和RRDCK_L的任何通道上都没有成功检测到,则物理通道TCKRD_P/RCKRD_P不可用作修复资源。

- 在接收到{MBINIT.REPAIRCLK结果响应}边带消息后,UCIe模块发送边带消息{MBINIT.REPAIRCLK初始化请求}并等待响应。当UCIe模块的合作伙伴准备好在RCKP_L、RCKN_L、RTRK_L和RRDCK_L上接收模式时,它会响应{MBINIT.REPAIRCLK初始化响应}。

- 在接收到{MBINIT.REPAIRCLK初始化响应}边带消息后,UCIe模块仅在TTRK_L上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。此时,TCKP_L、TCKN_L和TRDCK_L处于三态。

- UCIe模块的合作伙伴在所有的RCKP_L、RCKN_L、RTRK_L和RRDCK_L上检测到这个模式。如果至少检测到16个连续的时钟修复模式周期,就认为检测成功。UCIe模块的合作伙伴记录RCKP_L、RCKN_L、RTRK_L和RRDCK_L的检测结果。

- UCIe模块在完成模式传输后发送{MBINIT.REPAIRCLK结果请求}边带消息,以获取记录的结果,并等待响应。

- UCIe模块的合作伙伴停止比较,并使用记录的结果回复{MBINIT.REPAIRCLK结果响应}边带消息,其中包含RCKP_L、RCKN_L、RTRK_L和RRDCK_L的记录结果。如果仅在RTRK_L上检测成功而在RCKP_L、RCKN_L和RRDCK_L上没有检测成功,则不需要进行修复。如果在RCKN_L、RCKP_L、RTRK_L和RRDCK_L中的任意两个上检测成功,则暗示存在电短路。如果在RCKP_L、RCKN_L、RTRK_L和RRDCK_L中的任何一个上都没有检测成功,则需要修复物理通道TTRK_P/RTRK_P。

- 如果需要修复,UCIe模块将在其时钟/跟踪发射器上应用修复,并发送包含修复信息(包括不修复和无法修复)的边带消息{MBINIT.REPAIRCLK应用修复请求}。UCIe模块的合作伙伴应用修复并发送边带消息{MBINIT.REPAIRCLK应用修复响应}。如果边带无法修复(如果需要在RCKP_L、RCKN_L和RRDCK_L中的任意两个上进行修复,或者检测到电短路,则无法修复互连),则UCIe模块和UCIe模块的合作伙伴在执行TRAINERROR握手后必须退出到TRAINERROR(第4.5.3.8节)。

- 如果应用了修复,UCIe模块必须通过应用时钟修复模式并在接收器上进行检查来检查修复的成功与否。

a. UCIe模块发送边带消息{MBINIT.REPAIRCLK检查修复初始化请求}以启动检查修复,并等待响应。UCIe模块的合作伙伴使用边带消息{MBINIT.REPAIRCLK检查修复初始化响应}进行响应,并准备接收和检查时钟修复模式。

b. 在接收到{MBINIT.REPAIRCLK检查修复初始化响应}边带消息后,UCIe模块在TCKP_L上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。UCIe模块的合作伙伴在RCKN_L、RCKP_L和RTRK_L上检测到这个模式。如果至少检测到16个连续的时钟修复模式周期,就认为检测成功。UCIe模块使用边带消息{MBINIT.REPAIRCLK检查结果请求}请求检查结果,UCIe模块的合作伙伴使用边带消息{MBINIT.REPAIRCLK检查结果响应}进行响应。如果仅在RCKP_L上检测到模式,则修复被认为是成功的。如果修复不成功,则UCIe模块和UCIe模块的合作伙伴在执行TRAINERROR握手后必须退出到TRAINERROR(第4.5.3.8节)。

c. 步骤a和步骤b针对TCKP_L和TTRK_L重复。 - 如果修复成功或不需要修复,UCIe模块发送{MBINIT.RepairCLK完成请求}边带消息,UCIe模块的合作伙伴使用{MBINIT.RepairCLK完成响应}边带消息进行响应。当UCIe模块发送和接收到{MBINIT.RepairCLK完成响应}后,必须退出到REPAIRVAL。

对于标准封装接口,时钟和轨道通道在最低数据速率下进行功能操作检查。具体步骤如下:

- UCIe模块发送侧带消息{MBINIT.REPAIRCLK init req}并等待响应。当准备好在RCKP_L、RCKN_L和RTRK_L上接收模式时,UCIe模块的合作伙伴会以{MBINIT.REPAIRCLK init resp}进行响应。在接收到侧带消息{MBINIT.REPAIRCLK init resp}后,UCIe模块在TCKP_L、TCKN_L和TTRK_L上发送128个时钟修复模式迭代(16个时钟周期后跟8个低电平周期)。时钟修复模式不能进行混淆。

- UCIe模块的合作伙伴在RCKP_L、RCKN_L和RTRK_L上检测到该模式。如果至少连续检测到16个时钟修复模式周期,则认为检测成功。UCIe模块的合作伙伴记录了RCKP_L、RCKN_L和RTRK_L的检测结果。

- 在完成模式传输后,UCIe模块发送{MBINIT.REPAIRCLK result req}侧带消息以获取记录的结果。

- UCIe模块的合作伙伴停止比较,并以{MBINIT.REPAIRCLK result resp}侧带消息响应,附带RCKP_L、RCKN_L和RTRK_L的记录结果。

- 如果在RCKP_L、RCKN_L和RTRK_L中的任何一个通道上都没有成功检测到,则UCIe模块和UCIe模块的合作伙伴必须在执行TRAINERROR握手后退出到TRAINERROR状态。

- 如果检测成功,UCIe模块发送{MBINIT.RepairCLK done req}侧带消息,UCIe模块的合作伙伴以{MBINIT.RepairCLK done resp}侧带消息响应。当UCIe模块发送并接收到侧带消息{MBINIT.RepairCLK done resp}后,它必须退出到REPAIRVAL状态。

4.5.3.3.4 MBINIT.REPAIRVAL

UCIe模块将时钟相位设置在其主通道发送器的数据UI中心。UCIe模块的合作伙伴必须使用接收到的转发时钟对接收到的有效信号进行采样。在此状态下,所有数据通道必须保持低电平。

该状态可用于检测和修复(如果需要)高级封装接口的有效通道,并用于标准封装接口的功能检查。

以下是高级封装接口的步骤:

- UCIe模块发送侧带消息{MBINIT.REPAIRVAL init req}并等待响应。当准备好在RVLD_L和RRDVLD_L上接收模式时,UCIe模块的合作伙伴清除任何先前的比较结果,并以{MBINIT.REPAIRVAL init resp}进行响应。

- UCIe模块在接收到{MBINIT.REPAIRVAL init resp}后,必须在TVLD_L上发送128个VALTRAIN模式迭代(四个1后跟四个0),并使用转发的时钟。VALTRAIN模式不能进行混淆。

- UCIe模块的合作伙伴在RVLD_L和RRDVLD_L上检测到该模式。如果至少连续检测到16个VALTRAIN模式周期,则认为检测成功。接收方记录了RVLD_L和RRDVLD_L的检测结果。

- 在完成模式传输后,UCIe模块必须发送{MBINIT.REPAIRVAL result req}侧带消息,并等待获取记录的结果。

- UCIe模块的合作伙伴必须使用包含前一步结果的边带消息{MBINIT.REPAIRVAL结果响应}进行响应。如果仅在RVLD_L上检测成功而在RRDVLD_L上没有检测成功,则不需要修复。如果在RVLD_L和RRDVLD_L上都检测成功,或者仅在RRDVLD_L上检测成功,则无法修复互连。如果在RVLD_L和RRDVLD_L上都没有检测成功,则需要修复有效通道(TVLD_P/RVLD_P)。

- 在接收到{MBINIT.REPAIRVAL结果响应}后,必须重复第1步。

- UCIe模块在TRDVLD_L上发送128个VALTRAIN修复模式迭代(四个1后跟四个0),同时携带转发的时钟。VALTRAIN模式不能进行扰码。

- UCIe模块的合作伙伴在RVLD_L和RRDVLD_L上检测到这个模式。如果至少检测到16个连续的VALTRAIN模式迭代,就认为检测成功。接收器记录RVLD_L和RRDVLD_L的检测结果。

- 在完成模式传输后,UCIe模块必须发送{MBINIT.REPAIRVAL结果请求}边带消息以获取记录的结果。

- UCIe模块的合作伙伴必须停止比较,并使用前一步中的结果回复{MBINIT.REPAIRVAL结果响应}边带消息。如果仅在RRDVLD_L上检测成功而在RVLD_L上没有检测成功,则可以修复。如果在RVLD_L和RRDVLD_L上都检测成功,或者仅在RVLD_L上检测成功,则无法修复互连。如果在RVLD_L和RRDVLD_L上都没有检测成功,则TRDVLD_P/RRDVLD_P不可用,不能用于修复有效通道。

- 如果需要在(TVLD_P/RVLD_P)上进行修复且修复资源可用,UCIe模块将在其有效发射器上应用修复(第4.3.6节),并发送包含修复信息(包括不修复和无法修复)的边带消息{MBINIT.REPAIRVAL应用修复请求}。UCIe模块的合作伙伴在接收到消息后必须在其有效接收器上应用修复,并回复边带消息{MBINIT.REPAIRVAL应用修复响应}。

- 如果应用了修复,设备必须通过重复第1步到第4步来检查修复的成功与否。如果修复成功或不需要修复,UCIe模块必须发送{MBINIT.RepairVAL完成请求}边带消息,UCIe模块的合作伙伴回复{MBINIT.RepairVAL完成响应}边带消息。当UCIe模块发送和接收到{MBINIT.RepairVAL完成响应}边带消息后,必须退出到REPAIRMB状态。

- 如果修复不成功或有效通道无法修复(在步骤11中),UCIe模块在完成TRAINERROR握手后必须退出到TRAINERROR状态。

对于标准封装接口,必须在最低数据速率下检查有效通道的功能操作。以下是流程:

- UCIe模块必须发送边带消息{MBINIT.REPAIRVAL初始化请求}并等待响应。当UCIe模块的合作伙伴准备好在RVLD_L上接收模式时,必须回复{MBINIT.REPAIRVAL初始化响应}。

- 在接收到边带消息{MBINIT.REPAIRVAL初始化响应}后,UCIe模块在TVLD_L上发送128个VALTRAIN模式迭代(四个1后跟四个0),同时携带转发的时钟。

- UCIe模块的合作伙伴在RVLD_L上检测到这个模式。如果至少检测到16个连续的有效修复模式迭代,就认为检测成功。接收器记录RVLD_L的检测结果。

- 在完成模式传输后,UCIe模块必须发送{MBINIT.REPAIRVAL结果请求}边带消息,并等待获取记录的结果。

- UCIe模块的合作伙伴必须停止比较,并使用前一步中的结果回复{MBINIT.REPAIRVAL结果响应}边带消息。

- 如果检测失败,UCIe模块必须在完成TRAINERROR握手后退出到TRAINERROR状态。

- 如果检测成功,UCIe模块必须发送{MBINIT.RepairVAL完成请求}边带消息,UCIe模块的合作伙伴回复{MBINIT.RepairVAL完成响应}边带消息。当UCIe模块发送和接收到{MBINIT.RepairVAL完成响应}边带消息后,必须退出到REVERSALMB状态。

4.5.3.3.5 MBINIT.REVERSALMB

这种状态只有在时钟和有效通道正常工作时才会进入。在此状态下,检测到数据通道反转。所有发射器和接收器都已启用。UCIe模块将转发的时钟相位设置在其主带上的数据UI中心。UCIe模块的合作伙伴必须使用传入的转发时钟对传入的数据进行采样。

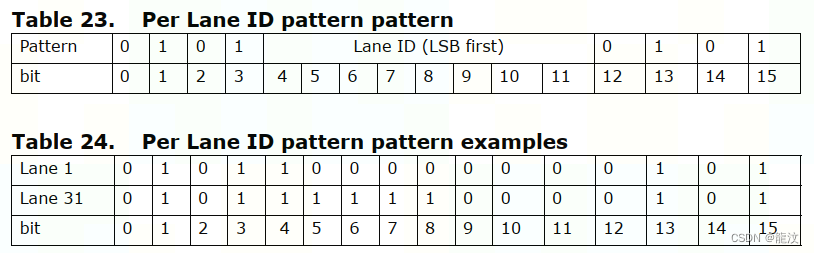

"Per Lane ID"模式是一种使用在第4.2.1节中描述的Lane ID的特定于通道的模式,使用16位的模式。Lane 0和Lane 31的"Per Lane ID"模式示例显示在Table 24中。当使用"Per Lane ID"模式时,不能对其进行扰码处理。

以下是高级封装接口和标准封装接口的反转MB序列:

对于高级封装接口和标准封装接口,步骤如下:

- UCIe模块必须发送侧带消息{MBINIT.REVERSALMB init req}。当准备好接收“Per Lane ID”模式并执行每个通道模式比较时,UCIe模块的合作伙伴必须以{MBINIT.REVERSALMB init resp}进行响应。

- 在接收到{MBINIT.REVERSALMB init resp}侧带消息后,UCIe模块必须发送{MBINIT.REVERSALMB clear error req}侧带消息。在接收到此消息后,UCIe模块的合作伙伴清除任何先前的错误,并以{MBINIT.REVERSALMB clear error resp}进行响应。在接收到{MBINIT.REVERSALMB clear error resp}后,UCIe模块使用正确的Valid帧在所有N个数据通道上(包括正确的Valid通道)发送128个“Per Lane ID”模式迭代(从最低位开始)(参见第5.11节和第4.1.2节),并使用转发的时钟。其中,N为68(64个数据通道+4个RD)用于高级封装接口,为16用于标准封装接口。

- UCIe模块的合作伙伴必须对其接收器上的所有N个通道(参见第4.4节)进行每个通道比较。如果至少连续检测到16个“Per Lane ID”模式周期,则认为在某个通道上检测成功。UCIe模块的合作伙伴记录接收通道的检测结果,用于通道反转检测。

- 在发送了128个“Per Lane ID”模式迭代后,UCIe模块停止发送该模式,并发送{MBINIT.REVERSALMB result req}侧带消息以获取记录的结果。

- UCIe模块的合作伙伴停止比较,并必须以{MBINIT.REVERSALMB result resp}侧带消息响应,其中包含每个通道的N位(高级封装接口为68,标准封装接口为16)结果。

-

如果大多数通道显示成功(因为某些通道可能需要修复),则不需要进行通道反转。跳转到第11步。

-

否则,如果第5步的结果显示大多数通道都不成功,UCIe模块将在其发射器上应用通道反转。

-

在对其发射器应用通道反转之后,UCIe模块重复执行第2步到第5步。

-

如果大多数通道显示成功,则需要进行通道反转。如果应用了通道反转,则在接下来的设备操作中保留通道反转。跳转到第11步。

-

否则,如果第8步的结果显示大多数通道都不成功,UCIe模块在完成TRAINERROR握手后必须退出到TRAINERROR状态。

-

UCIe模块必须发送{MBINIT.ReversalMB完成请求}边带消息,UCIe模块的合作伙伴将回复{MBINIT.RversalMB完成响应}。当UCIe模块发送和接收到{MBINIT.ReversalMB完成响应}边带消息后,必须退出到REPAIRMB状态。

4.5.3.3.6 MBINIT.REPAIRMB

这种状态只有在通道反转检测和应用成功之后才会进入。UCIe模块上的所有发射器和接收器都已启用。UCIe模块将时钟相位设置在其主带上的数据UI中心。UCIe模块的合作伙伴必须使用主带接收器上的传入转发时钟对传入的数据进行采样。

在此状态下,如果需要,将检测和修复主带通道,用于高级封装接口和标准封装接口的功能检查和宽度降级。

以下是高级封装接口的顺序:

- UCIe模块必须发送边带消息{MBINIT.REPAIRMB开始请求}并等待响应。UCIe模块的合作伙伴将回复{MBINIT.REPAIRMB开始响应}。

- UCIe模块设备在其发射器通道上执行发射器发起的数据到时钟点训练,如第4.5.1.1节所述。

a. 发射模式必须设置为发送128个连续模式的“Per Lane ID”模式。"Per Lane ID"模式不能进行扰码处理。接收器必须设置为执行每个通道的比较。

b. 如果在接收器通道上连续检测到至少16个迭代的“Per Lane ID”模式,则视为接收器通道的检测成功。

c. LFSR重置对MBINIT.REPAIRMB没有影响。 - UCIe模块在发射器发起的数据到时钟点测试第2步结束时,通过边带消息接收每个通道的通过/失败信息。

- 如果需要进行通道修复并且修复资源可用,UCIe模块将按照第4.3.1节的描述在其主带发射器上应用修复,并发送{MBINIT.REPAIRMB应用修复请求}边带消息。在接收到此边带消息后,UCIe模块的合作伙伴将按照第4.3.1节的描述在其主带接收器上应用修复,并发送{MBINIT.REPAIRMB应用修复响应}边带消息。如果通道故障的数量超过了修复能力(第4.3节),则主带无法修复,并且UCIe模块在执行TRAINERROR握手后必须退出到TRAINERROR状态。

- 如果不需要进行修复,请执行第7步。

- 如果应用了通道修复(第4步),UCIe模块将通过重复第2步和第3步来检查应用的修复情况。如果在第5步中记录了修复后的通道错误,则UCIe模块在执行TRAINERROR握手后必须退出到TRAINERROR状态。如果修复成功,则执行第7步。

UCIe模块发送{MBINIT.REPAIRMB end req}侧带消息,UCIe模块的合作伙伴以{MBINIT.REPAIRMB end resp}进行响应。当UCIe模块发送并接收到{MBINIT.REPAIRMB end resp}后,它必须退出到MBTRAIN状态。对于标准封装接口,将在最低数据速率下检查主通道的功能操作。以下是步骤的顺序:

对于标准封装接口:

- UCIe模块发送侧带消息{MBINIT.REPAIRMB init req}并等待响应。当UCIe模块的合作伙伴准备好在其主通道接收器上接收模式时,它会以{MBINIT.REPAIRMB init resp}进行响应。

- UCIe模块根据第4.5节中的描述执行发射器发起的数据到时钟点训练。

a. 发射模式必须设置为连续模式的“Per Lane ID”模式的128个迭代。接收器必须进行每个通道的比较。

b. 如果在接收器通道上至少连续检测到16个“Per Lane ID”模式周期,则认为检测成功。

c. 在MBINIT.REPAIRMB中,LFSR复位不会产生影响。 - UCIe模块在发射器发起的数据到时钟点测试结束时,通过侧带消息接收每个通道的通过/失败信息。

- 如果检查成功,UCIe模块发送{MBINIT.REPAIRMB end req}侧带消息,UCIe模块的合作伙伴以{MBINIT.REPAIRMB end resp}进行响应。当UCIe模块发送并接收到{MBINIT.REPAIRMB end resp}后,它必须退出到MBTRAIN状态。

- 否则,如果检查失败,并且存在宽度降级的可能性(第4.3.6节),具有故障发射器通道的UCIe模块必须对其发射器和接收器应用降级(参考表25中的逻辑通道映射),并向远程链路伙伴发送{MBINIT.REPAIRMB apply degrade req}。UCIe模块的合作伙伴必须对其发射器和接收器应用降级,并发送{MBINIT.REPAIRMB apply degrade resp}。UCIe模块必须从上述第2步开始重复。

- 否则,UCIe模块在执行TRAINERROR握手后必须退出到TRAINERROR状态。

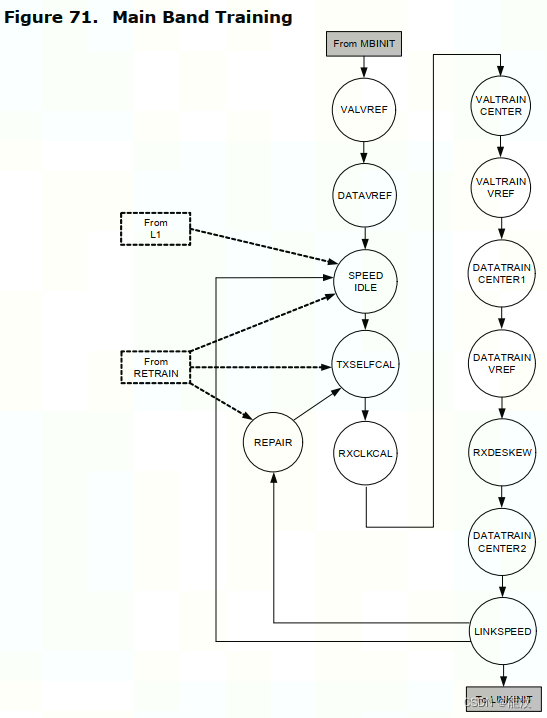

4.5.3.4 MBTRAIN

MBTRAIN状态用于在设置操作速度时执行时钟到数据中心的校准。在更高的速度下,可能需要进行额外的校准,如接收时钟校正、发送和接收器去斜校准,以确保链路性能。MBTRAIN允许子状态执行所有所需的校准和训练。UCIe模块必须进入每个子状态,并且每个状态的退出都通过边带握手进行。如果在子状态中不需要特定操作,UCIe模块可以通过边带握手退出该状态,而无需执行该子状态中描述的操作。

设备在MBINIT完成后进入此状态。这个状态对于高级封装接口和标准封装接口是共同的。

4.5.3.4.1 MBTRAIN.VALVREF

在这个状态下,接收器参考电压(Vref)用于采样传入的有效信号,并进行优化。主带上的数据速率将保持在最低支持的数据速率(4 GT/s)。UCIe模块的合作伙伴必须将转发时钟相位设置在其主带发射器上的数据UI中心。UCIe模块必须使用转发时钟对有效信号上的模式进行采样。在有效通道参考电压训练期间,所有数据通道必须保持低电平。

有效接收器参考电压调整的顺序如下:

- UCIe模块必须发送边带消息{MBTRAIN.VALVREF开始请求}并等待响应。当接收到{MBTRAIN.VALVREF开始请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.VALVREF开始响应}。

- UCIe模块通过调整接收器参考电压并执行一个或多个接收器发起的点测试(第4.5.1.3节)或接收器发起的眼图宽度扫描(第4.5.1.4节)来优化其有效接收器的Vref。

a. 发射模式必须设置为发送128个连续模式的“VALTRAIN”(四个1和四个零)模式(表21)。该模式不能进行扰码处理。接收器必须设置为对有效通道进行比较。

b. 如果在接收器通道上检测到的“VALTRAIN”模式检测错误低于设置的阈值,则视为接收器通道的检测成功。

c. 需要注意的是,LFSR RESET对MBTRAIN.VALVREF没有影响。 - UCIe模块在Vref优化后必须发送{MBTRAIN.VALVREF结束请求}边带消息(执行Vref优化的一种方法是在每个设置上逐步调整Vref并执行步骤2)。当接收到{MBTRAIN.VALVREF结束请求}时,UCIe模块的合作伙伴必须回复{MBTRAIN.VALVREF结束响应}。当UCIe模块发送并接收到边带消息{MBTRAIN.VALVREF结束响应}后,必须退出到MBTRAIN.DATAVREF状态。

4.5.3.4.2 MBTRAIN.DATAVREF

在这个状态下,接收器参考电压(Vref)用于采样传入的数据,并进行优化。UCIe模块主通道上的数据速率将保持在最低支持的数据速率(4 GT/s)。发射器设置的转发时钟相位设置在数据UI的中心位置。

数据接收器参考电压调整的顺序如下:

- UCIe模块发送侧带消息{MBTRAIN.DATAVREF start req}。当接收到{MBTRAIN.DATAVREF start req}侧带消息时,UCIe模块的合作伙伴将以{MBTRAIN.DATAVREF start resp}进行响应。

- UCIe模块通过调整数据接收器参考电压并执行一个或多个接收器发起的点测试(第4.5.1.3节)或接收器发起的眼图宽度扫描(第4.5.1.4节)来优化数据Vref。

a. 发射器必须设置为发送4K UI的连续模式LFSR模式(第4.4.1节中描述)。数据上的LFSR模式必须伴随着Valid Lane上的正确有效帧(第4.1.2节中描述)。接收器必须进行每个通道的比较。

b. 如果接收器通道上的总错误计数小于设定的错误阈值,则认为检测成功。 - UCIe模块在Vref优化后必须发送{MBTRAIN.DATAVREF end req}侧带消息(可以通过在每个设置上执行步骤2来执行Vref优化的一种方法)。当接收到{MBTRAIN.DATAVREF end req}时,UCIe模块的合作伙伴必须以{MBTRAIN.DATAVREF end resp}进行响应。一旦UCIe模块发送并接收到侧带消息{MBTRAIN.DATAVREF end resp},它必须退出到MBTRAIN.SPEEDIDLE状态。

4.5.3.4.3 MBTRAIN.SPEEDIDLE

这是一个电气空闲状态,允许频率变化。

-

如果从MBTRAIN.DATAVREF状态进入此状态,则UCIe模块将根据两个设备之间的最高公共速度过渡到基于数据速率的状态(第4.5.3.3.1节)。如果从LINKSPEED或PHYRETRAIN状态进入此状态,则选择下一个较低的数据速率。

-

在完成到所需数据速率的过渡后,UCIe模块必须发送带有当前链路速度信息的{MBTRAIN.SPEEDIDLE完成请求}边带消息。当接收到{MBTRAIN.SPEEDIDLE完成请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.SPEEDIDLE完成响应}。一旦UCIe模块发送并接收到{MBTRAIN.SPEEDIDLE完成响应}边带消息,它必须退出到MBTRAIN.TXSELFCAL状态。

4.5.3.4.4 MBTRAIN.TXSELFCAL

UCIe模块在独立于UCIe模块合作伙伴的情况下校准其电路参数。在此步骤中,UCIe模块必须使其发射器保持电气空闲状态。

- UCIe模块被允许执行与发射器相关的任何所需校准。

- 在完成校准后,UCIe模块必须发送侧带消息{MBTRAIN.TXSELFCAL Done req}。当接收到{MBTRAIN.TXSELFCAL Done req}消息时,UCIe模块的合作伙伴必须以{MBTRAIN.TXSELFCAL Done resp}进行响应。一旦UCIe模块发送并接收到{MBTRAIN.TXSELFCAL Done resp}侧带消息,它必须退出到MBINIT.RXCLKCAL状态。

4.5.3.4.5 MBTRAIN.RXCLKCAL

-

当UCIe模块准备对其时钟接收路径进行校准时,发送边带消息{MBTRAIN.RXCLKCAL开始请求}。当接收到边带消息{MBTRAIN.RXCLKCAL开始请求}时,UCIe模块的合作伙伴开始发送转发时钟,并发送边带消息{MBTRAIN.RXCLKCAL开始响应}。发射器时钟必须自由运行,并且所有数据通道和有效信号必须保持低电平。UCIe模块被允许使用转发时钟来执行任何与时钟路径相关的校准。在此状态下,UCIe模块的合作伙伴不得调整其发射器上的任何电路或PI相位参数。

-

当执行所需的校准(如果有)时,UCIe模块发送{MBTRAIN.RXCLKCAL完成请求}消息。当接收到{MBTRAIN.RXCLKCAL完成请求}时,UCIe模块的合作伙伴停止发送转发时钟,并通过发送{MBTRAIN.RXCLKCAL完成响应}消息作出回应。当UCIe模块发送并接收到{MBTRAIN.RXCLKCAL完成响应}边带消息时,必须退出到VALTRAINCENTER状态。

4.5.3.4.6 MBTRAIN.VALTRAINCENTER

为确保有效信号正常工作,在数据通道训练之前进行有效到时钟的训练。接收器使用转发的时钟对Valid上的模式进行采样。接收器参考电压设置为通过Vref训练获得的优化值(第4.5.3.4.1节/第4.5.3.4.2节)。在有效到时钟训练期间,所有数据通道都保持低电平。以下是MBTRAIN.VALTRAINCENTER的顺序:

- UCIe模块发送侧带消息{MBTAIN.VALTRAINCENTER start req}。UCIe模块的合作伙伴以{MBTAIN.VALTRAINCENTER start resp}进行响应。

- UCIe模块必须执行发射器发起的完整眼图宽度扫描(第4.5.1.2节)或一个或多个发射器发起的点测试(第4.5.1.1节),以确定正确的有效到时钟居中位置。

a. 发送的模式必须设置为发送128个连续模式的“VALTRAIN”(四个1和四个零)模式(表21)。此模式不得进行扰码。接收器必须设置为对Valid Lane进行比较。

b. 如果接收器通道上的“VALTRAIN”模式检测错误数小于设定的阈值,则认为检测成功。

c. 值得注意的是,在MBTRAIN.VALVREF中,LFSR RESET对其没有影响。 - UCIe模块可以使用接收到的结果日志来评估有效功能和余量。在此之后,必须执行第4步。

- UCIe模块必须发送{MBTRAIN.VALTRAINCENTER done req}侧带消息。当接收到{MBTRAIN.VALTRAINCENTER done req}时,UCIe模块的合作伙伴将以{MBTRAIN.VALTRAINCENTER done resp}进行响应。一旦UCIe模块发送并接收到{MBTRAIN.VALTRAINCENTER done resp}侧带消息,它必须退出到MBTRAIN.DATATRAINVREF状态。

4.5.3.4.7 MBTRAIN.VALTRAINVREF

UCIe模块被允许选择性地优化参考电压(Vref),以在操作数据速率下对输入的有效信号进行采样。UCIe模块和UCIe模块的合作伙伴必须进入此状态。有效信号接收器参考电压调整的顺序如下:

-

UCIe模块必须发送边带消息{MBTRAIN.VALTRAINVREF开始请求}。当接收到{MBTRAIN.VALTRAINVREF开始请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.VALTRAINVREF开始响应}。

-

UCIe模块可选择通过调整其有效信号接收器上的接收器参考电压并执行接收器发起的眼宽度扫描(第4.5.1.4节)或一个或多个接收器发起的点测试(第4.5.1.3节)来优化Vref。这是可选的,具体实现因情况而异。

a. 如果执行有效信号中心对齐,则发送模式必须设置为发送连续模式“VALTRAIN”(四个1和四个零)模式的128次迭代(表21)。此模式不得进行扰码。接收器必须进行有效信号通道的比较。

b. 如果接收器通道上的“VALTRAIN”模式检测错误小于设定的阈值,则认为接收器通道上的检测成功。

c. 值得注意的是,在MBTRAIN.VALVREF状态下,LFSR RESET不会产生影响。 -

在Vref优化完成后,UCIe模块必须发送{MBTRAIN.VALTRAINVREF结束请求}边带消息。当接收到{MBTRAIN.VALTRAINVREF结束请求}时,UCIe模块的合作伙伴必须回复{MBTRAIN.VALTRAINVREF结束响应}。一旦UCIe模块发送并接收到边带消息{MBTRAIN.VALTRAINVREF结束响应},它必须退出到MBTRAIN.DATATRAINCENTER状态。

4.5.3.4.8 MBTRAIN.DATATRAINCENTER1

在这个状态下,UCIe模块执行完整的数据到时钟训练(包括有效信号)。在此状态下,必须使用第4.4.1节中描述的LFSR模式。以下是MBTRAIN.DATATRAINCENTER的顺序:

-

UCIe模块发送侧带消息{MBTRAIN.DATATRAINCENTER1 start req}。当接收到{MBTRAIN.DATATRAINCENTER start req}侧带消息时,UCIe模块的合作伙伴将以{MBTRAIN.DATATRAINCENTER1 start resp}进行响应。

-

UCIe模块必须执行发射器发起的完整眼图宽度扫描(第4.5.1.2节)或一个或多个点测试(第4.5.1.1节),以确定正确的数据到时钟居中位置,并调整发射器的逐位去斜(如果需要)。

a. 发射器必须设置为发送第4.4.1节中描述的4K UI连续模式的LFSR模式。数据上的LFSR模式必须伴随着Valid Lane上的正确有效帧(如第4.1.2节所述)。接收器必须设置为执行每个通道的比较。

b. 如果接收器通道上的总错误计数小于设定的错误阈值,则认为检测成功。 -

如果测试成功,UCIe模块必须将时钟相位设置为在最佳点采样数据眼图,以最大化眼图余量。UCIe模块必须发送{MBTRAIN.DATATRAINCENTER1 end req}侧带消息。当接收到{MBTRAIN.DATATRAINCENTER1 end req}侧带消息时,UCIe模块的合作伙伴将以{MBTRAIN.DATATRAINCENTER1 end resp}进行响应。一旦UCIe模块发送并接收到{MBTRAIN.DATATRAINCENTER1 end resp}侧带消息,它必须退出到MBTRAIN.DESKEW状态。

注意:在这一步中,眼图开口可能不足(测试失败),接收器可能需要逐位去斜。因此,UCIe模块必须退出到MBTRAIN.DESKEW状态。

4.5.3.4.9 MBTRAIN.DATATRAINVREF

UCIe模块被允许选择性地优化其数据接收器上的参考电压(Vref),以优化对操作数据速率下输入数据的采样。UCIe模块和UCIe模块的合作伙伴必须进入此状态。

数据接收器参考电压调整的顺序如下:

-

UCIe模块必须发送边带消息{MBTRAIN.DATATRAINVREF开始请求}。当接收到{MBTRAIN.DATATRAINVREF开始请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.DATATRAINVREF开始响应}。

-

UCIe模块可选择通过调整接收器参考电压并执行接收器发起的眼宽度扫描(第4.5.1.4节)或一个或多个接收器发起的点测试(第4.5.1.3节)来优化Vref。这是可选的,具体实现因情况而异。如果执行数据Vref优化:

a. 发射器必须设置为发送4K UI的连续模式LFSR模式,该模式在第4.4.1节中有描述。数据上的LFSR模式必须与第4.1.2节中描述的正确有效帧配合使用。接收器必须设置为对每个通道进行比较。

b. 如果接收器通道上的总错误计数小于设定的错误阈值,则认为接收器通道上的检测成功。 -

在Vref优化完成后,UCIe模块必须发送{MBTRAIN.DATATRAINVREF结束请求}边带消息。当接收到{MBTRAIN.DATATRAINVREF结束请求}时,UCIe模块的合作伙伴必须回复{MBTRAIN.DATATRAINVREF结束响应}。一旦UCIe模块发送并接收到边带消息{MBTRAIN.DATATRAINVREF结束响应},它必须退出到MBTRAIN.RXDESKEW状态。

4.5.3.4.10 MBTRAIN.RXDESKEW

在这个状态下,UCIe模块可以选择对其接收器进行每个通道的去斜,以改善时序余量。UCIe模块和UCIe模块的合作伙伴必须进入这个状态。

-

UCIe模块必须发送侧带消息{MBTRAIN.RXDESKEW start req}。当接收到{MBTRAIN.RXDESKEW start req}侧带消息时,UCIe模块的合作伙伴将以{MBTRAIN.DESKEW start resp}进行响应。

-

UCIe模块可以选择通过接收器发起的完整眼图宽度扫描(第4.5.1.4节)或一个或多个接收器发起的点测试(第4.5.1.3节)对其接收器进行每个通道的去斜。这是可选的,具体实现取决于实现。如果进行每个通道的去斜操作:

a. 发射器必须设置为发送第4.4.1节中描述的4K UI连续模式的LFSR模式。数据上的LFSR模式必须伴随着Valid Lane上的正确有效帧(如第4.1.2节所述)。接收器必须设置为执行每个通道的比较。

b. 如果接收器通道上的总错误计数小于设定的阈值,则认为检测成功。 -

UCIe模块在进行或跳过去斜操作后,必须发送{MBTRAIN.RXDESKEW end req}侧带消息。当接收到{MBTRAIN.RXDESKEW end req}时,UCIe模块的合作伙伴必须以{MBTRAIN.RXDESKEW end resp}进行响应。一旦UCIe模块发送并接收到侧带消息{MBTRAIN.RXDESKEW end resp},它必须退出到MBTRAIN.DATATRAINCENTER状态。

4.5.3.4.11 MBTRAIN.DATATRAINCENTER2

这个状态是为了让UCIe模块重新将时钟重新对准,以聚合数据,以防止UCIe模块的合作伙伴的接收器执行了每个通道的时钟偏移校准。

以下是MBTRAIN.DATATRAINCENTER的顺序:

-

UCIe模块发送边带消息{MBTRAIN.DATATRAINCENTER2开始请求}。当接收到{MBTRAIN.DATATRAINCENTER开始请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.DATATRAINCENTER2开始响应}。

-

UCIe模块必须执行发射器发起的全眼宽度扫描(第4.5.1.2节)或一个或多个发射器发起的点测试(第4.5.1.1节),以确定正确的数据对眼中心对齐。

a. 发射器必须设置为发送4K UI的连续模式LFSR模式,该模式在第4.4.1节中有描述。数据上的LFSR模式必须与第4.1.2节中描述的正确有效帧配合使用。接收器必须设置为对每个通道进行比较。

b. 如果接收器通道上的总错误计数小于设定的错误阈值,则认为接收器通道上的检测成功。 -

UCIe模块使用接收到的训练结果来计算最终的眼中心,并设置时钟相位以在最佳点采样数据眼以最大化眼余量。UCIe模块必须发送{MBTRAIN.DATATRAINCENTER2结束请求}边带消息。当接收到{MBTRAIN.DATATRAINCENTER2结束请求}边带消息时,UCIe模块的合作伙伴将回复{MBTRAIN.DATATRAINCENTER2结束响应}。一旦UCIe模块发送并接收到边带消息{MBTRAIN.DATATRAINCENTER2结束响应},它必须退出到MBTRAIN.LINKSPEED状态。

4.5.3.4.12 MBTRAIN.LINKSPEED

在这个状态下,UCIe模块在操作数据速率下检查链路稳定性。必须按顺序执行以下步骤:

-

UCIe模块发送侧带消息{MBTRAIN.LINKSPEED start req}。当接收到{MBTRAIN.TXTRAIN start req}侧带消息时,UCIe模块的合作伙伴将以{MBTRAIN.LINKSPEED start resp}进行响应。

-

UCIe模块必须使用在上一个MBTRAIN.DATACENTER2状态中计算出的最终时钟采样相位执行点测试(第4.5.1.1节)。在此状态下,必须使用第4.4.1节中描述的LFSR模式。

a. 发射器必须设置为发送第4.4.1节中描述的4K UI连续模式的LFSR模式。数据上的LFSR模式必须伴随着Valid Lane上的正确有效帧(如第4.1.2节所述)。接收器必须设置为执行每个通道的比较。

b. 如果接收器通道上的总错误计数小于设定的阈值,则认为检测成功。 -

对于单个模块实例化,如果遇到错误,UCIe模块将其发射器设置为电气空闲状态,并发送{MBTRAIN.LINKSPEED error req}侧带消息。如果接收到{MBTRAIN.LINKSPEED error req}侧带消息,则UCIe模块的合作伙伴必须完成步骤1到步骤2,并在其接收器上进入电气空闲状态,并发送侧带消息{MBTRAIN.LINKSPEED error resp}。

a. 基于遇到错误的通道数量,UCIe模块检查是否可以修复失败的通道(对于高级封装)或降低带宽(对于标准封装)。如果通道可以修复(对于高级封装)或降低带宽(对于标准封装),UCIe模块必须发送{MBTRAIN.LINKSPEED exit to repair req}给UCIe模块的合作伙伴,并等待响应。UCIe模块的合作伙伴进入MBTRAIN.REPAIR状态,并发送侧带消息{MBTRAIN.LINKSPEED exit to repair resp}。随后,UCIe模块必须退出到MBTRAIN.REPAIR状态。

b. 如果通道无法修复(对于高级封装)或降低带宽(对于标准封装),则必须降低速度。UCIe模块发送{MBTRAIN.LINKSPEED exit to speed degrade req}侧带消息。UCIe模块的合作伙伴必须退出到MBTRAIN.SPEEDIDLE状态,并以{MBTRAIN.LINKSPEED exit to speed degrade resp}进行响应。随后,UCIe模块必须退出到MBTRAIN.SPEEDIDLE状态,以将数据速率降低到下一个较低速度。

c. 如果UCIe模块接收到{MBTRAIN.LINKSPEED exit to speed degrade req},则必须忽略任何未完成的{MBTRAIN.LINKSPEED exit to repair req}或{MBTRAIN.LINKSPEED done req},并且UCIe模块必须对{MBTRAIN.LINKSPEED exit to speed degrade req}进行响应。

-

对于单个模块实例,如果没有遇到错误,UCIe模块必须设置其发射器的时钟相位,以在最佳点采样数据眼以最大化眼余量。UCIe模块必须发送{MBTRAIN.LINKSPEED完成请求}边带消息。当接收到{MBTRAIN.LINKSPEED完成请求}时,UCIe模块的合作伙伴必须回复{MBTRAIN.LINKSPEED完成响应}。当UCIe模块发送并接收到边带消息{MBTRAIN.LINKSPEED完成响应}时:如果PHY_IN_RETRAIN未设置,则执行步骤7。如果设置了PHY_IN_RETRAIN变量,则必须执行以下操作:

a. 如果从PHYRETRAIN条目检测到运行时链路测试控制寄存器的更改,UCIe模块必须发送{MBTRAIN.LINKSPEED退出到PHY重新训练请求}并等待响应。收到此消息后,UCIe模块的合作伙伴必须退出到PHY重新训练并发送{MBTRAIN.LINKSPEED退出到PHY重新训练响应}。一旦收到此边带消息,UCIe模块必须退出到PHY重新训练。

b. 否则,如果未检测到更改,则必须清除运行时链路测试状态中的Busy位和PHY_IN_RETRAIN变量。现在必须执行下面的步骤7。

c. 如果UCIe模块接收到{MBTRAIN.LINKSPEED退出到降速请求}或{MBTRAIN.LINKSPEED退出到修复请求},则必须忽略任何未完成的{MBTRAIN.LINKSPEED完成请求},并且UCIe模块必须响应接收到的边带消息。 -

对于多个模块实例,在第2步之后,每个UCIe模块向多模块PHY逻辑(MMPL)报告第2步的结果,并等待解决方案。多模块PHY逻辑在接收到此信息后,必须遵循第4.7.1节中的规则,并为每个UCIe模块提供必要的操作。这些操作包括:

a. 如果MMPL指示UCIe模块退出到LINKINIT,则UCIe模块必须发送{MBTRAIN.LINKSPEED完成请求}边带消息。当接收到{MBTRAIN.LINKSPEED完成请求}时,UCIe模块的合作伙伴必须回复{MBTRAIN.LINKSPEED完成响应}。当UCIe模块发送并接收到边带消息{MBTRAIN.LINKSPEED完成响应}后,它必须退出到LINKINIT。如果UCIe模块接收到{MBTRAIN.LINKSPEED退出到降速请求}或{MBTRAIN.LINKSPEED退出到修复请求},则必须忽略任何未完成的{MBTRAIN.LINKSPEED完成请求},并且UCIe模块必须响应接收到的边带消息。

b. 如果MMPL指示UCIe模块退出到SPEEDIDLE,则UCIe模块发送{MBTRAIN.LINKSPEED退出到降速请求}边带消息。UCIe模块的合作伙伴必须退出到MBTRAIN.SPEEDIDLE并回复{MBTRAIN.LINKSPEED退出到降速响应}。在此之后,UCIe模块必须退出到MBTRAIN.SPEEDIDLE以将数据速率设置为下一个较低的速度。

c. 如果MMPL指示UCIe模块退出到REPAIR,则UCIe模块必须向UCIe模块合作伙伴发送{MBTRAIN.LINKSPEED退出到修复请求}并等待响应。UCIe模块合作伙伴进入MBTRAIN.REPAIR并发送边带消息{MBTRAIN.LINKSPEED退出到修复响应}。在此之后,UCIe模块必须退出到MBTRAIN.REPAIR。

-

. 如果没有遇到错误且为Retimer,则需要遵循以下规则以实现链路匹配(如果需要):

a. Retimer在目标链路速度和远程Retimer合作伙伴的链路宽度解决为当前链路和宽度之前,不得发送{MBTRAIN.LINKSPEED完成请求}。

b. 在与远程Retimer合作伙伴解决目标链路速度和宽度时,它必须每4毫秒发送带有停顿编码的{MBTRAIN.LINKSPEED完成响应}。UCIe Retimer必须确保此停顿不是永久性的,并且Retimer中必须包含特定实现的超时。

c. 如果本地UCIe链路速度或宽度大于远程Retimer UCIe链路,则必须按顺序执行以下操作:

i. 必须发送不带停顿编码的{MBTRAIN.LINKSPEED完成响应}。

ii. 这种情况必须视为错误条件,并执行步骤4或步骤5中适用的修复或降速操作。 -

现在,发送器和接收器都已启用且处于空闲状态,两个设备都退出到LINKINIT。

4.5.3.4.13 MBTRAIN.REPAIR

这个状态可以从PHYRETRAIN或MBINIT.LINKSPEED状态进入。对于高级封装接口,此状态将用于修复,对于标准封装接口,此状态将用于链路宽度降级。

对于高级封装接口,如果当前可用的修复资源数量大于遇到错误的通道数量,则必须应用修复。

-

UCIe模块发送侧带消息{MBTRAIN.REPAIR init req}给其发射器,UCIe模块的合作伙伴以{MBTRAIN.REPAIR init resp}进行响应。

-

如果可以修复通道,UCIe模块将根据第4.3.1节的描述对其发射器通道进行修复,并发送{MBTRAIN.REPAIR Apply repair req}侧带消息。UCIe模块的合作伙伴根据第4.3.1节的描述进行修复,并在应用所需修复后以{MBTRAIN.REPAIR Apply repair resp}侧带消息进行响应。

-

UCIe模块必须发送{MBTRAIN.REPAIR end req}侧带消息,并等待响应。UCIe模块的合作伙伴必须以{MBTRAIN.REPAIR end resp}进行响应。当UCIe模块发送并接收到{MBTRAIN.REPAIR end resp}时,它必须退出到MBTRAIN.TXSELFCAL状态。

对于标准封装接口,如果遇到错误的通道全部包含在Lane 0到Lane 7或Lane 8到Lane 15中,必须将宽度降级为x8链路(Lane 0 ... Lane 7或Lane 8 ... Lane 15)。

-

UCIe模块发送侧带消息{MBTRAIN.REPAIR init req},接收器以{MBTRAIN.REPAIR init resp}进行响应。

-

如果可以降低宽度,请求降低宽度的UCIe模块应用宽度降级,并发送{MBTRAIN.REPAIR Apply degrade req}侧带消息。该消息包括具有Lane反转意识的Lane映射信息(对于Lane 0...7为2b'01,对于Lane 8...15为2b'10)。如果接收到Lane映射2b'01,则UCIe模块的合作伙伴将使用Lane 0...7,如果接收到Lane映射2b'10,则使用Lane 8...15。降级应用后,UCIe模块以{MBTRAIN.REPAIR Apply degrade resp}进行响应。

-

UCIe模块必须发送{MBTRAIN.REPAIR end req}侧带消息,并等待响应。UCIe模块的合作伙伴必须以{MBTRAIN.REPAIR end resp}进行响应。当UCIe模块发送并接收到{MBTRAIN.REPAIR end resp}时,它必须退出到MBTRAIN.TXSELFCAL状态。

4.5.3.5 LINKINIT

这个状态用于允许完全的芯片对芯片适配器在进入主动状态之前完成初始的链路管理。请参考第8.1.6节了解有关RDI启动流程的更多详细信息。

一旦RDI处于活动状态,物理层将从UCIe链路控制寄存器中清除其“启动UCIe链路训练”位的副本。

在进入这个状态时,线性反馈移位寄存器(LFSR)必须被重置。

这个状态对于高级和标准封装接口是共用的。

4.5.3.6 ACTIVE

在物理层初始化完成后,RDI处于活动状态,并且上层的数据包可以在两个芯片之间进行交换。

在这个状态下,所有的数据都使用第4.4.1节描述的LFSR扰码器进行扰码。

这个状态对于高级封装和标准封装接口是通用的。

4.5.3.7 PHYRETRAIN

一个芯片可以因为多种原因进入物理层重新训练。物理层进入物理层重新训练的触发条件如下所述的情况之一:

• 适配器指示的物理层重新训练:适配器可以因为任何认为必要的原因指示物理层进行重新训练。

• 物理层发起的物理层重新训练:当检测到有效的帧错误时,本地物理层必须发起重新训练。

• 远程芯片请求的物理层重新训练:当接收到远程芯片的请求时,本地物理层必须进入物理层重新训练。

• 如果在MBTRAIN.LINKSPEED期间检测到运行时链路测试控制寄存器中的变化。

在进入物理层重新训练时,必须设置一个变量PHY_IN_RETRAIN。

4.5.3.7.1 Adapter initiated PHY retrain

以下是适配器发起物理层重新训练的步骤序列:

- UCIe模块从本地适配器接收到重新训练请求(RDI状态请求移至重新训练)。接下来,UCIe模块必须按照第8.0章节中描述的方法,在RDI上完成停顿请求/应答(pl_stallreq;lp_stallack)握手。

- UCIe模块必须向UCIe模块伙伴发送侧带消息{PHYRETRAIN.retrain init req}。

- UCIe模块伙伴在接收到侧带消息{PHYRETRAIN.retrain init req}后,必须在其RDI接口上完成停顿请求/应答(pl_stallreq;lp_stallack)握手后将其RDI状态转换为重新训练。随后,UCIe模块伙伴会回复{PHYRETRAIN.retrain init resp}。

- 一旦接收到{PHYRETRAIN.retrain init resp},UCIe模块必须将其RDI状态转换为重新训练。

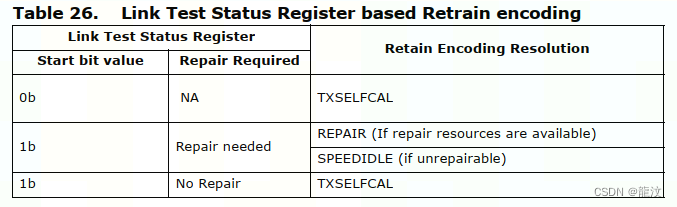

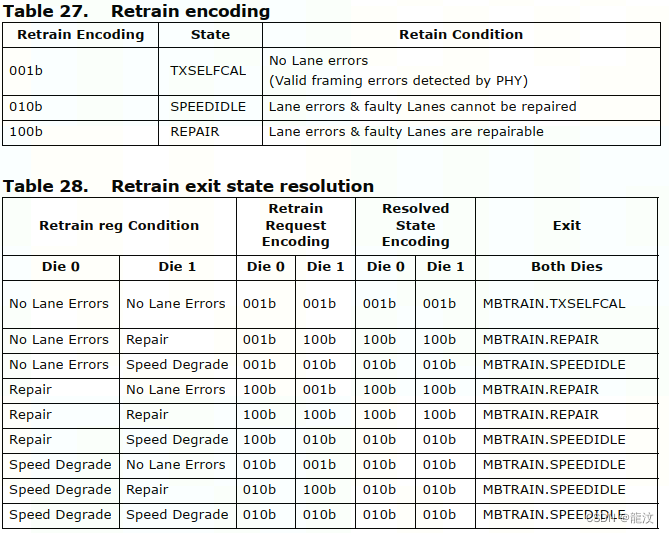

- UCIe模块必须发送带有重新训练编码的{PHYRETRAIN.retrain start req},其中重新训练编码反映了运行时链路测试控制寄存器的内容(除了启动位),如果运行时链路测试状态寄存器中的忙位被设置。随后,UCIe模块伙伴将接收到的重新训练编码与本地重新训练编码进行比较。如果接收到的重新训练编码与本地重新训练编码相同,UCIe模块伙伴必须回复{PHYRETRAIN.retrain start resp}。如果重新训练编码不匹配,UCIe模块伙伴必须根据表26、表27和表28中的重新训练编码和解决方案进行解决,然后发送{PHYRETRAIN.retrain start resp}。

- 一旦UCIe模块发送和接收到侧带消息{PHYRETRAIN.retrain start resp},它必须根据解决后的重新训练寄存器编码退出到相应的训练状态。

4.5.3.7.2 PHY initiated PHY retrain

PHY发起的PHY重训练的步骤如下:

-

当检测到有效的帧错误时,UCIe模块必须在通过RDI传输该flit(或flit块)时断言pl_error。在此之后,UCIe模块(PHY)必须完成RDI上的stall Req/Ack(pl_stallreq; lp_stallack)握手。

-

UCIe模块必须发送侧带消息{PHYRETRAIN.retrain init req}。

-

接收到侧带消息{PHYRETRAIN.retrain init req}的UCIe模块的合作伙伴在完成其RDI上的stall Req/Ack(pl_stallreq; lp_stallack)握手后,必须将其RDI转换为retrain状态。随后,UCIe模块的合作伙伴以{PHYRETRAIN.retrain init resp}进行响应。

-

一旦接收到{PHYRETRAIN.retrain init resp},UCIe模块必须将其RDI转换为retrain状态。

-

UCIe模块必须发送带有retrain编码的{PHYRETRAIN.retrain start req},该编码反映Runtime Link Test Control寄存器的内容(除了Start位)(如果Runtime Link Test Status Register中的Busy位被设置)。随后,UCIe模块的合作伙伴将接收到的retrain编码与本地retrain编码进行比较。如果接收到的retrain编码与本地retrain编码相同,则UCIe模块的合作伙伴必须以{PHYRETRAIN.retrain start resp}进行响应。如果retrain编码不匹配,则UCIe模块的合作伙伴必须根据表26、表27和表28中的Retrain编码和解决方案进行解决,然后发送{PHYRETRAIN.retrain start resp}。

-

一旦UCIe模块发送并接收到侧带消息{PHYRETRAIN.retrain start resp},它必须根据retrain编码退出到相应的训练状态。

4.5.3.7.3 Remote Die requested PHY retrain

- 在接收到{PHYRETRAIN.retrain init req}后,UCIe模块必须在其RDI上完成停顿请求/应答(pl_stallreq;lp_stallack)握手后将本地RDI状态转换为重新训练。随后,UCIe模块会回复{PHYRETRAIN.retrain init resp}。

- 一旦接收到{PHYRETRAIN.retrain init resp},UCIe模块伙伴必须将其RDI状态转换为重新训练。

- UCIe模块必须发送带有重新训练编码的{PHYRETRAIN.retrain start req},其中重新训练编码反映了运行时链路测试控制寄存器的内容(除了启动位),如果运行时链路测试状态寄存器中的忙位被设置。随后,UCIe模块会将接收到的重新训练编码与本地重新训练编码进行比较。如果接收到的重新训练编码与本地重新训练编码相同,UCIe模块伙伴会回复{PHYRETRAIN.retrain start resp}。如果重新训练编码不匹配,UCIe模块伙伴必须根据表26、表27和表28中的重新训练编码和解决方案进行解决,然后发送{PHYRETRAIN.retrain start resp}。

- 一旦芯片发送和接收到侧带消息{PHYRETRAIN.retrain start resp},它必须根据重新训练编码退出到相应的训练状态。

4.5.3.7.4 PHY retrain from LINKSPEED

-

UCIe模块必须发送带有反映Runtime Link Test Control寄存器内容(除了Start位)的retrain编码的{PHYRETRAIN.retrain start req}(如果Runtime Link Test Status Register中的Busy位被设置)。随后,UCIe模块的合作伙伴将接收到的retrain编码与本地retrain编码进行比较。如果接收到的retrain编码与本地retrain编码相同,则UCIe模块的合作伙伴必须以{PHYRETRAIN.retrain start resp}进行响应。如果retrain编码不匹配,则UCIe模块的合作伙伴必须根据表26、表27和表28中的Retrain编码和解决方案进行解决,然后发送{PHYRETRAIN.retrain start resp}。

-

一旦一个芯片发送并接收到侧带消息{PHYRETRAIN.retrain start resp},它必须根据retrain编码退出到相应的训练状态。

4.5.3.8 TRAINERROR

TRAINERROR状态用作过渡状态,用于处理需要将状态机返回到RESET状态的任何致命或非致命事件。这可能发生在初始化和训练过程中,或者当状态机不处于RESET状态时设置了"Start UCIe Link training"位于UCIe Link控制寄存器中。它还用于将链路从链路正常状态转换为链路断开状态的任何事件。

从TRAINERROR状态到RESET状态的退出是与实现相关的。对于没有错误升级的情况(即,RDI不处于LinkError状态),建议尽快退出TRAINERROR状态。对于存在错误升级的情况(即,RDI处于LinkError状态),物理层必须在RDI处于LinkError状态时持续处于TRAINERROR状态。

有关RDI上可纠正的、非致命的和致命的错误升级,请参考第8.0章。

该状态适用于高级和标准包接口。

如果侧带处于活动状态,则必须对UCIe模块和UCIe模块伙伴进行侧带握手,以使其从除SBINIT以外的任何状态进入TRAINERROR状态。以下是定义的TRAINERROR握手过程:

- 请求退出到TRAINERROR的UCIe模块必须发送{TRAINERROR Entry req}侧带消息并等待响应。UCIe模块伙伴必须退出到TRAINERROR状态并回复{TRAINERROR Entry resp}。一旦收到{TRAINERROR Entry resp}侧带消息,UCIe模块必须退出到TRAINERROR状态。如果在8ms内没有收到响应,链路训练状态机将转换到TRAINERROR状态。

4.5.3.9 L1/L2

PM状态允许比ACTIVE中的动态时钟门控更低的功耗状态。

• 当RDI转换到PM状态时,进入该状态,如第8.0章所述。该状态下的PHY功耗节省功能是特定于实现的。

• 当本地适配器在RDI上请求Active或远程链路伙伴请求L1退出时,PHY必须退出到MBTRAIN.SPEEDIDLE状态。L1退出与RDI上的相应L1状态退出转换进行协调。

• 当本地适配器在RDI上请求Active或远程链路伙伴请求L2退出时,PHY必须退出到RESET状态。L2退出与RDI上的相应L2状态退出转换进行协调。

4.6 Run time Recalibration

在ACTIVE状态下,接收器可以使用Track信号进行周期性的运行时校准。在运行时重新校准期间,主通道数据必须继续正确采样。为了请求Track模式,以下是相应的步骤序列:

- UCIe模块在其接收器上启用Track信号缓冲,并发送侧带消息{RECAL.track pattern init req},然后等待响应。

- UCIe模块伙伴发送{RECAL.track pattern init resp},并启用其Track信号发射器。随后,发射器开始发送在第5.5.1节中描述的模式。

- 接收器执行所需的重新校准,并发送侧带消息{RECAL.track pattern done req}。

- 在接收到此消息后,发射器停止发送模式,并发送侧带消息{RECAL.track pattern done resp}。

- 在接收到侧带消息{RECAL.track pattern done resp}后,接收器可以禁用Track接收器。

注意:上述步骤描述了请求Track模式的过程,以便进行周期性的运行时校准。具体实现中可能还有其他细节和条件需要考虑。

4.7 Multi-module Link

正如第1.0章所述,多模块链路的允许配置有一模块、两模块和四模块配置。

4.7.1 Multi-module initialization

在多模块配置中,每个模块必须使用其侧带独立进行初始化和训练。如果使用了两个或四个模块,则一个单独的多模块物理逻辑块(MMPL)在模块之间进行协调,如1.2.2节所述。多模块物理逻辑(MMPL)负责协调跨多个模块的数据传输。多模块链路中的每个模块必须以相同的宽度和速度运行。在初始化或重新训练过程中,如果任何模块无法进行训练,MMPL必须确保多模块配置降级到下一个允许的降级配置。随后,必须使用以下规则解决不同模块之间的速度和宽度差异:

-

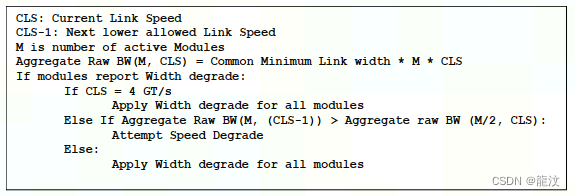

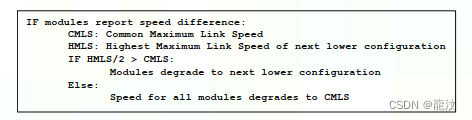

对于标准封装的多模块配置,如果任何模块报告了宽度降级:

a. 如果小于或等于一半的模块在当前链路速度下报告了宽度降级,则相应的模块必须被禁用。MMPL必须确保多模块配置降级到下一个允许的降级配置。例如,如果四个模块中有三个处于活动状态,则MMPL必须将链路降级为两个模块的配置。

b. 如果大多数模块在当前链路速度下报告了宽度降级,请参考下面的伪代码。

2. 对于高级或标准封装的多模块配置,如果模块报告速度差异,请参考下面的伪代码。

3. 对于标准封装的模块,如果同时报告了宽度和速度差异,MMPL必须在(1)和(2)之间选择最佳配置。

4.7.1.1 Sideband assignment

在链路初始化、训练和重新训练(第4.5节)期间,所有侧带消息都通过各个模块的侧带接口发送。

注意:对于来自上层或与RDI状态转换相关的所有其他侧带消息,使用单个侧带进行发送和接收侧带消息。设备必须在其逻辑LSB模块的侧带接口(Module-0)上发送侧带消息。在侧带接收器上,可以在不同的逻辑模块上接收到在逻辑LSB模块上发送的消息。

1460

1460

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?