GraphPlanner: Floorplanning with Graph Neural Network

https://doi.org/10.1145/3555804

一、摘要

在超大规模集成电路芯片的物理实现中,芯片布图规划一直是一项具有高计算复杂度的关键任务。它的主要目标是以最小的线长确定大芯片模块的初始位置,同时坚持密度约束,这在本质上是一个过程,构建一个优化的映射从电路连接到物理位置。芯片布图规划是一个NP难题,很难用算法有效地解决。本文介绍了GraphPlanner,这是一种用于芯片布局规划的基于变分图卷积网络的深度学习技术。GraphPlanner能够学习电路连接性和物理线长之间的优化和广义映射,并使用高效的模型推理生成芯片布图规划。GraphPlanner还配备了一种高效的聚类方法,即超边缘粗化与图谱聚类的统一,将大规模网表划分为具有最小化簇间加权连接的高质量簇。GraphPlanner已与两个最先进的混合尺寸放置模型集成。使用学术基准和工业设计的实验研究表明,与最先进的混合尺寸放置器相比,GraphPlanner将放置运行时间提高了25%,平均线长减少了4%。

二、简介

芯片布图规划是VLSI芯片物理实现中的关键步骤和具有挑战性的任务。它确定大芯片模块的初始位置(例如,嵌入式存储器、知识产权(IP)核、标准单元簇),并且能够早期估计互连长度、电路延迟和芯片性能[3]。芯片布图规划的质量对许多下游优化目标具有显著影响,其中布局线长是最重要的一个,因为线长与信号传播延迟、功率、可布线性和制造成本密切相关。与仅放置宏的传统布图规划不同,现代版本输入混合宏块和标准单元的网表,并放置它们,以便针对给定区域约束优化物理线长。

即使在经典公式[35]中也被证明是NP难的,芯片布图规划难以使用算法方法有效地解决。由于缺乏有效的自动化工具,大多数专业设计师不得不手动完成这项工作,通常需要数月的紧张工作[34]。为了提高生产力,Google开发了一种基于深度强化学习的平面规划器[34]。它采用了成功的AlphaGo系统中使用的方法,将布局规划过程视为一系列移动,每个移动都在芯片上放置一个宏。当所有宏被放置时,使用商业工具进行下游物理实现阶段,并且计算最终奖励。与AlphaGo类似,这个最终奖励被反向传播到序列中的每个情况和动作,并基于这些奖励训练评估网络和策略网络。据报道,该系统在6小时内生成的TPU设计结果优于人类专家。

我们的工作受到了Google工作的极大启发,我们同意深度学习是解决芯片布局问题的一种有前途的方法。另一方面,我们在芯片布局规划中使用强化学习是相当保守的,因为将任务分解为一系列移动,每个移动只放置一个块,使工作复杂化。与围棋游戏完全不同的是,在围棋游戏中,玩家只能在对方未知的下一步棋之前走一步棋,芯片设计师预先拥有电路网表的完整连接信息,并且很少需要在顺序过程中一次一个块地进行布局规划。 在现实中,考虑到电路的整体视图,专家设计师通常将电路划分为越来越精细的子电路,并且每次同时将一个级别的所有子电路放置在芯片上,优化它们之间的数据流。本质上,它是一次建立粗略的布图规划的过程,其中从子电路连接到物理位置的映射是优化的。

在这项工作中,受电路专家如何创建芯片平面图的启发,我们追求一个变分图卷积网络为基础的(GCN为基础的)方法芯片布图规划。一般的经验法则,“在人类的直觉发挥的地方,神经网络可能会胜利,”这种方法开始与分区的网表到子电路集群的基础上提出的高效聚类算法C-谱聚类,以减少问题的大小,使集群的标准单元和宏的大小相当。在此基础上,利用变分GCN模型对子电路的连通性进行了全面的理解,并基于变分推理学习子电路连通性与物理线长之间的优化和广义映射,进而利用高效的模型推理生成电路块的物理位置.然后使用所得到的布图来驱动下游混合尺寸布局任务。

拟议的工作旨在回答以下三个研究问题:

- 如何在电路连通性和物理线长之间建立一个优化的、广义的映射关系?我们建议使用变分GCN为基础的方法。该模型由一个基于GCN的变分推理编码器和一个生成解码器组成,用于学习电路连接性和物理线长之间的优化和广义映射,并进一步生成宏和标准单元的物理位置,即,芯片布局,然后驱动下游布局任务。

- 如何在不需要大的真实世界数据集的情况下训练基于变分GCN的布局规划器?现实世界的最佳布图规划是具有挑战性的。我们提出了一种方法来生成一个合成的训练数据集与最佳的平面布置方案来训练变分GCN为基础的模型。在数据集中,电路连通性和物理线长之间的映射被保证是最优的。使用合成训练数据集,经训练的模型可以产生优化的平面布置图。此外,它还提供了广泛的统计连接分布,以确保经过训练的模型在现实世界的设计中得到很好的推广。

- 如何有效地将网表划分为高质量的簇?所提出的变分GCN的布图规划器进一步配备了一个高效的聚类方法,它统一了超边粗化与图谱聚类。所提出的方法可以有效地划分成高质量的集群与最小化的簇间加权连接的大规模网表。

被称为GraphPlanner的布局规划器已与两个最先进的混合大小放置器集成,这将与合成数据集沿着公开发布。使用ISPD2005基准测试和实际行业设计的实验研究表明,与最先进的混合尺寸放置器相比,GraphPlanner始终将放置运行时间提高了25%,平均线长减少了4%。使用学术基准和工业设计也验证了GraphPlanner的泛化能力。我们还通过将基于变分GCN的模型与两种广泛使用的图嵌入方法Spectrum [12]和GAT[44]进行比较来扩展实验,以进一步证明所提出的基于变分GCN的模型的有效性。

三、相关工作

布局规划是确定大型物理模块的初始位置(例如,嵌入式存储器、IP核、标准单元簇),并且能够对互连线长进行早期估计,以便优化芯片尺寸、改善时序等[3]。研究人员已经提出了各种布局表示(例如,序列对[27,35]、有界切片网格[19]和B* 树[7])和布图规划算法(例如,模拟退火[26,27]、遗传算法[28,37]和粒子群优化[8,22,43])来解决布图规划问题,其中前者旨在对布图规划进行合适的表示,以便形式化和最小化问题搜索空间的大小和计算复杂度,而后者用于布图规划优化和生成。所得到的布图规划用于随后的放置器以完成芯片放置任务并产生宏单元和标准单元的最终位置,同时实现一组优化目标,例如,最小化连接对象的总线长。

在芯片放置方面,早期的工作主要是基于分区的[4,13,14]和基于随机/爬山的方法(例如,基于模拟退火的砂矿)[26,38]。基于分区的布局器递归地将网表和布局区域划分为较小的分区,直到子问题可以被最优地解决。这些方法可以分层应用,这使他们能够处理大规模的电路布局问题。然而,通过独立地优化每个子问题而不考虑其他分区,基于分区的方法可能会负面地影响全局解的质量。对于基于模拟退火的放置算法,增加了随机扰动以避免放置陷入局部最优。虽然这种方法产生高质量的解决方案,它是耗时的,很难被并行化,因此很难被应用到大型和复杂的电路。上述这些放置工作仅集中于放置标准单元,并且宏的位置由布局规划阶段确定,这限制了整体物理设计空间的优化潜力[20]。

现代芯片放置器应用分析技术来同时处理宏和标准单元的放置,作为统一的混合尺寸放置任务,例如Kraftwerk [41],NTUPlace3 [9],mPL6 [6]和FLOP [46]。最近的混合尺寸放置工作,如ePlace [32],RePlAce [10]和DREAMPlace [17,29],能够产生高质量的放置解决方案。这些方法将混合尺寸布局问题表示为约束非线性优化问题。目标函数由凸线长函数和加权非凸密度函数组成。芯片布局是一个由无线感应力和密度感应力共同驱动的迭代优化过程。优化过程通过收集所有可移动对象(即,宏和标准单元)到具有最小线长的微小簇,然后基于缓慢增加的密度惩罚迭代地将对象展开。这样的过程通常会产生高质量的解决方案,但具有较长的迭代时间。

最近,研究人员开始探索基于机器学习的方法来解决芯片布局和芯片放置问题。Xie等人。[45]利用图形注意力网络在放置之前估计净长度,优于现有的解决方案。Lu等人。[33]将GraphSAGE应用于节点表示学习,并将其与K-Means算法相结合,以生成用于放置指导的聚类。Liu等人[47]提出了一种基于图形注意力网络的方法来完成芯片布局规划。图神经网络(GNN)也用于学习网表嵌入,并配备强化学习(RL)代理以完成布局任务,同时提高对新设计的泛化能力[1,2,34]。[34]是Google提出的一项典型工作,它将GNN与深度强化学习相结合,用于芯片放置。这项工作应用了一个基于RL的代理顺序放置宏和基于力的方法来放置标准的细胞簇。在放置所有对象之后,计算奖励并反向传播以训练策略网络。它报告了比人类专家更好和更快的TPU设计结果。Cheng和Yan [11]提出了一种端到端的基于RL的放置器,可以联合放置宏和标准单元。

从最近提出的RL为基础的顺序优化方法,启发如何电路专家创建和优化芯片布图,我们追求一个基于GNN的方法,学习优化和广义的映射从电路连接到对象的物理位置与优化的线长。该模型可以通过高效的模型推理产生高质量的芯片布图规划。所提出的方法已被集成与国家的最先进的混合尺寸的布局方法,以完成下游的混合尺寸的布局任务,具有高质量的结果。

四、问题描述

平面布置实例可以被建模为G=(C, E)具有对象集合C(即,宏和群集标准单元)由超边E连接。芯片布图规划的主要目标可以被公式化为最小化总无线长度W(c),同时遵守密度约束ρ(c):

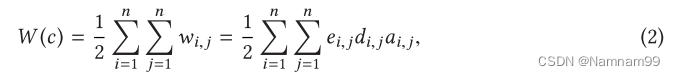

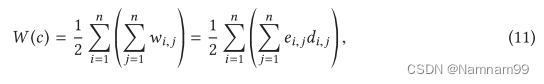

通过将超图G建模为连接矩阵[3],可以将布图规划的总线长W(c)估计为所有连接对象之间的线长之和,其在等式(2)中定义:

其中

e

i

,

j

e_{i,j}

ei,j和

d

i

,

j

d_{i,j}

di,j分别表示对象i和j之间的连接数和距离,并且

a

i

,

j

a_{i,j}

ai,j是邻接矩阵,其中如果对象i和j连接,则

a

i

,

j

a_{i,j}

ai,j = 1,否则为0。

在密度方面,根据[31],可以将放置区域均匀地划分为表示为G的一组网格(bin),并且可以如等式(3)计算每个网格D的密度:

其中

l

x

(

i

,

g

)

l_x(i,g)

lx(i,g)和

l

y

(

i

,

g

)

l_y(i,g)

ly(i,g)表示网格e和单元i之间的水平和垂直重叠。根据等式(2),对于给定的电路网表,e和a是已知的。因此,布图规划的目标是在满足密度约束的同时计算连接对象之间的最佳距离d。因此,布图规划的本质是构建互连和物理线长之间的优化映射,然后引导下游任务优化并产生最终的芯片布局。

五、GRAPHPLANNER方法

本节介绍了GraphPlanner,提出的基于变分GCN的布图规划器。它首先描述了整个算法流程,然后介绍了GraphPlanner的关键组件,包括聚类、基于变分GCN的模型和合成训练数据集生成。

5.1 解决方案概述

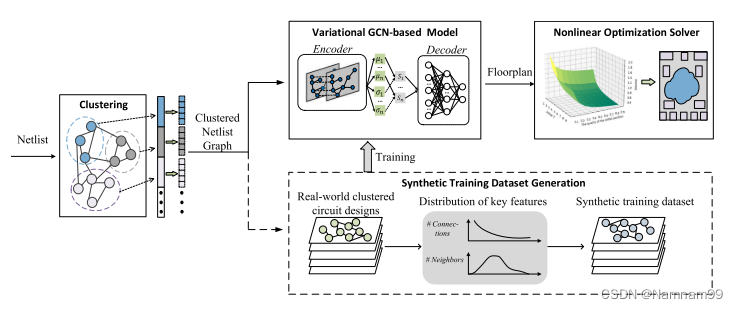

图1描述了GraphPlanner的整体算法流程。给定一个电路网表表示为一个加权的无向超图,GraphPlanner开始分区的网表成子电路集群使用建议的c-谱聚类算法,以减少问题的大小,并使集群的标准单元和宏的大小可比。划分的子电路超图,包括宏和集群的标准单元,被送入变分GCN为基础的模型学习电路连接性和物理线长之间的优化映射,并进一步生成一个芯片布图的基础上的距离正则化项,然后送入下游的放置器,以产生最终的芯片布局。使用合成数据集训练基于变分GCN的模型,而不需要真实世界的芯片设计。合成数据集由覆盖广泛的电路连接性分布的最佳布图规划解决方案,以确保所提出的变分基于GCN的布图规划的泛化。

图1.GraphPlanner概述。聚类模块将表示为加权无向图的网表划分成子电路簇。基于变分GCN的模型旨在学习电路连接性与物理距离之间的优化映射,并预测对象的初始位置(即,芯片布局),其使用合成数据集来训练,而不需要真实世界的芯片设计。然后将基于变分GCN的模型的输出馈送到下游的基于非线性优化的放置器中以完成放置任务。

5.2 C谱聚类算法

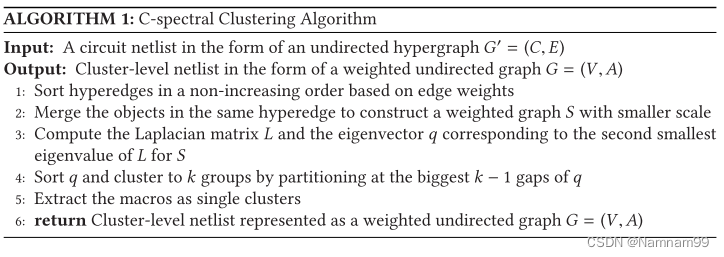

本节描述所提出的c-谱聚类算法。先前的工作已经表明,谱聚类可以有效地最小化聚类间加权连接,但对于大规模图来说运行时间较长[42]。提出的c-谱聚类算法的目的是利用谱聚类的好处,但避免其高计算成本,通过自底向上的超边缘粗化。

所提出的c-谱聚类算法总结在算法1中。第1-2行描述了自底向上的超边缘粗化过程。由于具有高连接性权重的对象需要紧密地放置在芯片上,粗化过程基于超边缘权重执行自下而上的聚类,从而减小图的规模并减轻谱聚类的计算成本。具体地,给定在具有一组对象C(即,宏和聚类的标准单元),超边粗化过程首先基于边权重以非递增顺序对超边进行排序。按照排序顺序,由同一超边连接的对象将合并到一个簇中。这个过程继续进行,直到达到预定义的集群总数。

粗化过程的输出是具有较小尺度的加权图S的形式,其然后被馈送到谱聚类(行3-4)。我们采用基于频谱的聚类方法[42]。我们首先计算图S的拉普拉斯矩阵L,并计算对应于L的第二小特征值的特征向量q。然后,我们对特征向量q进行排序,并通过找到排序特征向量的最大k-1个间隙将对象划分为k个聚类。我们还应用Lanczos算法[15]来提高特征值和特征向量。最后,我们提取宏作为单个集群,以平衡每个集群内的细胞的总面积。c谱聚类的输出是由对象集V和邻接矩阵A定义的加权无向图G =(V,A)形式的聚类级网表。

5.3 变分图卷积网络

本节提出了所提出的用于布图规划生成的基于变分GCN的模型,其具有电路连接性和物理线长之间的优化映射。

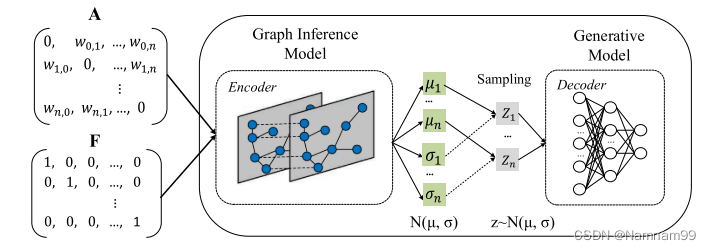

- 模型构造:如图2所示,模型的输入是从由所提出的c-谱聚类算法生成的聚类网表获得的对象连接性信息,并且模型的输出是对象的位置,即,芯片平面图。该模型包含图推理编码器和生成解码器,其中配备变分推理的图推理编码器由两层变分GCN [24]参数化以从生成角度编码电路连接信息,并且生成解码器由多层感知器组成MLP(MLP)[16]基于所学习的电路连接性与连接对象的物理线长之间的优化映射来解码到对象物理位置或芯片布图规划的嵌入。

图2 基于GCN的变分模型的体系结构。与变分推理集成的图推理编码器将电路连接性信息编码为潜在空间上的分布。生成解码器对从潜在空间中的分布采样到芯片布图规划的采样点进行解码。

编码器: 图推理编码器的输入包含特征矩阵F和加权邻接矩阵A,该特征矩阵F和加权邻接矩阵A是从通过c-谱聚类生成的聚类网表G =(V,A)获得的(第4.2节)。 F ∈ R N × h F∈R^{N×h} F∈RN×h包括作为行的所有对象的特征向量,其中每个对象具有由独热嵌入表示的h维特征向量(即,每个对象被映射到二进制向量)。 A ∈ R N × N A ∈ R^{N×N} A∈RN×N是一个 N × N N×N N×N加权邻接矩阵,其中 A i , j = w A_{i,j }= w Ai,j=w,如果i和j索引的对象由w条边连接(或者连接对象i和对象j的边的权为w),否则Ai,j = 0。

图推理编码器基于变分的基于GCN的模型学习每个对象的广义新表示。由于GCN可以通过有效的迭代邻域聚合来有效地利用图结构的优点,因此我们最初将F和A输入到单层GCN以获得第一层对象嵌入 e 0 e_0 e0。为了进一步改进模型的泛化,我们参考[23,25]将编码器与概率变体集成,即通过将 e 0 e_0 e0编码为潜在空间中的分布而不是单个点来开发潜在空间的正则化。换句话说,我们将e0映射到一个分布而不是一个固定的向量,以避免过拟合,并更好地描述潜在空间中的互连分布的对象,使布图生成过程。

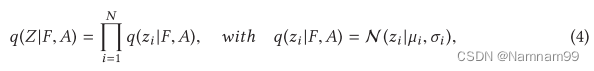

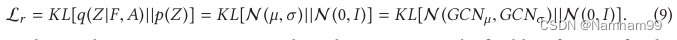

设q(Z| F,A)表示潜在空间中的后验分布:

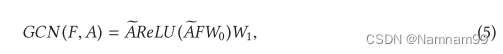

其中μ = GCNμ(F,A)和σ = GCNσ(F,A)是描述分布的均值矩阵和协方差矩阵。图推断编码器由两层GCN参数化,其定义如下:

其中

A

^

=

D

−

1

2

A

D

−

1

2

\hat{A} = D^{−\frac{1}{2}} AD^{−\frac{1}{2}}

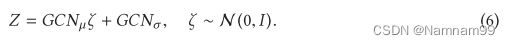

A^=D−21AD−21是对称归一化邻接矩阵,Wi表示第i层权重矩阵。GCNμ(F,A)和GCNσ(F,A)共享第一层参数W0。我们进一步基于重参数化技巧[23](参见等式(6))从潜在空间中的分布N(μ,σ)进行采样以获得采样点

Z

∈

R

N

×

M

(即,

Z ∈ R^{N×M}(即,

Z∈RN×M(即,Z~q(Z| F,A)

)

)

),然后将Z馈送到生成解码器中以得到芯片布图规划:

解码器: 由MLP组成的生成解码器将采样点Z解码为所有对象的2维坐标(即,芯片布局)基于所学习的群集网表连通性和连接对象的物理线长之间的优化映射。令Xl ∈ RN×2表示由解码器预测的对象位置。我们如下定义计算Xl的模型:

其中,

f

θ

l

:

R

M

→

R

2

f_{θ_l} : R^M → R^2

fθl:RM→R2 是具有可学习参数

θ

l

θ_l

θl的MLP以解码对象位置。

损失函数:

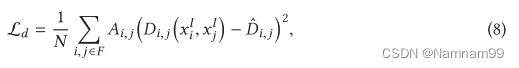

通过最小化损失函数来训练模型,损失函数由两个分量组成,最终层上的重建项和潜在层上的正则化项。重建项促使模型通过基于由解码器产生的对象位置计算所有连接对象的距离来生成优化的平面布置图,其可以表示如下:

其中

D

i

,

j

D_{i,j}

Di,j表示对象i和j的模型预测位置的距离(即,

x

l

i

和

x

l

j

{x^l}_i和{x^l}_ j

xli和xlj),

D

^

i

,

j

\hat{D}_{i,j}

D^i,j表示i和j之间距离的真实距离值,

A

i

,

j

A_{i,j}

Ai,j是邻接矩阵。我们应用连接对象的距离而不是对象位置来训练模型的原因在于两个方面。首先,布图规划旨在优化电路互连与位置确定的对象间物理距离之间的映射。因此,使用对象间距离作为中间约束项有助于提高从电路互连到物理位置的优化映射的建模功效。第二,距离是比位置更具有变换不变性的特征。例如,当平面布置图被旋转或翻转时,距离保持不变,而对象位置改变。因此,距离比位置更能反映对象之间的关系。

损失函数的正则化项旨在通过使后验分布

q

(

Z

∣

F

,

A

)

q(Z| F,A)

q(Z∣F,A)接近先验分布

p

(

Z

)

p(Z)

p(Z)。我们应用Kullback-Leibler散度来测量这两个分布之间的距离。为了简化计算复杂度并减少参数的数量,我们遵循[25]假设p(Z)是标准高斯分布,其可以直接用均值和协方差矩阵表示,i.e.,

p

(

Z

)

=

∏

i

p

(

z

i

)

=

∏

i

N

(

z

i

∣

0

,

I

)

.

p(Z) =∏_i p(z_i ) =∏_i N(z_i |0, I).

p(Z)=∏ip(zi)=∏iN(zi∣0,I).

为此,可以如下计算正则化项:

通过组合重构项和正则化项,基于变分GCN的模型的最终损失函数定义如下:

与下游模型结合: 使用具有互连和对象的线长之间的最佳映射的合成训练数据集来训练模型(参见图1)。第4.4节)。训练后的模型可以直接应用于预测芯片布图规划看不见的现实世界的电路设计的基础上的模型推理。

具体而言,给定一个真实世界的电路设计,它首先被划分成K个子电路集群使用cspectral聚类,然后子电路集群被送入训练的变分GCN为基础的模型(包括编码器和解码器),以获得芯片布图规划。通过将宏单元和标准单元的初始位置设置为模型输出,模型的输出与下游放置工具进一步集成。通过调整初始密度权重,随后的放置器(例如,DREAMPlace [17]和RePlAce [10])从所提出的模型预测的对象的初始位置继续放置任务,而不是使用所有对象都在芯片中心的位置作为初始位置,使得集成的布图规划-放置流程与单独的放置器相比可以有效地减少放置任务的优化迭代和运行时间,并提供高质量的放置结果。

原因在于,如ePlace-MS [32]所指出的,对于基于现代非线性优化的放置工具,初始解对最终放置结果的质量至关重要。为此,现有技术的砂矿(例如,ePlace-MS、RePlace和DREAMPlace)都由初始阶段组成,该初始阶段通过首先将块聚集到芯片的中心以最小化线长,然后通过将大权重应用于HPWL并将小权重应用于密度来调整芯片的中心区域周围的块的初始位置。该过程确实提高了最终放置质量,然而,这显著减慢了整体放置过程,而所提出的模型可以预测对象的优化初始位置(即,芯片布局),其具有高效的模型推理,这驱动下游放置器绕过耗时的初始化阶段,从而有效地减少了总迭代和运行时间,并具有高质量的结果。更多的实验证明和细节,请参见第5.2节。

5.4 合成训练数据集生成

现实世界的最佳平面布置图是很难获得的。即使假设它们的最佳布局是已知的,有限数量的公共基准也远远不足以支持深度模型的训练。我们提出了一种方法来创建一个合成的训练数据集来解决这个问题。

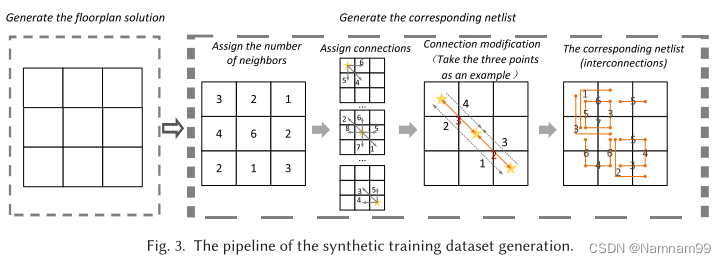

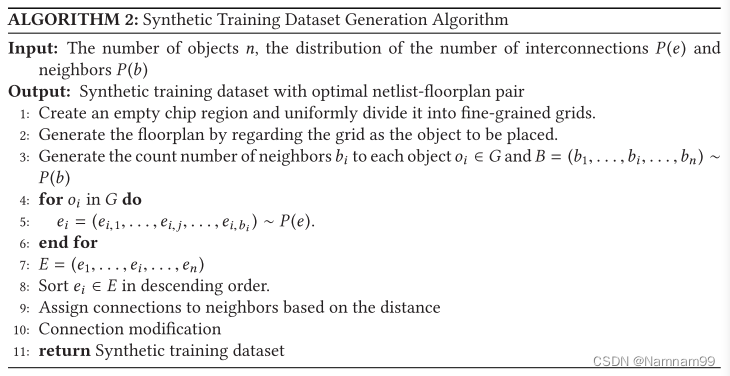

如第3节所述,布图规划器的主要优化目标是在满足给定密度约束的同时最小化总线长,其可以如等式(2)和(3)所示进行计算。因此,合成训练数据集的创建需要保证每个创建的网表-布图规划对将包含电路连接性和对象间物理线长之间的最佳映射而没有重叠。根据等式(2),我们可以从给定的集群网表中提取的关键特征是e和a,其可以被转换为连接性的统计分布,更具体地,表示为E的两个邻居之间的连接数量的分布和表示为B的每个对象的邻居数量的分布。

如图3所示,为了构建合成训练数据集,我们首先创建一个空的芯片区域,并将该区域均匀地分解为一组M * N个矩形网格。每个网格被视为要放置的对象,这保证了对象的放置是不重叠的(即,满足密度约束)。这是训练数据集中的平面布置方案。因此,合成训练数据集中的对象在芯片区域中具有规则排列的相等大小。

接下来,我们生成相应的网表。首先,我们对每个对象进行连接分配(即,生成相应的网表)以保证电路连通性和线长之间的最佳映射(即,总的线长被最小化),使得我们可以获得最优的网表-布图规划对。具体地,我们计算了E和B在各种簇电路中的概率分布,其可以分别表示为P(e)和P(b)。

接下来,我们生成邻居的数量

B

=

(

b

1

,

…

,

b

i

,

.

.

.

,

b

n

)

P

(

b

)

B =(b_1,…,b_i,...,b_n)~ P(b)

B=(b1,…,bi,...,bn) P(b),并且连接数

E

=

(

e

1

,

…

,

e

i

,

.

.

.

,

e

n

),

∀

e

i

E =(e_1,…,e_i,...,e_n),∀e_i

E=(e1,…,ei,...,en),∀ei ~

P

(

e

)

P(e)

P(e),其中b_i表示对象i的邻居的数量,并且

e

i

=

(

e

i

,

l

,

e

i

,

2

,

…

,

e

i

,

b

i

)

e_i =(e_i,l,e_i,2,…,e_i,b_i)

ei=(ei,l,ei,2,…,ei,bi)表示对象i与其邻居之间的互连数的集合。我们以降序对

e

i

e_i

ei进行排序,并将更多的连接分配给距离较短的邻居。由于芯片区域中的对象具有相等的尺寸和网格结构,因此存在位于对象的上、下、左和右的多达四个物理上最近的邻居。次近邻位于对象的左上、左下、右上和右下。我们现在给予一个例子来进一步详细说明基于距离的连接分配策略。假设对象i的坐标是(x,y)(假设0 < x < n,0 < y < n,即,对象不位于芯片区域的边界中),则存在四个物理上最近的邻居,其坐标分别为(x-1,y)、(x + 1,y)、(x,y-1)和(x,y + 1)。如果bi < 4,我们从最近的四个邻居中随机选择bi个邻居,并将连接分配给它们。如果fbi> 4,我们基于距离分配连接;也就是说,前四个最大数量的连接被分配给最近的四个邻居,而离对象较远的邻居被分配较少的连接,直到分配了E1中的所有数量的连接。在这种情况下,每个对象与其相邻对象之间的互连的分布是最优的(参见图1)。证明)。

在所有对象都分配了邻居和互连后,通过计算每个对象对的平均连接数并将其设置为对象之间的最终连接数来进行连接修改,从而确保对象之间的连接数对称。具体地,假设对象i分配给对象j的连接数是

e

i

,

j

e_{i,j}

ei,j,并且j分配给i的连接数是

e

j

,

i

e_{j,i}

ej,i ;则i和j之间的连接数被修改为

(

e

i

,

j

+

e

j

,

i

)

/

2

(即,

e

i

,

j

=

(

e

i

,

j

+

e

j

,

i

)

/

2

)

(e_{i,j} + e_{j,i})/2(即,e_{i,j} =(e_{i,j} + e_{j,i})/ 2)

(ei,j+ej,i)/2(即,ei,j=(ei,j+ej,i)/2),以确保连接关系的对称性。这种修改虽然改变了邻居和连接数的分布,但仍然保证了网表-布图对的最优性,即解决方案保证了对象之间没有重叠的最小总线路长度(参见.算法2)。则每个对象的坐标O(x,y)可以被视为位置标签(即,芯片平面图),并且每个连接对象对之间的物理距离是距离标记

D

L

a

b

e

l

DLabel

DLabel。数据集的构建在算法2中描述。因此,我们可以获得具有最佳布图方案和广泛覆盖统计连通性分布的合成训练数据集,从而确保训练后的模型具有良好的泛化能力。

证明: 最优布图方案表明,对象的位置保证了最小的总线长,而不重叠.由于对象在空芯片区域上的初始放置已经确保对象不重叠,网表-布图规划对的最优性取决于线长分布。

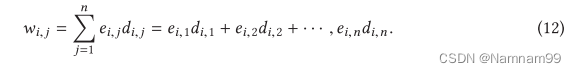

平面图的总线路长度W(c)可以计算为:

其中,

∑

j

=

1

n

w

i

,

j

\sum ^n _ {j = 1}w_{i,j}

∑j=1nwi,j表示对象i和所有其他对象之间的总线路长度,

d

i

,

j

d_{i,j}

di,j和

e

i

,

j

e_{i,j}

ei,j表示i和j之间的距离和连接数。其次,我们证明了

∑

j

=

1

n

w

i

,

j

\sum ^n _ {j = 1}w_{i,j}

∑j=1nwi,j的最优性;也就是说,对于任何对象i,i和它的邻居之间的线长分布是最佳的

∑

j

=

1

n

w

i

,

j

\sum ^n _ {j = 1}w_{i,j}

∑j=1nwi,j可计算为:

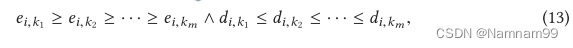

由于e是预先已知的,为了在不违反密度约束的情况下最小化

w

i

,

j

w_{i,j}

wi,j,d需要与e成反比,即:

其映射在连接修改之前在合成训练数据集中得到保证。交换任何邻居的位置将导致

w

i

,

j

w_{i,j}

wi,j增加;也就是说,没有比当前解决方案具有更好性能的解决方案,这证明了wi,j的最优性。

由于总线路长度W(c)=

∑

j

=

1

n

(

∑

j

=

1

n

w

i

,

j

)

\sum ^n _ {j = 1} (\sum ^n _ {j = 1}w_{i,j})

∑j=1n(∑j=1nwi,j),因此连接修改(即,计算每个对象对的平均连接作为它们的最终连接数)不影响总线路长度的最优性,从而证明了网表-布图规划对在合成训练数据集中的最优性。

此外,合成数据集应在电路连接方面提供广泛的覆盖,以确保训练模型的泛化。图4示出了在使用c-谱聚类算法进行聚类之后ISPD 2005基准中的两个关键特征B(由蓝色直方图表示)和E(由灰色直方图表示)的分布。从图中我们可以看到,两个关键特性在不同的基准测试中差异很大。我们进一步计算B和E的统计特征,包括众数(及其比例)、平均值和标准差(见表1)。如图4和表1所示,大多数集群的邻居都少于10个。

在聚类之后,指示所述聚类电路的连通性局部性。关于E的分布,簇之间的连接的数量相对较小,其中在邻居之间仅具有一个连接的簇占所有簇的大约50%。这一结果表明,所提出的C-谱聚类算法,它使对象与最小化的连接被分配到不同的集群的有效性。为了便于统计和减少参数的数量,我们应用高斯分布来近似两个关键特征的分布,这两个特征可以用均值μ和标准差σ来描述;为了提高训练模型的泛化能力,我们在μ和σ上添加随机偏差,以生成具有不同分布的电路连通性统计特征的合成训练数据集。

如图5所示,在这项工作中,合成数据集的连通性统计数据(由红色虚线指示)足以覆盖学术基准的连通性统计数据,例如,ISPD2005和真实世界的工业设计(用不同颜色的点表示)。即使是“真实世界”电路也可能与每个合成训练数据都不相同,它在附近有许多训练数据。此外,如果连接性分布显著偏离合成数据集的新的现实世界电路设计,用户可以通过生成具有对应连接性统计的合成数据集来进一步扩展合成数据集(即,μ和σ)以适应新的设计。由于所提出的基于变分GCN的模型的推广性,它具有基于相邻训练数据“内插”解的能力。我们的实验表明,情况就是这样(cf.第5节)。

GraphPlanner是一种深度学习技术,用于芯片布局规划,尤其适用于超大规模集成电路。它利用变分图卷积网络学习电路连接性和物理线长之间的优化映射,并生成高效的芯片布图。通过高效的聚类方法减少问题规模,与现有混合尺寸放置器集成,能显著降低放置运行时间和线长。相比传统方法,GraphPlanner在实验中表现出更好的性能和速度。

GraphPlanner是一种深度学习技术,用于芯片布局规划,尤其适用于超大规模集成电路。它利用变分图卷积网络学习电路连接性和物理线长之间的优化映射,并生成高效的芯片布图。通过高效的聚类方法减少问题规模,与现有混合尺寸放置器集成,能显著降低放置运行时间和线长。相比传统方法,GraphPlanner在实验中表现出更好的性能和速度。

610

610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?