SPEC:Rev 7.0

规格:

1.通信速度:

standard-mode:100kbps

fast-mode:400kbps

fast-mode plus:1Mbps

high-speed mode:3.4Mbps

2.半双工、多主多从

基本原理

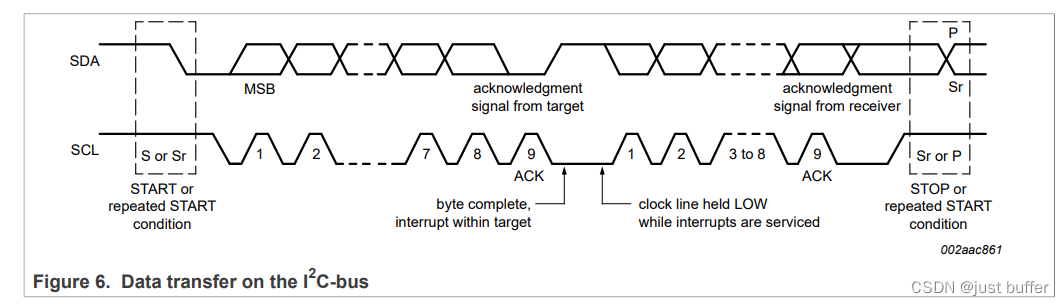

总线空闲状态:SCL和SDA都处在高电平。

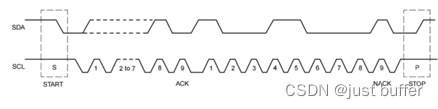

起始信号:SCL高电平时SDA从高到低。

终止信号:SCL高电平时SDA从低到高。

数据传输:按字节发送、SDA在时钟低电平切换、高电平保持。

ACK和NACK:第九个时钟拉低SDA为ACK、拉高为NACK.

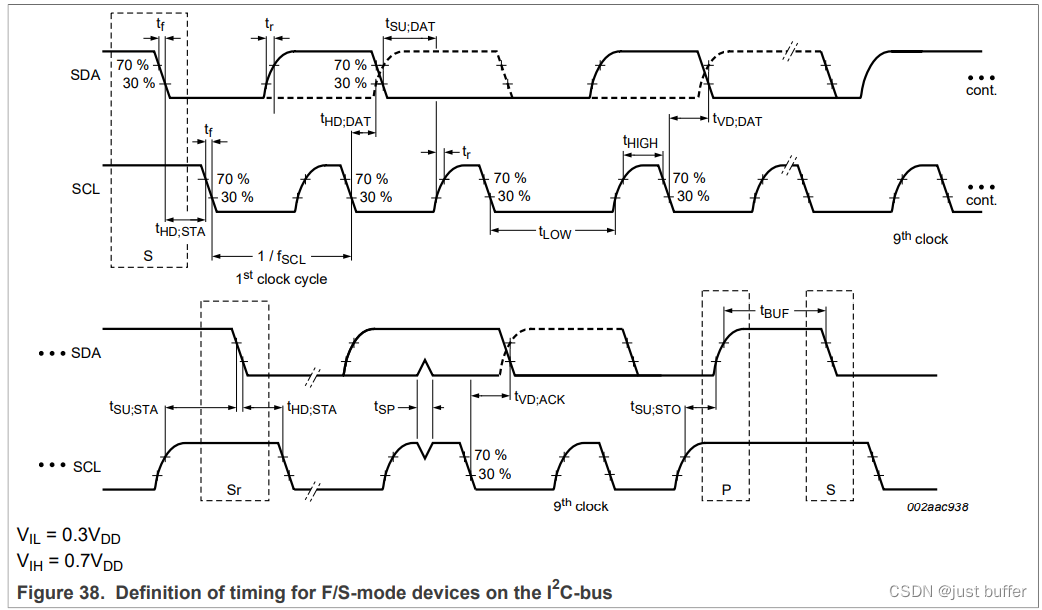

建立保持时间:

t(HD;DAT):hold time 保持时间,时钟下下降沿之后,SDA需要保持的时间。

t(SU;DAT):set-up time建立时间,时钟沿上升之前,SDA需要保持的时间。

相关点:

时钟同步:

双主机时钟不同时,SCL通过线与同步低速时钟。

总线仲裁:

解决多主机情况下总线冲突情况,SCL空闲状态下。两个主机一前一后的拉低SDA启动发送,则仲裁开始。

仲裁期间,主机逐位监测发送和电平和读取电平是否一致,不一致则停止发送,让出总线。

常见问题:

总线挂死:

情况一:SDA挂死

先来看下哪些情况下I2C从机会需要拉低SDA线:

(1) 主机向从机写数据或地址时,从机如果发出A应答,则会第9个CLK的期间拉低SDA

(2) 主机读数据的时候,从机会在bit为0时对应的CLK期间拉低SDA

那什么情况I2C从机可能钳住SDA线呢?假如在读数据时,从机在SCK高电平时拉低SDA发送0,按照I2C协议规定,SCK高电平期间,SDA应当保持,假如此时主机发生复位或断点,则主机恢复后,默认SCK为高电平,SDA仍然处于被从机拉低的状态,此时主机也无法发出START信号(START信号需要先主机拉低SDA,但此刻SDA正被从机拉低),故而也无法使SDA恢复,导致SDA总线挂死。此时现象为:

① SDA低电平

② SCK高电平

解决方案:

方案一:主机模拟SCK信号,同时探测SDA电平状态。假如SDA被释放,则发送STOP信号,结束本次通信。

方案二:连续模拟9个CLK信号。

情况二:SCL挂死

I2C从机主动拉低SCL线在规范中是一个合法的行为,称之为Clock Stretching(时钟扩展,我一般叫他时钟同步)。通常是主机请求数据( 收或者发)后从机需要一些时间处理,且没有多余Buffer可以接收接或者提供接下来的数据的时候从机则会拉低SCL一段时间直到有新的数据准备好。

SCL挂死(也就是前面所说一直拉低SCL)这种情况在标准I2C从器件上基本不会出现,因为只要芯片还在正常工作buffer总算有准备好的时候,自然就就释放SCL了。往往是使用用户使用MCU作为I2C从机时,程序设计上的问题导致MCU无法读取&填充buffer而导致,重点分析MCU I2C中断服务程序。

解决方案:从以下角度接入分析

① I2C中断服务程序被意外屏蔽

② 中断服务程序中陷入了一些标志位查询的while(flag != xxx)死循环

③ I2C功能系统被意外禁止

1323

1323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?