一、HLS简介

1.1 HLS简介

HLS(High Level Synthesis):一款高层次综合工具。

能够将C/C++或者 system C 等高级语言转化为RTL(底层硬件描述语言)电路,降低开发时间。

提供了常见的库(例如图像处理相关的 OpenCv 库和其

它的数学库)。

可以创建IP并通过例化或者使用 BlockDesign 的方式应用到项目中。

转化原理:在前端将 C 语言描述进行分析,然后进行代码层面的优化(code-level transformation),再在后端把这些运算工作进行并行调度(parallelise & schedule),最后生成 RTL 语言。

第一步 C/C++层面的仿真:

首先在源文件中,添加一个顶层函数,这个函数就是我们想要将来映射到 RTL 电路中的函数,之后需要一个 C Testbench 来对这个函数功能进行验证,在算法层面,检验我们的函数是否能够正常工作。(算法层面的仿真,能够很快地就得出结果,有助于提高我们的开发效率。)

第二步 对C 代码进行综合:

综合后会根据我们的功能函数,产生相应的电路。在 C 综合阶段,HLS 会根据我们对功能函数中的一些约束(Directive),来生成不同的接口。

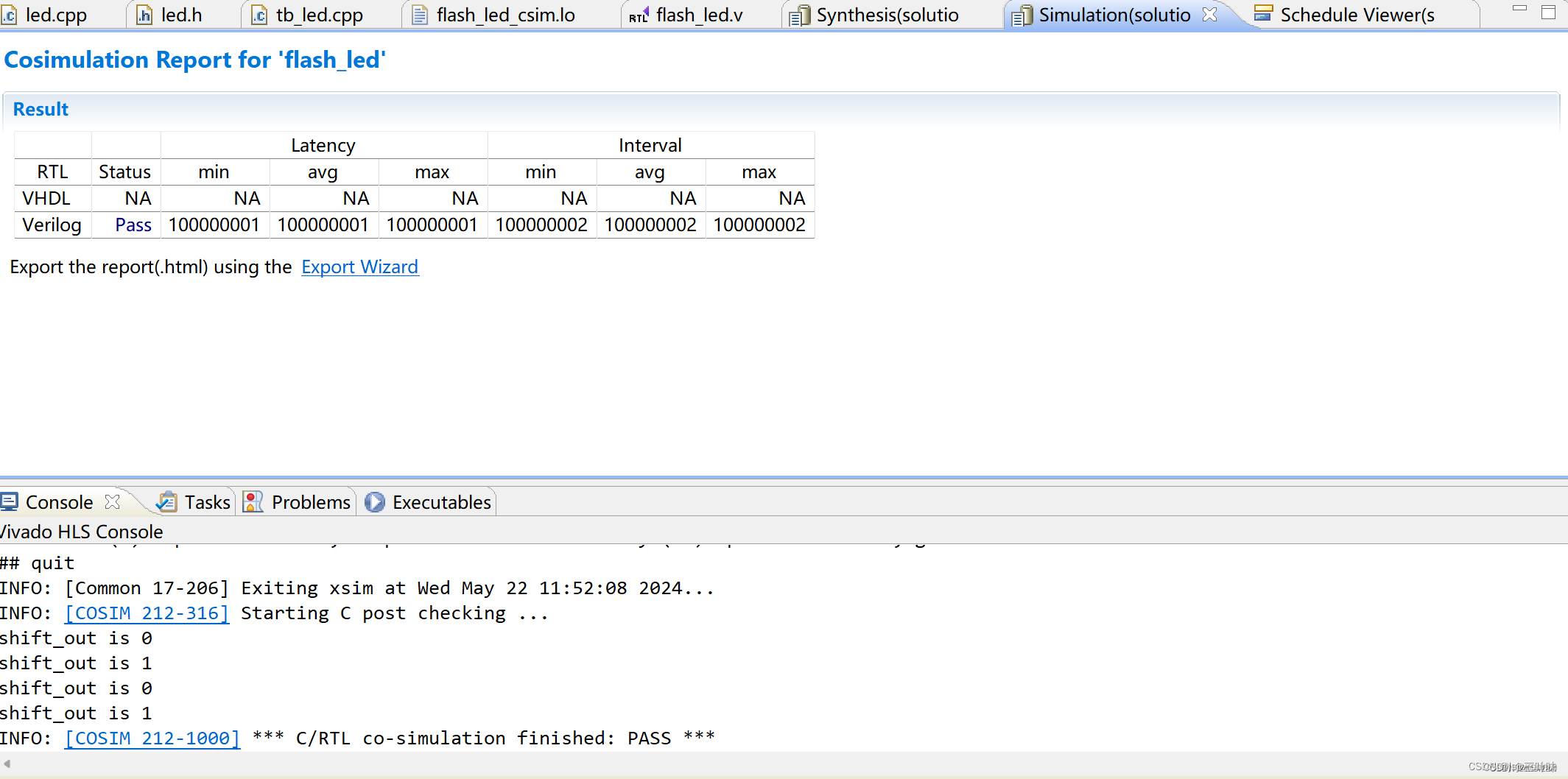

第三步 C/RTL 的联合仿真:

在这一阶段,HLS 会根据我们的 C Testbench 来生成我们的 RTL 的 Testbench 并且根据我们所选择的仿真工具来进行 RTL 级的仿真。仿真完成后我们可以观察联合仿真所产生的波形。

第四步 导出IP :

前面有提到过 HLS 相当于一个 IP 生成器,它能够将我们的高级语言的代码映射为一个 IP,我们可以根据需要将这些 IP 导出到 Vivado 的集成开发环境中,将这些算法的 IP 应用到实际的工程当中。

1.2 HLS与VHDL/Verilog

随着FPGA密度随着工艺几何尺寸的缩小而不断增长,设计复杂性使得继续使用传统的HDL设计流程变得越来越困难。尽管HDL语言和工具已经发展,但是设计周期仍然长得令人讨厌。为了帮助解决该问题,出现了高级综合(HLS)编译器,以使设计人员能够进入更高的抽象级别。

HLS能自动把 C/C++ 之类的高级语言转化成 Verilog/VHDL 之类的底层硬件描述语言(RTL),生成定制硬件在 FPGA 上跑实现加速。这使得不懂硬件的软件工程师也可以拥有玩转硬件的能力。

为了提高设计数字硬件组件的效率,高层综合(HLS)被视为提高设计抽象水平的下一步。但是,HLS工具的结果质量(QoR)往往落后于手动寄存器传输级别(RTL)流程的质量。

HLS 经过十数年的发展,虽然有诸如 AutoPilot、OpenCL SDK 等 FPGA HLS 商业化成功的案例出现,但距离其完全替代人工 RTL 建模还有很长的路要走。

1.3 HLS优点与局限

(1)优点

第一,使对于软件工程,实现算法基于硬件(ASIC或者FPGA)的计算加速。

第二,高层语言能促进 IP 重用的效率。

第三,HLS 能帮助软件和算法工程师参与、甚至主导芯片或 FPGA 设计。

第四、对于IC设计开发,从抽象的C层级进行功能设计。

第五、对于硬件验证,从更抽象的层次进行功能性验证,加速设计流程。

(2)局限

IP library 尚未全面还在不断升级,距离其完全替代人工 RTL 建模还有路要走。

没有早期的性能估计以及任何违反设计和平台限制的行为

没有利用所有可能的数据通信方式

没有功能概述,也没有对用户代码进行优化转换

支持代码报告得太晚了

在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。 HLS工具无法预先检测到这种情况,也无法在用户坚持的情况下尽量减轻其影响。

二、点亮LED仿真

2.1创建项目

①打开Vivado HLS,点击Create New Project

②输入相关工程信息

③选择顶层函数

④其他都点next,直到finish

2.2添加文件

①源文件添加

点击Source,右键后,选择New File,创建文件

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

②仿真测试文件添加

右键Test Bench,选择New File

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

2.3仿真与综合

①点击project->project settings->synthesis->browser->选择顶层函数

②点击project->Run C Simulation(输出01交替,表示C仿真结果正确)

③点击Solution->Run C Synthesis->Active Solution

生成的总结文件(Synthesis(solution1)(flash_led_csynth.rpt))里有端口表格

以及solution1\impl\verilog中,有已经生成好的.v文件

点击联合仿真:

总结

认识了HLS是什么,VHDL/Verilog编程技术有什么关系,Quantus的HLS进行了集成vivado的五个组件功能强大有待探索。

1150

1150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?