1.概述

中断控制器是ARMv7-M 异常模型的核心组成部分。该中断控制器的运行遵循 ARM 通用中断控制器(GIC)规范,该规范也适用于其他 ARMv7 架构配置和其他处理器架构。

ARMv7-M 的 NVIC(嵌套向量中断控制器)架构支持最多 496 个中断。所支持的外部中断线数可通过访问中断控制器类型寄存器(ICTR,Interrupt Controller Type Register,地址 0xE000E004)。

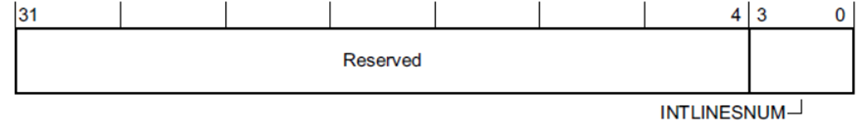

ICTR 中断控制器类型寄存器

- INTLINESNUM,位[3:0]:实现所支持的中断线总数,以 32个中断为粒度。即,中断线路总数为 32*(INTLINESNUM+1)。然而此时中断的绝对最大数量为 496,对应 INTLINESNUM 的二进制值 0b1111(即十进制 15)。

INTLINESNUM 用于确定 NVIC 寄存器映射中需要实现的寄存器范围。

- NVIC_ISERs、NVIC_ICERs、NVIC_ISPRs、NVIC_ICPRs 和 NVIC_IABRs:每个寄存器的每一位对应 32 个中断中的一个。

- NVIC_IPRs:每个寄存器包含 四组 8 位字段,每组对应一个中断

- 未实现的 NVI

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

982

982

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?