目录

SPI通信

(同步,全双工)

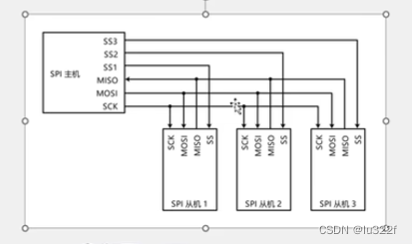

总线挂载多设备,一主多从。

通信线:

SCK(SCLK,CLK,CK):串行时钟线

MOSI(DI):主机输出,从机输入

MISO(DO):主机输入,从机输出

SS(NSS,CS):从机选择(指定与哪个从机通信)。主机与每个从机,都有一条单独的SS线

SS低电平:开启通信。SS低电平:关闭通信。

硬件电路:

所有设备的SCK、MOSI、MISO连接在一起。从机引出多条SS线,分别连接到各从机的SS引脚。

输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入。

注意:当从机的SS引脚为高电平,即从机未被选中时,它的MISO引脚必须切换为高阻态,防止MISO线产生电平冲突。

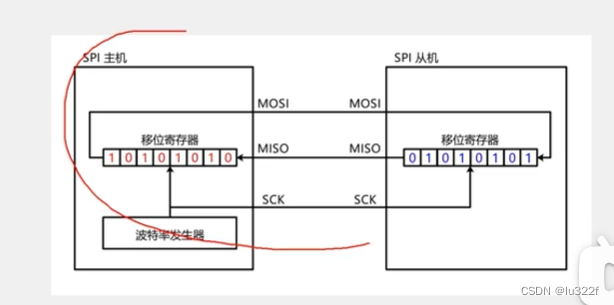

硬件过程:

每来一个时钟沿,移位寄存器都会向左移位(高位先行),从机也是如此。主机左边移出去的数据,通过MOSI引脚,输入到从机移位寄存器的右边。从机左边移位寄存器移出去的数据,通过MISO引脚,输入到主机移位寄存器的右边。

每一个时钟:

上升沿:主机最左边的1输出到MOSI线上,从机最左边的0输出到MISO线上。

下降沿:MOSI线上的1输入到从机最右边,MISO线上的0输入到主机最右边。循环往复~

时序:

起始条件:

SS从高电平变成低电平

终止条件:

SS从低电平变成高电平

交换一个字节:

(CPOL和CPHA的值可以配置,有00,01,10,11四种模式)

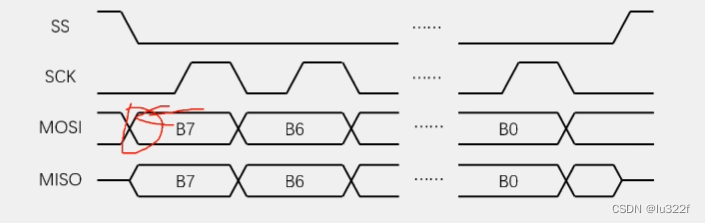

模式00(使用最多,重点掌握):

CPOL = 0:空闲状态时,SCK为低电平

CPHA = 0:SCK第一个时钟边沿(下降沿)移入数据,第二个时钟边沿(上升沿)移出数据。

SS为高电平时,MISO为高阻态。

需要注意的是:当SCK第一个时钟边沿到达之前,就要移出数据。因为SCK时钟沿一到,就要开始移入数据,要先移出到线上,才能移入。所以把SS的下降沿也当做一个信号,检测到SS下降沿时,立马开始移出数据。当SCK上升沿到来时,开始输入数据。

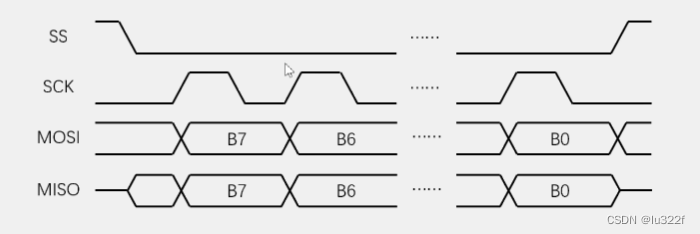

模式01:

CPOL = 0:空闲状态时,SCK为低电平

CPHA(时钟相位) = 1:SCK第一个时钟边沿(下降沿)移出数据,第二个时钟边沿(上升沿)移入数据。

SS为高电平时,MISO为高阻态。

5988

5988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?