上一章中我们学习了read和write相关的时序,在真正的系统中我们想要读或者写正确的数据离不开初始化时Data trainin这一步,今天我们来了解下dram在初始化时重要的一环write leveling的训练。

write leveling的目的

在ddr3及以后的ddr系列中我们一般会采用fly-by的布线方式来设计soc和dram之间的通信。

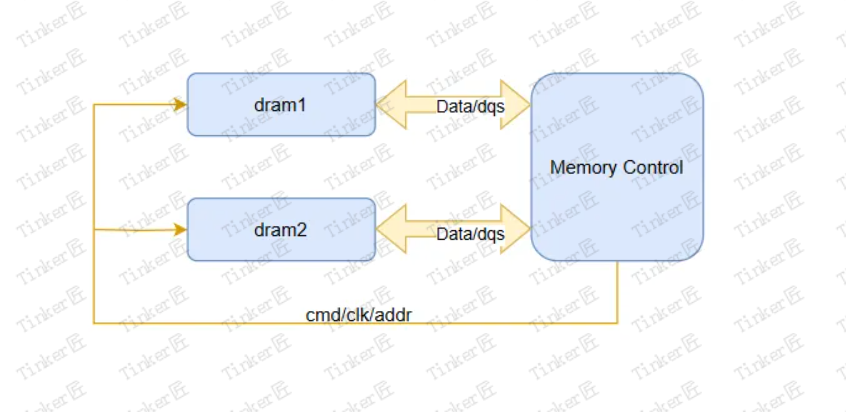

如图1所示,这是一个简单的fly-by的布线图,从图中我们可以看到,这种布线方式是把命令,地址和时钟这些共用信号线依次连接dram1,dram2。但是这样连接会有一个显而易见的问题就是dq/dqs线与clk线的长度不一样。如果信号同时发出的话很显然clk会晚于dqs到达dram中,这就会导致同步出错进而导致数据错误。所以write leveling就是给dqs加延时让它和clk同时能到达dram中

write leveling的步骤

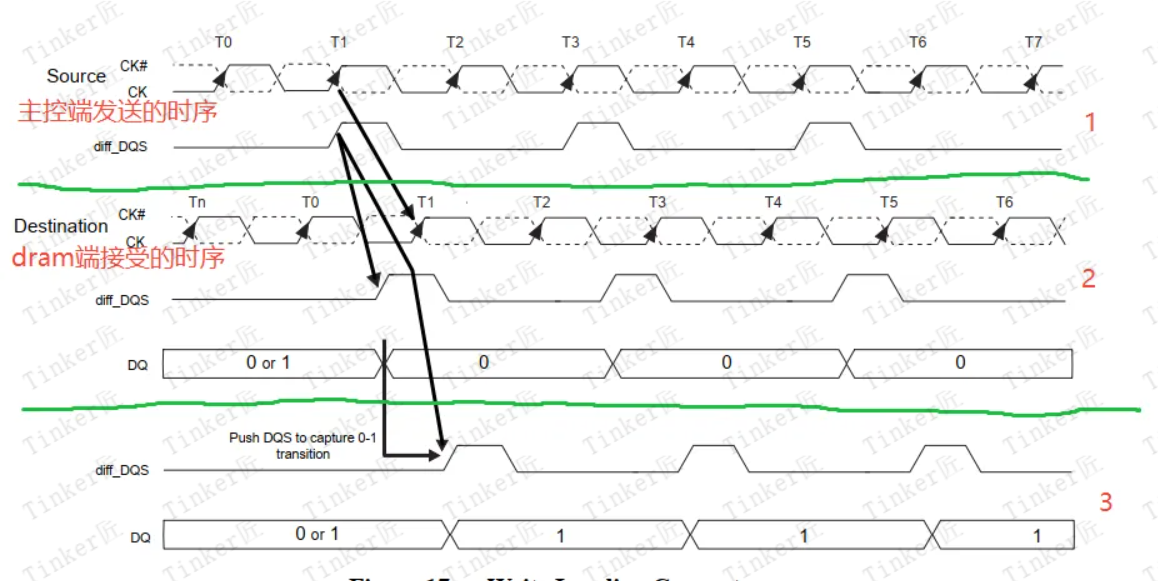

如图2中所示,主控端发送的时序我们称source,dram端接收的时序称为destination端,第一阶段source中的clk信号和dqs信号同时在T1时间起点发出。在第二阶段到达dram端时我们发现clk信号T1时间起点是晚于dqs到达的所以dram在采集clk信号时是返回0,原因就是我们上面讲的clk的布线一般要比数据线更长。所以我们需要延时发出dqs信号直至它达到第三阶段在dqs的上升沿检测到clk信号是高电平,此时dram返回给主控端的信号为1,表示training完成。

简化总结下这个流程就是

T1: 使能ODT,主控端发送DQ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

774

774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?