DDR3的FLY-BY拓扑结构带来了时钟信号和数据/数据选通信号之间的flighttime偏斜,这是FPGA与DDR3 SDRAM实现接口互连必须解决的问题。为此,DDR3采用Write Leveling的技术来调整各SDRAM芯片的数据选通信号相位,保证其和时钟信号在接收端同步;而更可靠易实现的Write Leveling技术实现方案能够更好地应对采样时信号完整性不好的情形,从而让DDR3能够跑到更高的频率。

DDR3中的命令、地址和时钟信号线采用了FLY-BY拓扑,造成了它们与数据选通(DQS)信号之间的flight time偏斜,Write Leveling作为Leveling技术的核心部分是解决这一问题的关键所在。下面针对FLY-BY拓扑结构带来的影响,着重分析Write Leveling的工作机制。

DDR3的FLY-BY拓扑结构

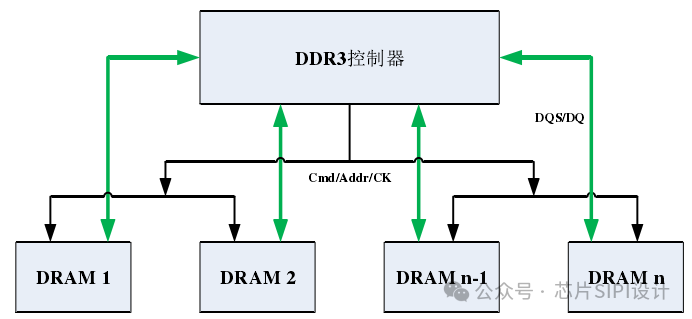

由第二章介绍的DDR3 SDRAM内存特性可知,DDR3具有较高的信号传输速率,模组集成更多SDRAM模块。如果还继续采用下图给出的DDR2的T型拓扑结构,就会出现多个stub(抽头)而且也会增加容性负载,带来并发开关噪声(SNN),造成信号完整性问题,这样将无法可靠地支持更高的频率。

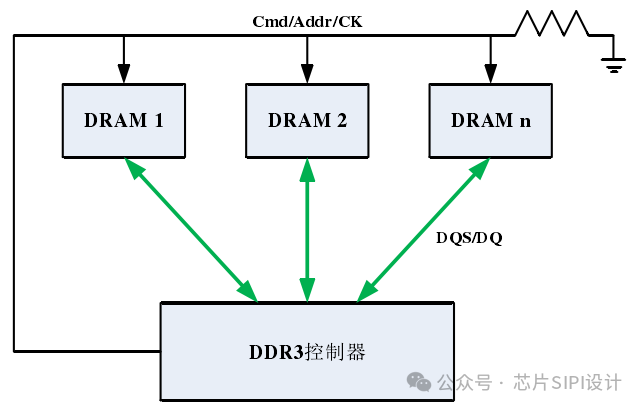

为解决上述问题而获得更好的信号完整性,DDR3内存采用了下图给出的FLY-BY拓扑结构,以菊花链的方式来布线将DDR3控制器和SDRAM模块连接在一起。这种结构有利于减少抽头的数量及其长度,其中的各个SDRAM模块共享命令、地址、控制和时钟信号线,它们以串联的方式连接在一起,并在末端配备合适的电阻。在FLY-BY拓扑结构中,信号会在不同的间隔时间内到达不同的SDRAM模块,这样就延迟了遭遇SDRAM模块输入容性负载的时间,如此通过容性负载的减少,DDR3可以在不影响数据速率的同时获得更好的信号完整性。因此,FLY-BY拓扑结构能够支持更高的信号传输速率,获得更高的性能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1383

1383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?