Zynq FPGA实验报告

DDS IP 数字波形合成

1.使用 Vivado的IPI工具,例化DDS IP

在IP INTERGRATOR下点击Create Block Design,Diagram下点击+添加一个DDS Compiler。

2.DDS需要能够配置频率字(相位增量)

双击DDS Compiler。

Implementation——Phase Increment Programmability——Programmable

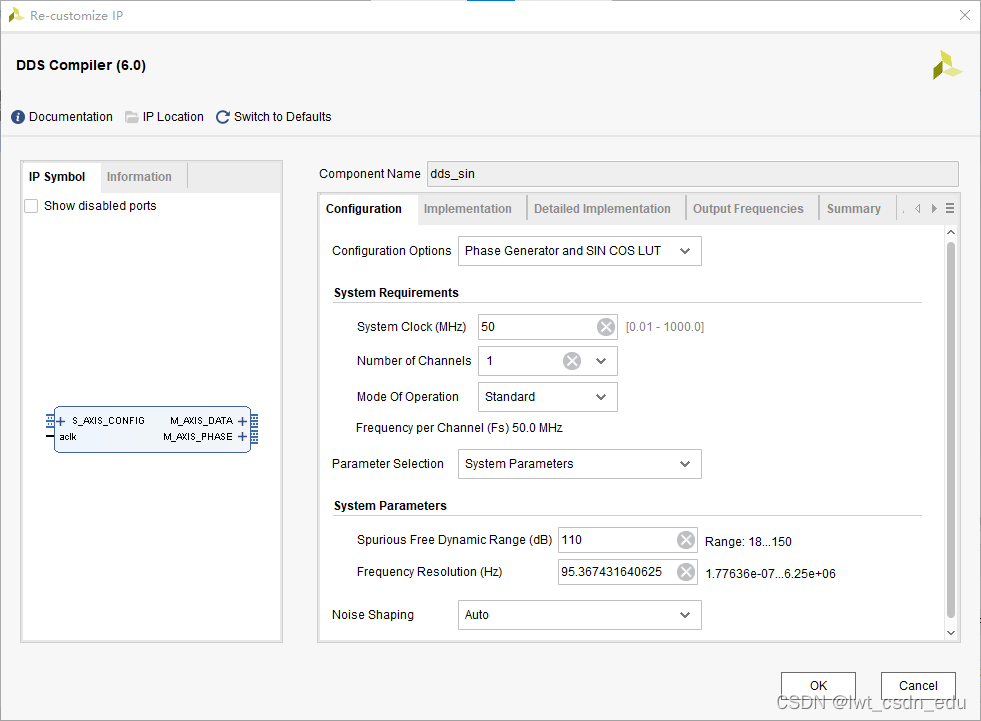

3.DDS工作时钟使用PL的板载50MHz时钟

Configuration——System Requirements——System Clock(MHz) 50

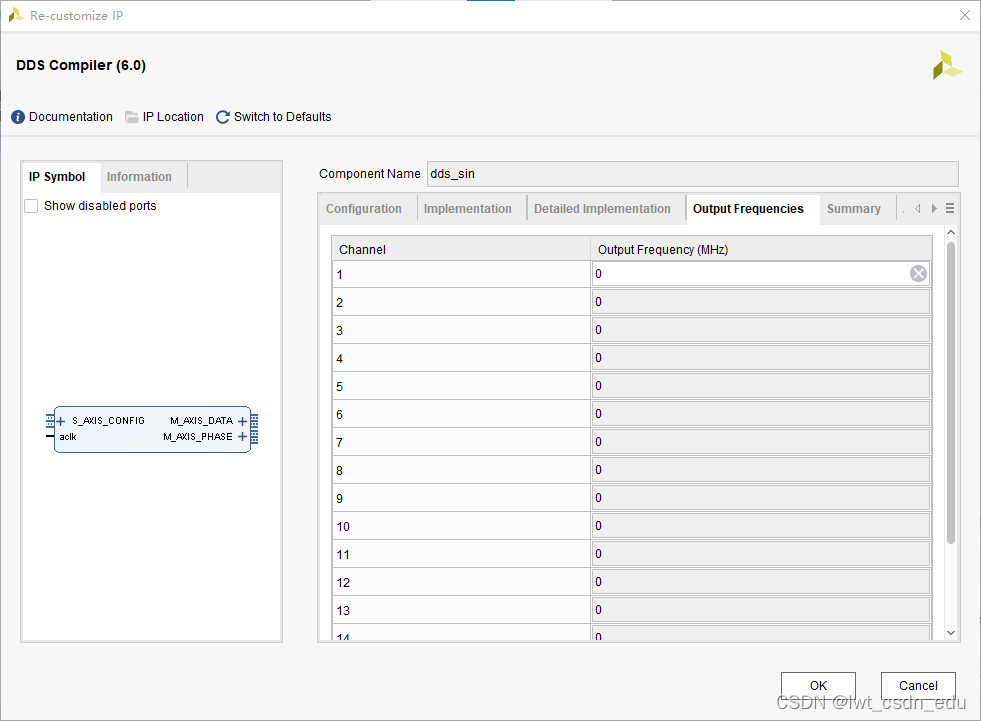

DDS的输出频率。

右键引脚Create Port连接。

右键Sources下DDS_IP,点击Create HDL Wrapper。

Add Sources创建一个.v文件存放相应代码。

`timescale 1ns / 1ps

module top(

input sys_clk ,//系统时钟 50MHz T=20ns

input rst_n //系统复位

);

// -----------0、VIO按键控制频率控制字(key_PINC)

wire [1:0] key_PINC;

vio_0 vio_0_inst (

.clk(sys_clk), // input wire clk

.probe_out0(key_PINC) // output wire [1 : 0] probe_out0

);

//---------------1、信号频率控制模块--------------//

wire [23:0] Fword ; //频率字

Fword_set Fword_set_inst(

//input

.clk (sys_clk ),

.rst_n (rst_n ),

.key_PINC (key_PINC ),

//output

.Fword (Fword )

);

//---------------2、DDS模块--------------//

//input

wire [0:0] fre_ctrl_word_en ;

//output

wire [0:0] m_axis_data_tvalid ;

wire [47:0] m_axis_data_tdata ;

wire [0:0] m_axis_phase_tvalid ;

wire [23:0] m_axis_phase_tdata ;

assign fre_ctrl_word_en=1'b1;

//例化DDS IP

dds_sin dds_sin_inst (

.aclk (sys_clk ), // input wire aclk

.s_axis_config_tvalid (fre_ctrl_word_en ), // input wire s_axis_config_tvalid

.s_axis_config_tdata (Fword ), // input wire [23: 0] s_axis_config_tdata

.m_axis_data_tvalid (m_axis_data_tvalid ), // output wire m_axis_data_tvalid

.m_axis_data_tdata (m_axis_data_tdata ), // output wire [47 : 0] m_axis_data_tdata

.m_axis_phase_tvalid (m_axis_phase_tvalid ), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata (m_axis_phase_tdata ) // output wire [23 : 0] m_axis_phase_tdata

);

ila_1 ila_1_inst (

.clk(sys_clk), // input wire clk

.probe0(key_PINC), // input wire [1:0] probe0

.probe1(Fword), // input wire [23:0] probe1

.probe2(m_axis_data_tdata) // input wire [47:0] probe2

);

endmodule

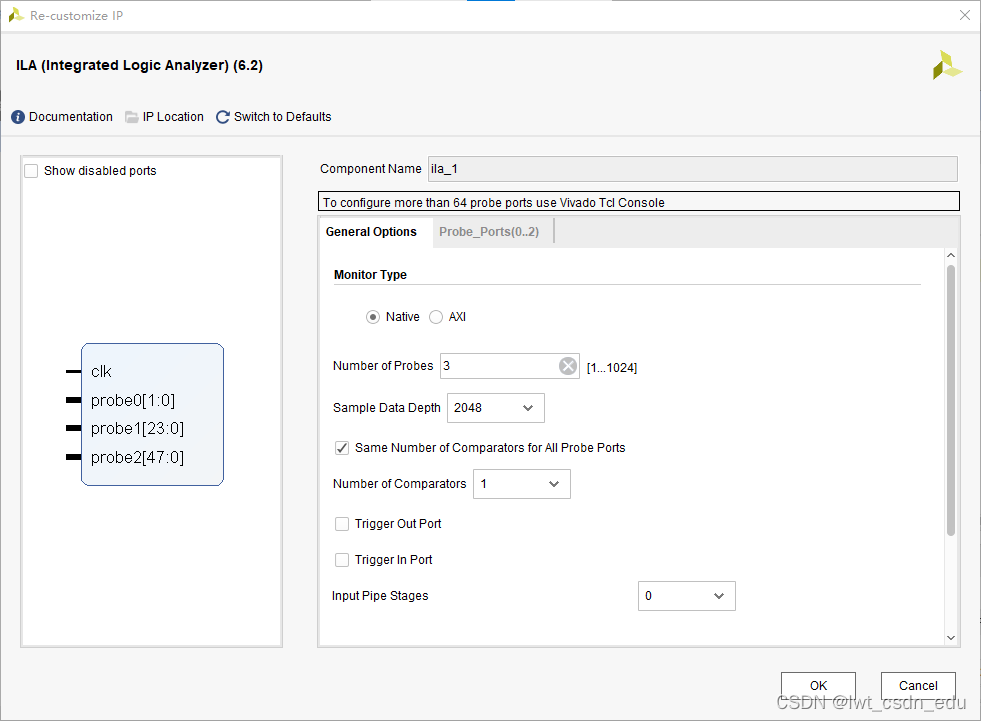

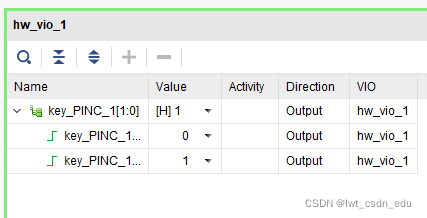

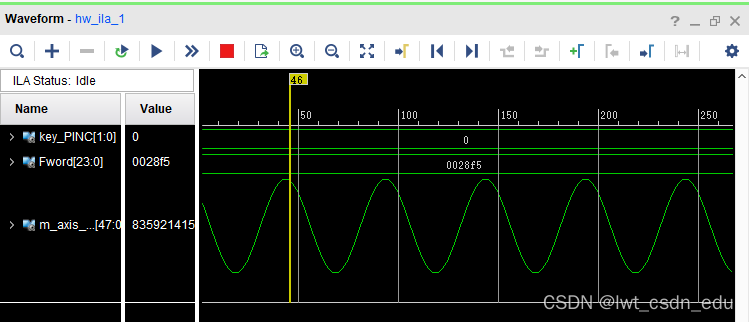

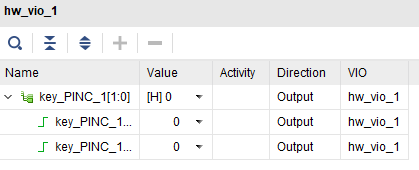

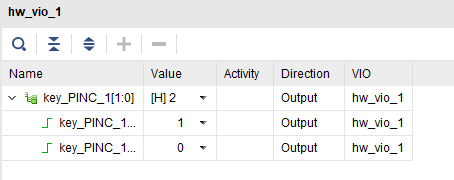

4.使用ILA工具观察波形, 使用VIO设定频率字

点击IP Catalog,搜索ila,选择双击。

配置完ILA核后,在vivado工程的IP Sources中找到刚刚生成的ILA核的例化代码。

将例化代码拷贝到所设计的RTL中。

ila_1 ila_1_inst (

.clk(sys_clk), // input wire clk

.probe0(key_PINC), // input wire [1:0] probe0

.probe1(Fword), // input wire [23:0] probe1

.probe2(m_axis_data_tdata) // input wire [47:0] probe2

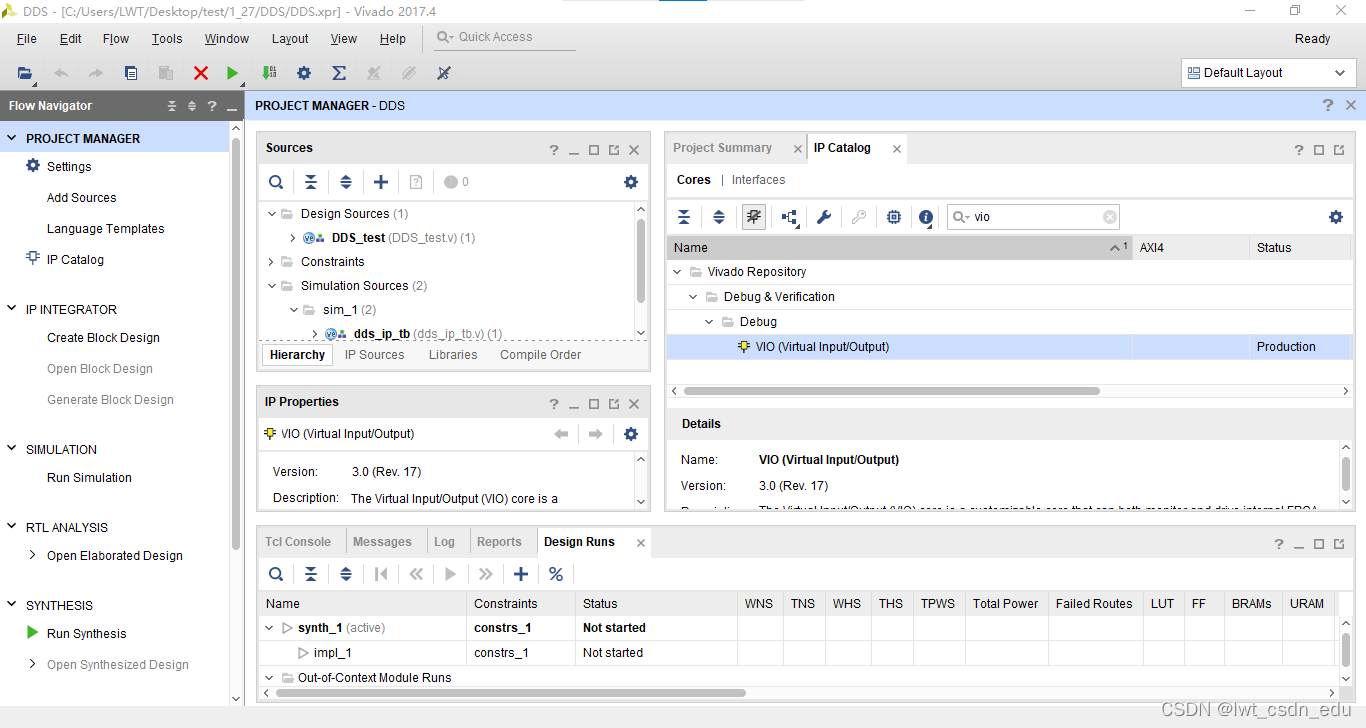

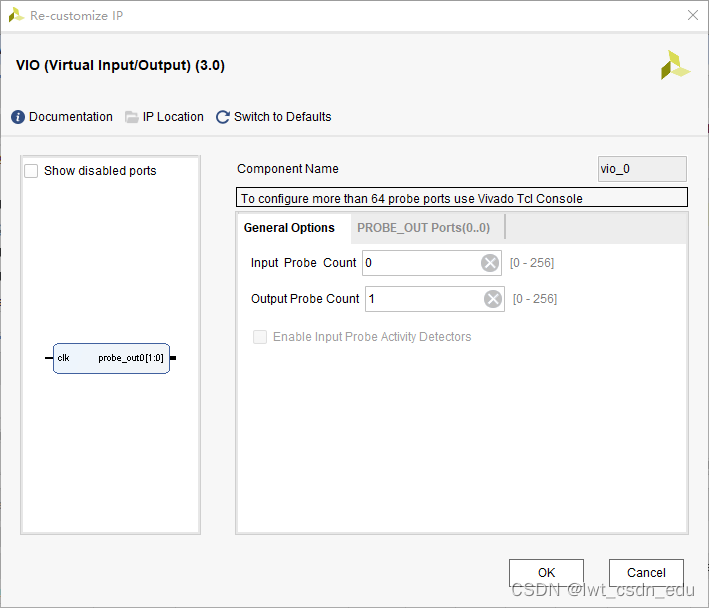

点击IP Catalog,搜索vio,选择双击。

将例化代码拷贝到所设计的RTL中。

vio_0 vio_0_inst (

.clk(sys_clk), // input wire clk

.probe_out0(key_PINC) // output wire [1 : 0] probe_out0

);

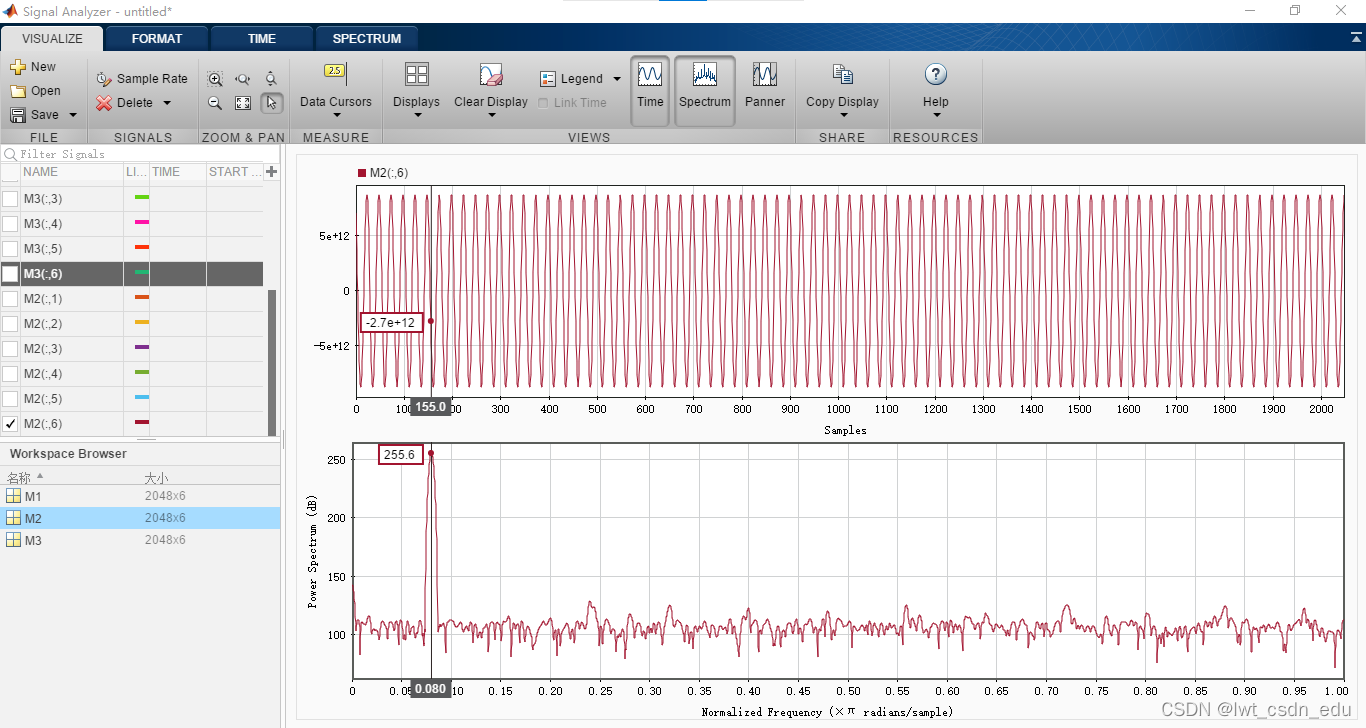

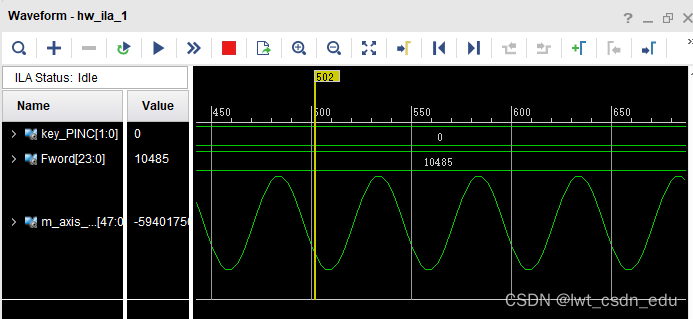

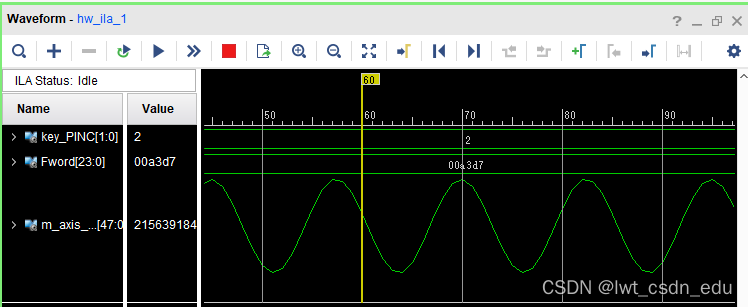

5.在ILA的波形窗口里,观察你设定的波形的周期,验证你频率字设定的正确性

修改完RTL后,生成比特流文件。PROGRAM AND DEBUG—Generate Bitstream。

key_PINC=1(2’b01)

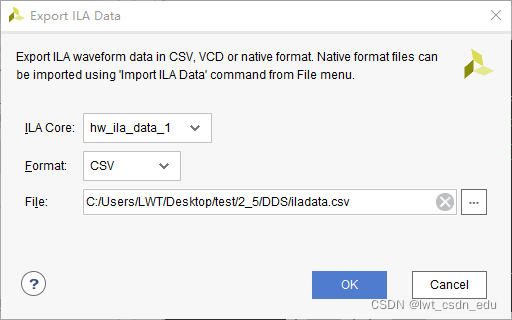

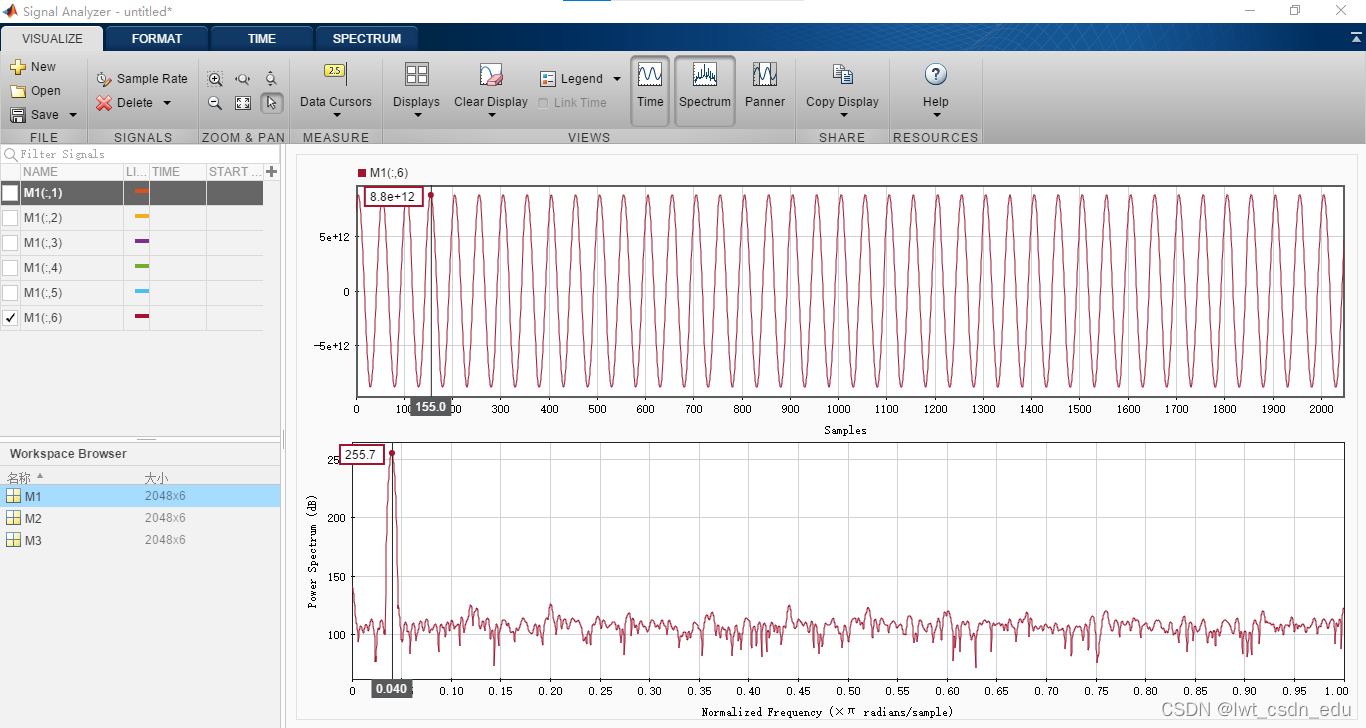

6.把ILA波形导出到CSV文件,波形样点长度不小于2048点,在Matlab里分析波形的频谱,验证你生成波形的正确性。

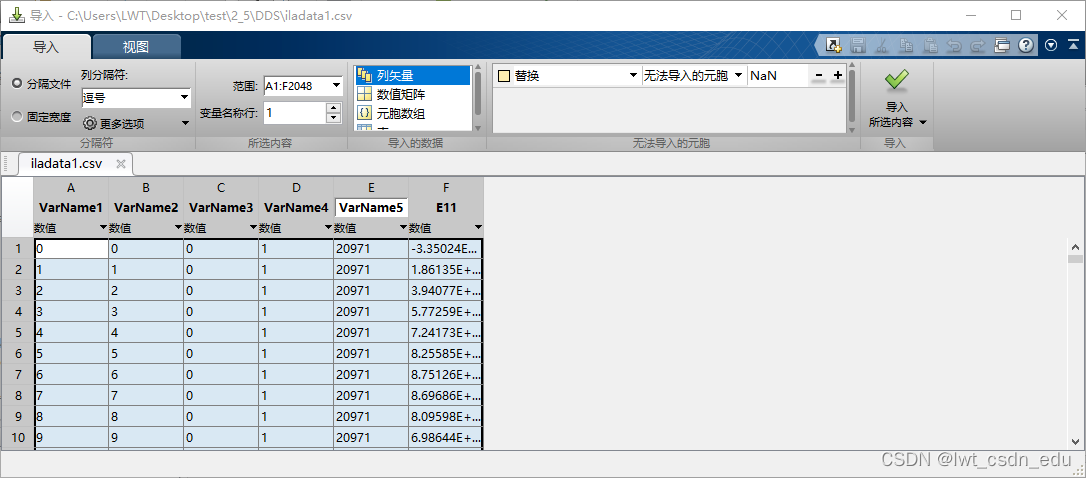

选中要分析的信号,右键Export ILA Data,Format选择CSV,导入到指定目录中。

Matlab中读出csv文件。

M = csvread(filename);

fprintf('%d\n',length(M));

N = length(M); %样点个数

filename1 = 'C:\Users\LWT\Desktop\test\2_5\DDS\iladata_1MHz.csv';

filename2 = 'C:\Users\LWT\Desktop\test\2_5\DDS\iladata_2MHz.csv';

filename3 = 'C:\Users\LWT\Desktop\test\2_5\DDS\iladata_3MHz.csv';

M1 = csvread(filename1,1,0); %1,0代表从该文件的第1行第0列开始读数直到文件末,因为上图中CSV文件的第0行为各列的名称,类型不是数据,因此无法读取,故从第1行开始读取数据

M2 = csvread(filename2,1,0);

M3 = csvread(filename3,1,0);

csv1_row6 = iladata1MHz{:,6}; %iladata_1MHz.csv文件中的第六列数据

csv2_row6 = iladata2MHz{:,6}; %iladata_2MHz.csv文件中的第六列数据

csv3_row6 = iladata3MHz{:,6}; %iladata_3MHz.csv文件中的第六列数据

fs=50000000; %设置采样频率为50MHz

N=2048; %采样点

n=0:N-1;

t=n/fs;

f=n*fs/N; %频率序列

figure;

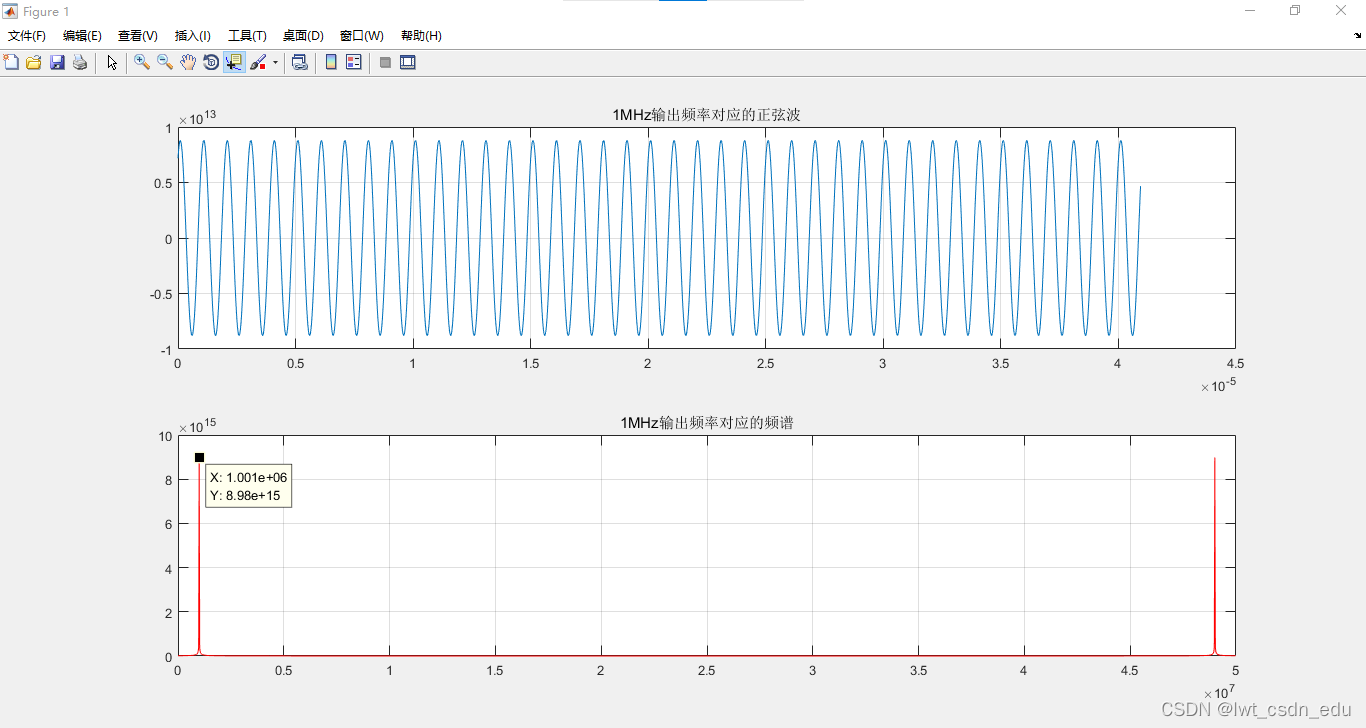

subplot(2,1,1);plot(t,csv1_row6);grid on;title('1MHz输出频率对应的正弦波');

y1=abs(fft(csv1_row6,N));

subplot(2,1,2);plot(f,y1,'r');grid on;title('1MHz输出频率对应的频谱');

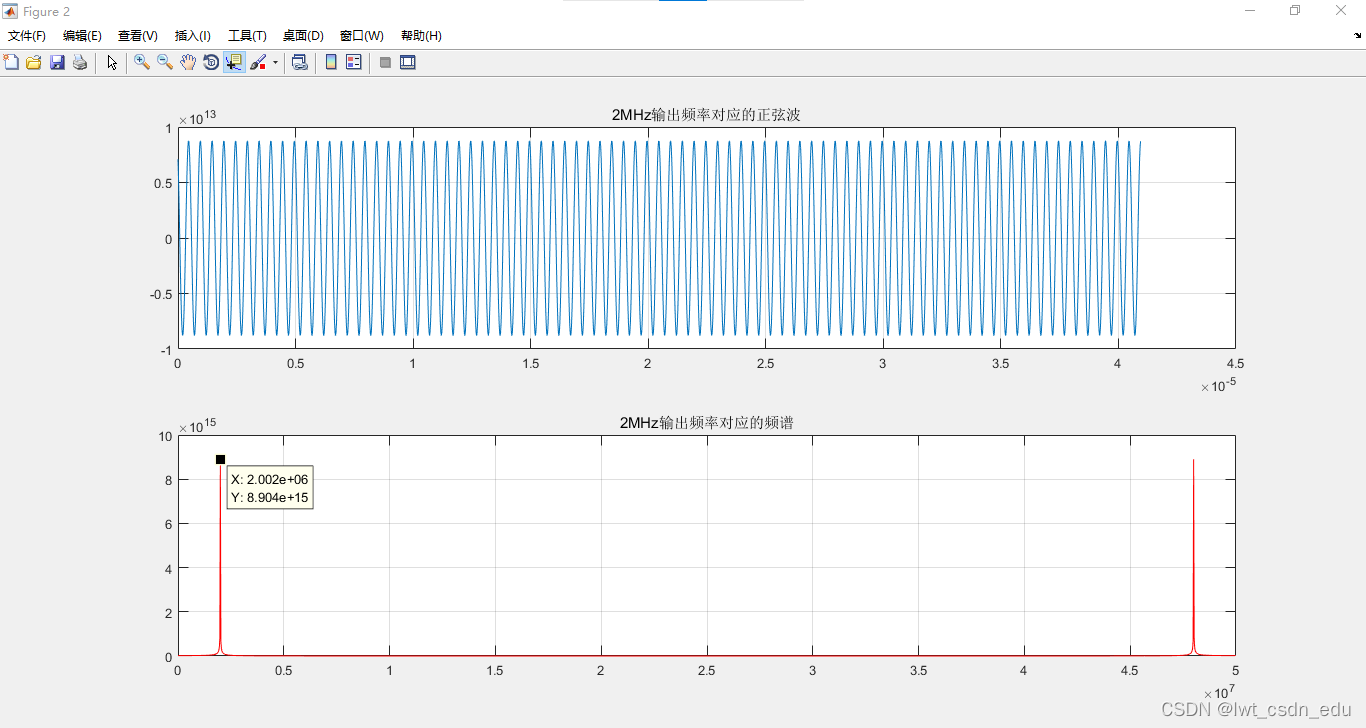

figure;

subplot(2,1,1);plot(t,csv2_row6);grid on;title('2MHz输出频率对应的正弦波');

y2=abs(fft(csv2_row6,N));

subplot(2,1,2);plot(f,y2,'r');grid on;title('2MHz输出频率对应的频谱');

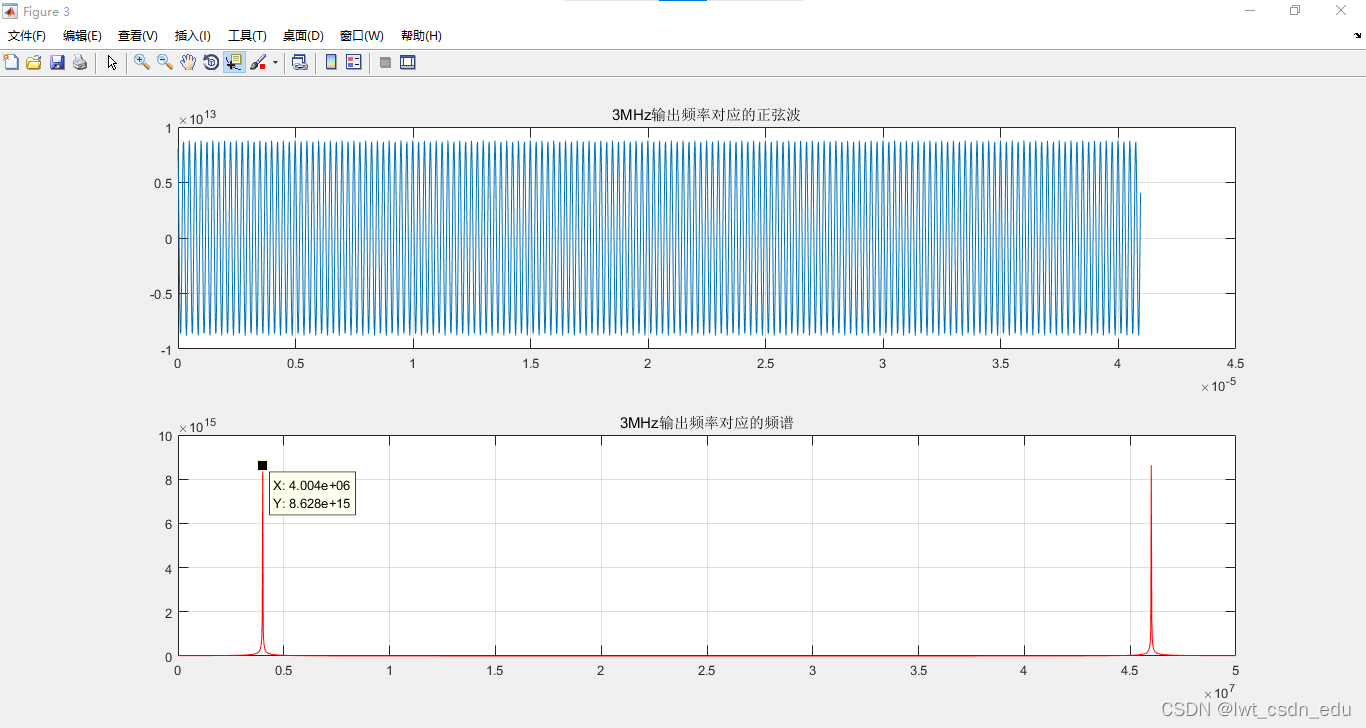

figure;

subplot(2,1,1);plot(t,csv3_row6);grid on;title('3MHz输出频率对应的正弦波');

y3=abs(fft(csv3_row6,N));

subplot(2,1,2);plot(f,y3,'r');grid on;title('3MHz输出频率对应的频谱');

7.使用VIO更改频率字,分别生成1MHz和3MHz的正弦波形。使用以上流程,验证你输出波形的正确性。

1MHz正弦波:

key_PINC=0(2’b00)

把ILA波形导出到csv文件。在Matlab中进行分析。

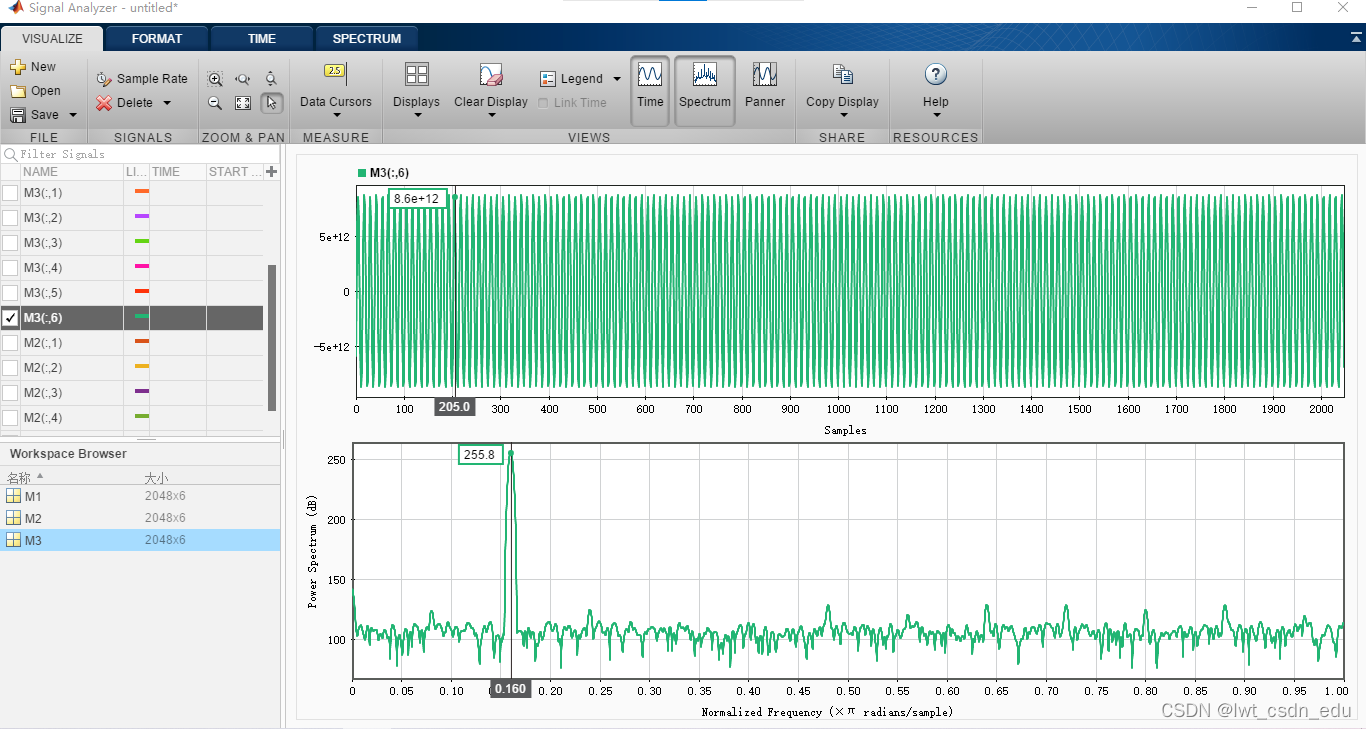

3MHz正弦波:

key_PINC=2(2’b10)

把ILA波形导出到csv文件。在Matlab中进行分析。

本文档详细介绍了如何在Zynq FPGA平台上使用Vivado的IPI工具例化DDSIP,配置相位增量生成不同频率的正弦波。通过ILA工具观察和分析波形,并在Matlab中验证了DDSIP的正确性,生成了1MHz和3MHz的正弦波。

本文档详细介绍了如何在Zynq FPGA平台上使用Vivado的IPI工具例化DDSIP,配置相位增量生成不同频率的正弦波。通过ILA工具观察和分析波形,并在Matlab中验证了DDSIP的正确性,生成了1MHz和3MHz的正弦波。

1665

1665