状态机实现的一个典型实例。

一、问题基本描述

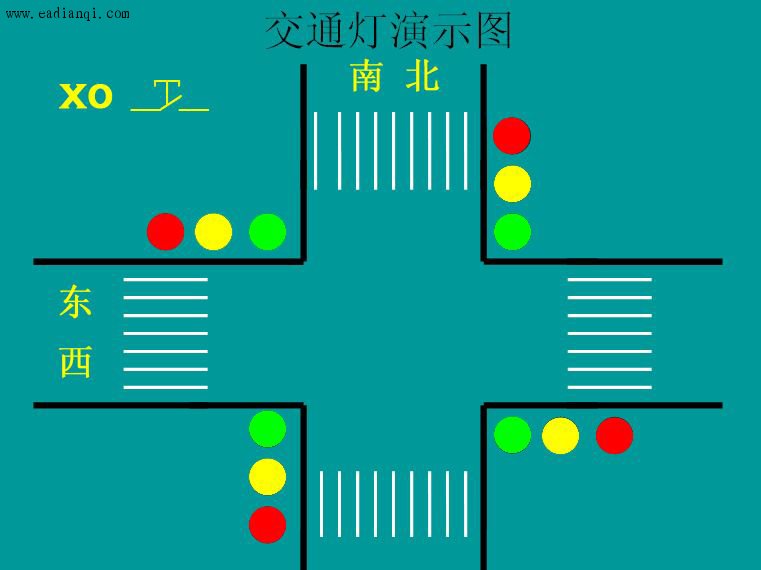

输出六路信号,分别控制南北向和东西向的红、黄、绿灯。

WE_RED,WE_YELLOW,WE_GREEN 东西向的红、黄、绿灯信号线

NS_RED, NS_YELLOW, NW_GREEN 南北向的红、黄、绿灯信号线

控制时间暂定为: 正常行驶时间60s,黄灯等待时间3s。

二、VHDL代码:

library ieee;

use ieee.std_logic_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity jiaotongdeng is

port(

clk : in std_logic;

reset : in std_logic;

f1,f2 : out std_logic;

WE_RED,WE_YELLOW,WE_GREEN : out std_logic;

NS_RED,NS_YELLOW,NW_GREEN : out std_logic

);

end entity;

architecture rtl of jiaotongdeng is

begin

process (current_state)

begin

case current_state is

when s0=>

if flag1='1' then

next_state <= s1;

else

next_state<=s0;

end if;

when s1=>

if flag2='1' then

next_state <= s2;

else

next_state<=s1;

end if;

when s2=>

if flag1='1' then

next_state <= s3;

else

next_state<=s2;

end if;

when s3=>

if flag2='1' then

next_state <= s0;

else

next_state<=s3;

end if;

when others=>

next_state <= s0;

end case;

end process;

process (current_state)

begin

case current_state is

when s0 =>

WE_RED<='1';WE_YELLOW<='0';WE_GREEN<='0';

NS_RED<='0';NS_YELLOW<='0';NW_GREEN<='1';

when s1 =>

WE_RED<='1';WE_YELLOW<='0';WE_GREEN<='0';

NS_RED<='0';NS_YELLOW<='1';NW_GREEN<='0';

when s2 =>

WE_RED<='0';WE_YELLOW<='0';WE_GREEN<='1';

NS_RED<='1';NS_YELLOW<='0';NW_GREEN<='0';

when s3 =>

WE_RED<='0';WE_YELLOW<='1';WE_GREEN<='0';

NS_RED<='1';NS_YELLOW<='0';NW_GREEN<='0';

end case;

end process;

-- sequnce process

process (clk)

variable cn: integer;

begin

if (rising_edge(clk)) then

current_state<=next_state;

end if;

--counter

if (rising_edge(clk)) then

if cn>0 then

cn:=cn-1;

ELSE cn:= 62;

end if;

if (cn<=62 and cn>=3) then

flag1<='1';

else flag1<='0';

end if;

if (cn<3 and cn>=0) then

flag2<='1';

else flag2<='0';

end if;

end if;

end process;

f1<=flag1;

f2<=flag2;

end rtl;

1491

1491

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?